JAJSGJ4D August 2018 – April 2021 UCC21530-Q1

PRODUCTION DATA

9.2.2.7 他のアプリケーション回路の例

理想的でない PCB レイアウトと長いパッケージ・リード (TO-220 および TO-247 タイプのパッケージなど) によって寄生インダクタンスが付くと、高 di/dt および dv/dt スイッチング中、パワー・トランジスタのゲート - ソース間駆動電圧にリンギングが生じる可能性があります。リンギングがスレッショルド電圧を上回る場合、予期しないターンオンのリスクがあり、貫通電流のリスクさえあります。ゲート駆動に負のバイアスを印加することは、このようなリンギングをスレッショルドよりも低く保つための一般的な方法です。負のゲート駆動バイアスの実装方法の例をいくつか以下に示します。

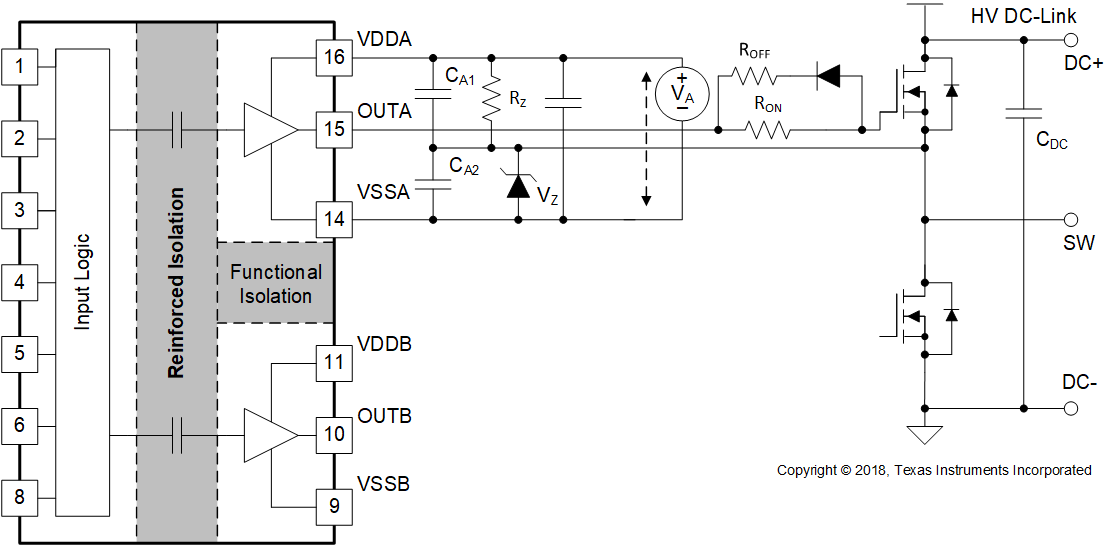

正および負の駆動電圧を生成するために2つの独立した電力を使用する代わりに、絶縁型電源の出力段でツェナー・ダイオードを使用してチャネル A のドライバを負バイアスでオフにする例を、図 9-2 に示します。この負バイアスはツェナー・ダイオード電圧によって設定されます。絶縁型電源 VA の電圧が 19V の場合、ターンオフ電圧は -3.9V、ターンオン電圧は 19V - 3.9V ≈ 15V です。チャネル B のドライバ回路は、チャネル A と同じです。そのため、この構成ではドライバの各チャネルについて 1 つの電源しか必要とせず、RZ によって定常的に電力が消費されます。

図 9-2 絶縁型バイアス電源の出力に接続したツェナー・ダイオードによる負バイアス印加

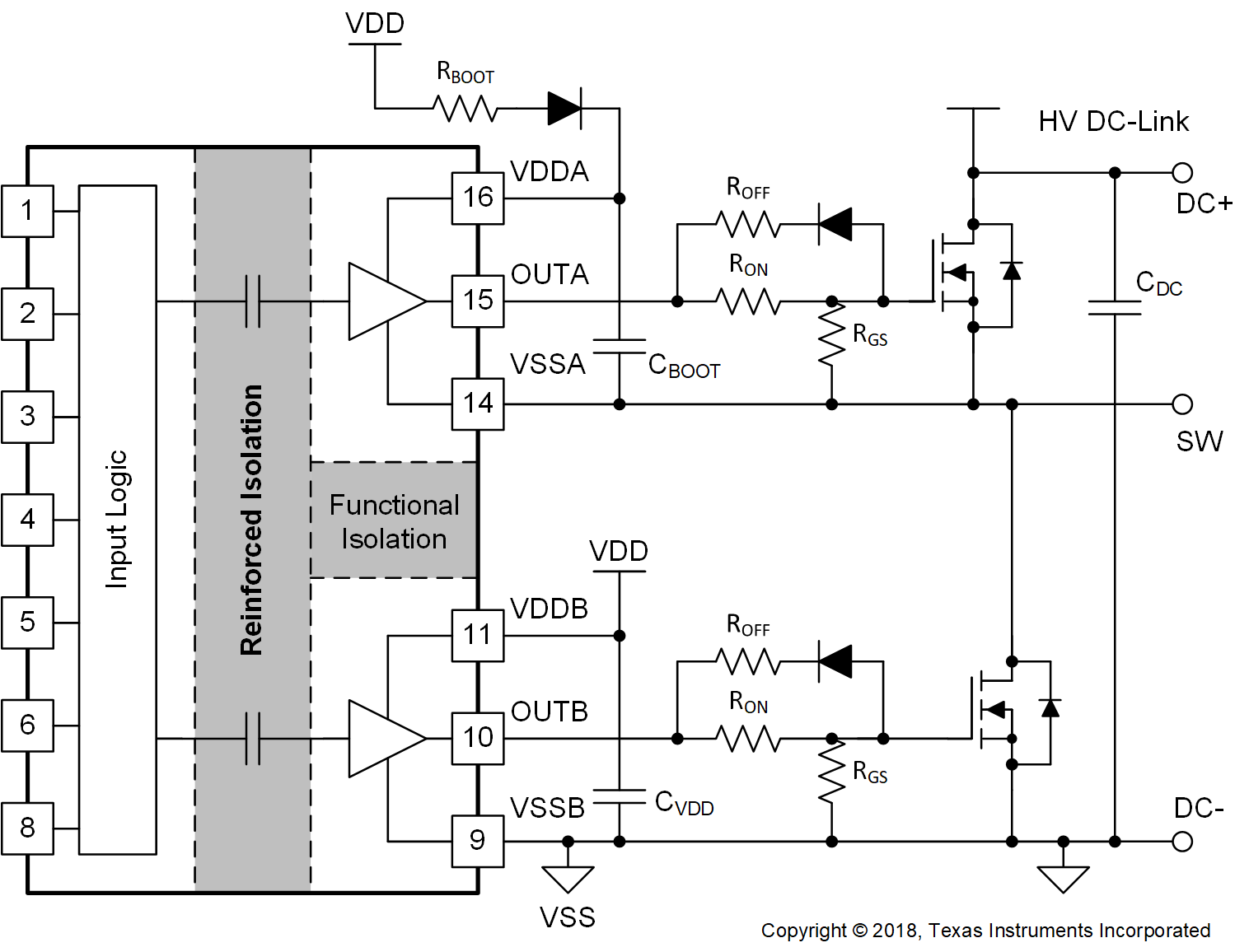

図 9-2 絶縁型バイアス電源の出力に接続したツェナー・ダイオードによる負バイアス印加ブートストラップを使用してチャネル A に電力を供給する別の例を、図 9-3 に示します。このソリューションには負のレール電圧がないため、リンギングが少ない回路や、スレッショルド電圧が高い電源デバイスにのみ適しています。

図 9-3 ハイサイド・デバイス用のブートストラップ電源

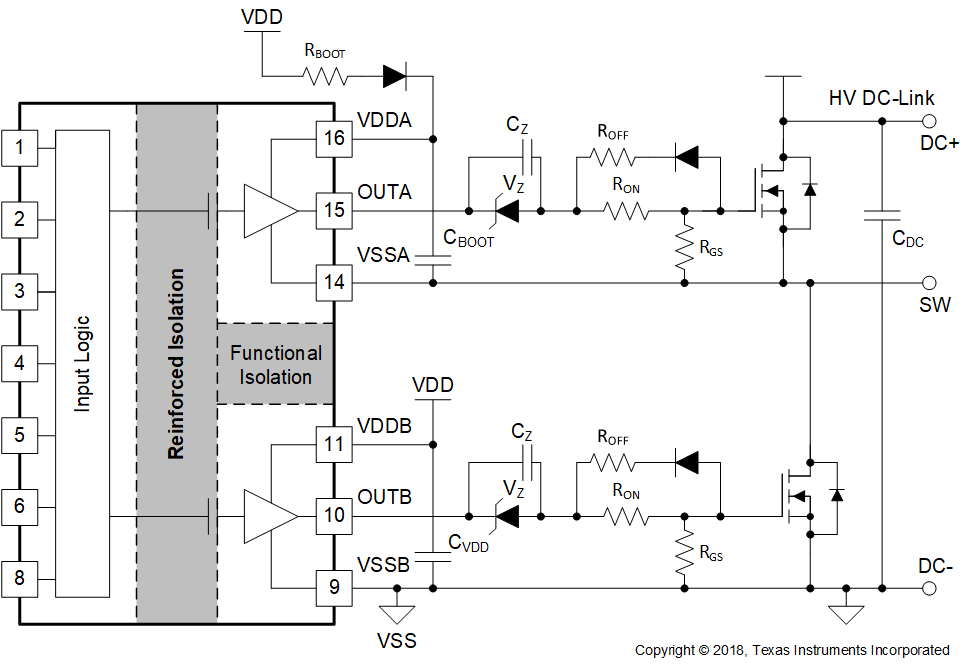

図 9-3 ハイサイド・デバイス用のブートストラップ電源図 9-4 に示す最後の例は単一電源構成で、ゲート・ドライブ・ループ内のツェナー・ダイオードによって負バイアスを生成しています。この方法の利点は、1 つの電源のみを使い、ブートストラップ電源をハイサイド駆動に使えることです。この設計は、3 つの方法のうちでコストと設計工数が最も少なくて済みます。しかし、この方法には以下の制約があります。

- 負のゲート駆動バイアスはツェナー・ダイオードのみによって決まるのではなく、デューティ・サイクルによっても影響されます。これは、デューティ・サイクルが変化すると負バイアス電圧が変化することを意味しています。そのため、固定デューティ・サイクル (約 50%) のコンバータ (例:可変周波数共振コンバータ、位相シフト・コンバータ) がこの方法に適しています。

- 推奨電源電圧範囲を維持するには、ハイサイド VDDA-VSSA として十分な電圧を維持する必要があります。これは、ブートストラップ・コンデンサをリフレッシュするために、各スイッチング・サイクルの間、ローサイド・スイッチをターンオンさせ、またはボディ・ダイオード (または逆並列ダイオード) にフリーホイール電流を流す必要があることを意味します。そのため、他の 2 つの回路例と同様のハイサイド専用電源を使わない限り、ハイサイドを 100% デューティ・サイクルにすることはできません。

図 9-4 1 つの電源とゲート駆動経路内のツェナー・ダイオードによる負バイアス印加

図 9-4 1 つの電源とゲート駆動経路内のツェナー・ダイオードによる負バイアス印加