JAJSFV7C September 2016 – March 2020 UCD90160A

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要 (続き)

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4

Device Functional Modes

- 8.4.1 Power Supply Sequencing

- 8.4.2 Pin-Selected Rail States

- 8.4.3 Voltage Monitoring

- 8.4.4 Fault Responses and Alert Processing

- 8.4.5 Shut Down All Rails and Sequence On (Resequence)

- 8.4.6 GPIOs

- 8.4.7 GPO Control

- 8.4.8 GPO Dependencies

- 8.4.9 GPI Special Functions

- 8.4.10 Power Supply Enables

- 8.4.11 Cascading Multiple Devices

- 8.4.12 PWM Outputs

- 8.4.13 Programmable Multiphase PWMs

- 8.4.14 Margining

- 8.4.15 System Reset Signal

- 8.4.16 Watch Dog Timer

- 8.4.17 Run Time Clock

- 8.4.18 Data and Error Logging to Flash Memory

- 8.4.19 Brownout Function

- 8.4.20 PMBus Address Selection

- 8.4.21 Device Reset

- 8.5 Programming

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RGC|64

サーマルパッド・メカニカル・データ

- RGC|64

発注情報

8.3.1 Rail Configuration

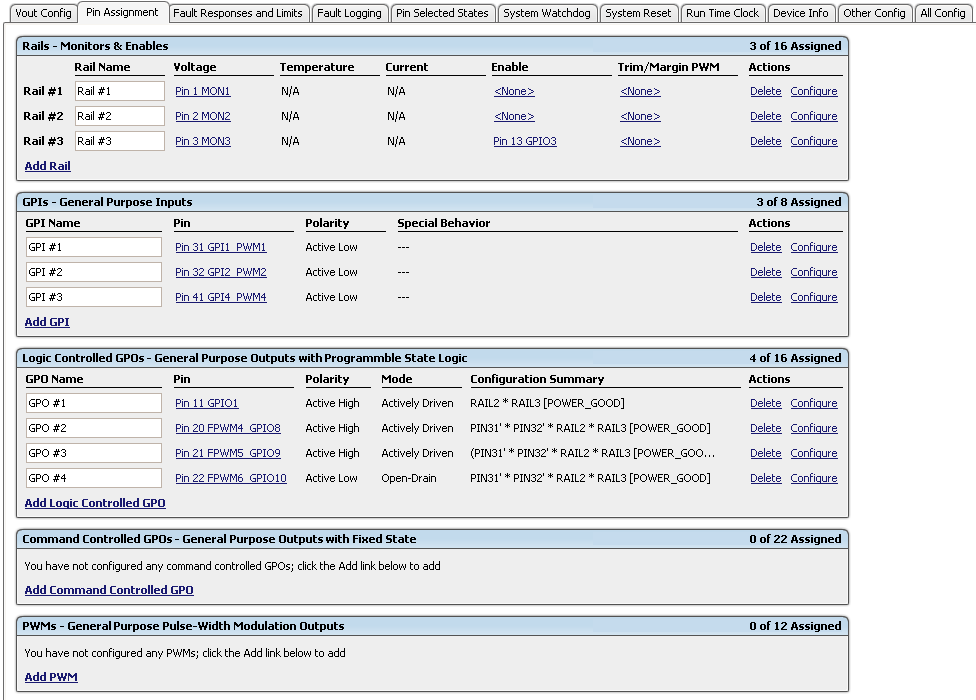

A rail includes voltage, a power supply enable and a margining output. At least one must be included in a rail definition. Once the user has defined how the power supply rails should operate in a particular system, analog input pins and GPIOs can be selected to monitor and enable each supply (Figure 6).

Figure 6. Fusion Digital Power Designer Software Pin-Assignment Tab

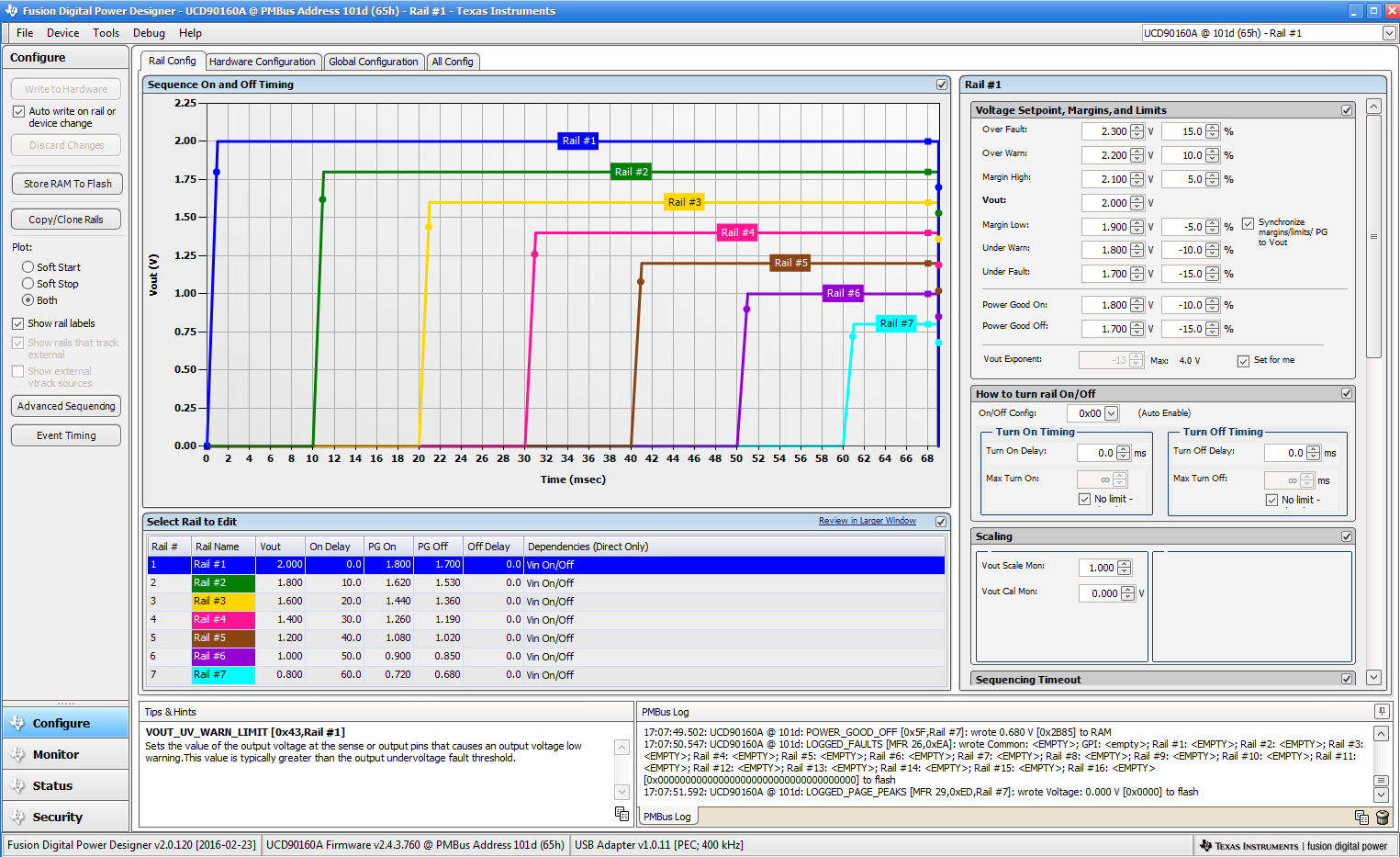

Figure 6. Fusion Digital Power Designer Software Pin-Assignment Tab After the pins have been configured, other key monitoring and sequencing criteria are selected for each rail from the Vout Config tab (Figure 7):

- Nominal operating voltage (VOUT)

- Undervoltage (UV) and overvoltage (OV) warning and fault limits

- Margin-low and margin-high values

- Power-good on and power-good off limits

- PMBus or pin-based sequencing control (On/Off Config)

- Rails, GPOs and GPIs for Sequence On dependencies

- Rails, GPOs and GPIs for Sequence Off dependencies

- Turn-on and turn-off delay timing

- Maximum time allowed for a rail to reach POWER_GOOD_ON or POWER_GOOD_OFF after being enabled or disabled

- Other rails to turn off in case of a fault on a rail (fault-shutdown slaves)

Figure 7. Fusion Digital Power Designer Software VOUT-Config Tab

Figure 7. Fusion Digital Power Designer Software VOUT-Config Tab Use the Synchronize margins/limits/PG to Vout checkbox to change the nominal operating voltage of a rail and also update all of the other limits associated with that rail according to the percentages shown to the right of each entry.

The plot in the upper left section of Figure 7 shows a simulation of the overall sequence-on and sequence-off configuration, including the nominal voltage, the turnon and turnoff delay times, the power-good on and power-good off voltages and any timing dependencies between the rails.

After a rail voltage has reached its POWER_GOOD_ON voltage and is considered to be in regulation, it is compared against two UV and two OV thresholds in order to determine if a warning or fault limit has been exceeded. If a fault is detected, the UCD90160A responds based on a variety of flexible, user-configured options. Faults can cause rails to restart, shut down immediately, sequence off using turnoff delay times or shut down a group of rails and sequence them back on. Different types of faults can result in different responses.

Fault responses, along with a number of other parameters including user-specific manufacturing information and external scaling and offset values, are selected in the different tabs within the Configure function of the Fusion Digital Power Designer software. Once the configuration satisfies the user requirements, it can be written to device SRAM if Fusion Digital Power Designer software is connected to a UCD90160A device using an I2C or PMBus interface. SRAM contents are stored to data flash memory so that the configuration remains in the device after a reset or power cycle.

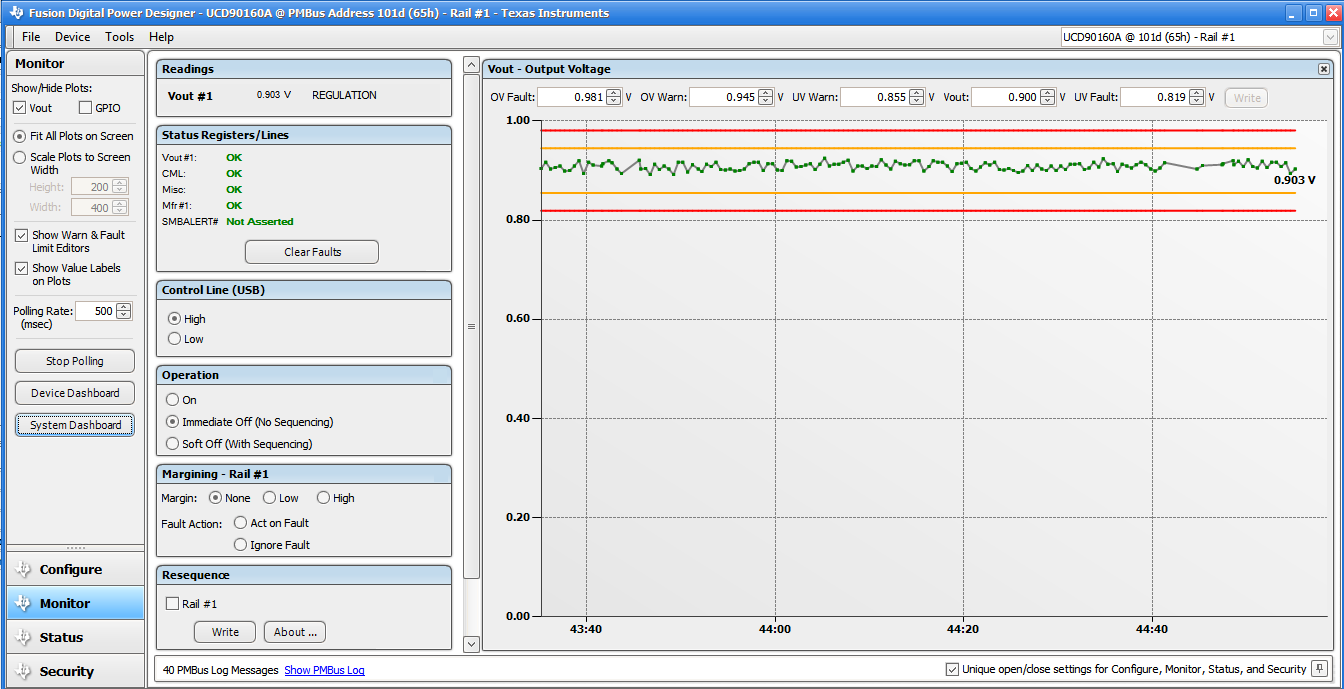

The Fusion Digital Power Designer software Monitor page has a number of options, including a device dashboard and a system dashboard, for viewing and controlling device and system status.

Figure 8. Fusion Digital Power Designer Software Monitor Page

Figure 8. Fusion Digital Power Designer Software Monitor Page The UCD90160A also has rail state for each rail to debug the system.

Table 1. Rail State

| RAIL STATE | VALUE | DESCRIPTION |

|---|---|---|

| IDLE | 1 | On condition is not met, or

rail is shut down due to fault, or rail is waiting for the resequence |

| SEQ_ON | 2 | Wait the dependency to be met to assert ENABLE signal |

| START_DELAY | 3 | TON_DELAY to assert ENABLE signal |

| RAMP_UP | 4 | Enable is asserted and rail is on the way to reach power good threshold. If the power good threshold is set to 0 V, the rail stays at this state even if the monitored voltage is bigger than 0 V. |

| REGULATION | 5 | Once the monitoring voltage is over POWER_GOOD when enable signal is asserted, rails stay at this state even if the voltage is below POWER_GOOD late as long as there is no fault action taken. |

| SEQ_OFF | 6 | Wait the dependency to be met to de-assert ENABLE signal |

| STOP_DELAY | 7 | TOFF_DELAY to de-assert ENABLE signal |

| RAMP_DOWN | 8 | Enable signal is de-asserted and rail is ramping down. This state is only available if TOFF_MAX_WARN_LIMIT is not set to unlimited; or If the turn off is triggered by a fault action, rail must not be under fault retry to show RAMP DOWN state. Otherwise, IDLE state is present. |

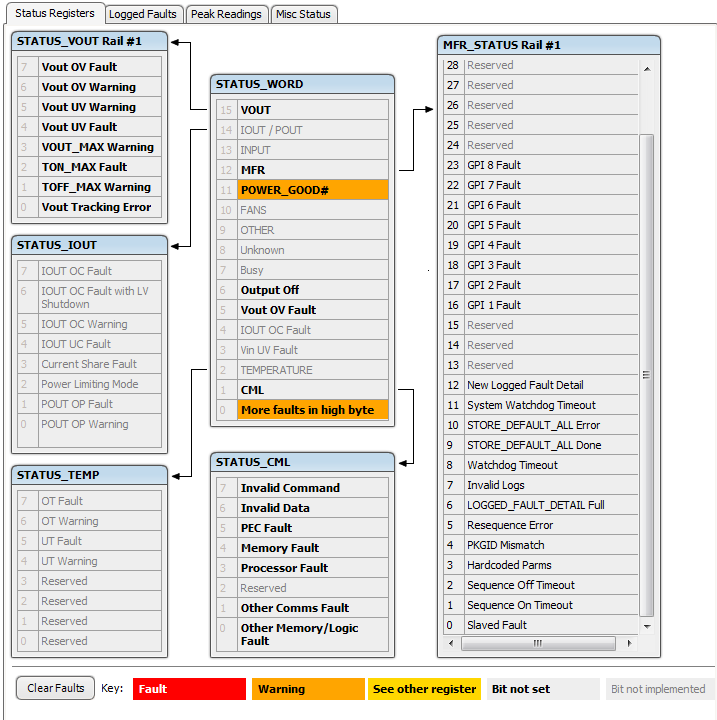

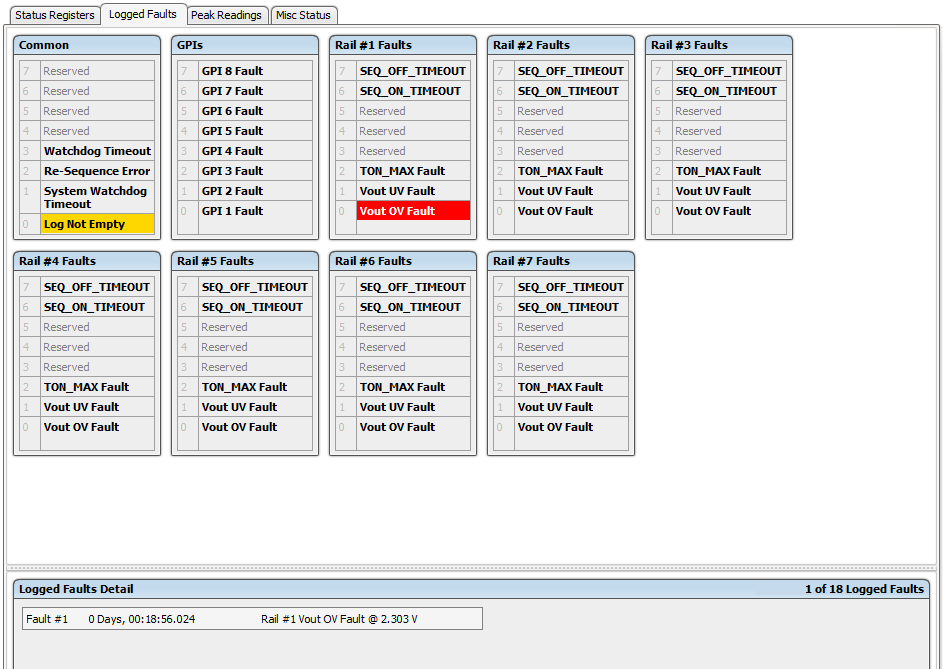

The UCD90160A also has status registers for each rail and the capability to log faults to flash memory for use in system troubleshooting. This is helpful in the event of a power supply or system failure. The status registers (Figure 9) and the fault log (Figure 10) are available in the Fusion Digital Power Designer software. See the UCD90xxx Sequencer and System Health Controller PMBus Command Reference (SLVU352) and the PMBus Specification for detailed descriptions of each status register and supported PMBus commands.

Figure 9. Fusion GUI Rail-Status Register

Figure 9. Fusion GUI Rail-Status Register  Figure 10. Fusion GUI Flash-Error Log (Logged Faults)

Figure 10. Fusion GUI Flash-Error Log (Logged Faults)