JAJSEF2D June 2013 – December 2021 DAC7760 , DAC8760

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

9.1.1.3 VOUT and IOUT Pins are Tied Together, Never Simultaneously Enabled

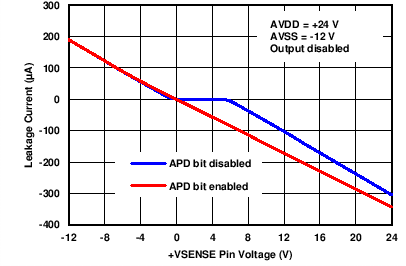

When the VOUT and IOUT pins are tied together, bit 8 of the Configuration Register (DUAL OUTEN) must be set to 0. Bits 2 down to 0 of the Control Register (RANGE) control VOUT and IOUT. Special consideration must be paid to the +VSENSE pin in this case. When VOUT is disabled, the +VSENSE pin is connected to the internal amplifier input through an internal 60-kΩ resistor as shown in Figure 8-2. This internal node has diode clamps to REFIN and GND. Setting bit 6 of the Configuration Register (APD) forces this internal node to be tied to GND through a 10-kΩ resistor, in effect, the +VSENSE pin is tied to GND through a 70-kΩ power-down resistor. Figure 9-1 shows the leakage current into the +VSENSE pin for both settings of the APD bit.

Figure 9-1 +VSENSE Leakage Current vs Pin Voltage

Figure 9-1 +VSENSE Leakage Current vs Pin VoltageWhether the APD bit is set or not set, the current output in this case incurs a gain error because the internal resistor acts as a parallel load in addition to the external load. If this gain error is undesirable, it can be corrected through the gain calibration register shown in Table 8-20. Another option is to use the application circuit in Figure 9-2.

Figure 9-2 VOUT and

IOUT Tied Together to One Pin

Figure 9-2 VOUT and

IOUT Tied Together to One PinThe buffer amplifier prevents leakage through the internal 60-kΩ resistor in current output mode and does not allow it to be seen as a parallel load. The VOUT pin is in high impedance mode in this case and allows minimal leakage current. Note that the offset of the external amplifier adds to the overall VOUT offset error and any potential phase shift from the external amplifier can cause VOUT stability issues.