JAJT258 February 2023 DLP6500FLQ , DLP650LNIR , DLP7000 , DLP7000UV , DLP9000X , DLP9000XUV , DLP9500 , DLP9500UV , DLPC410 , DLPC910

3.3 SPI フラッシュ構成方法をサポートする設計の詳細

DLPC910 および DLPC410 を使用したマスタ・シリアル・ペリフェラル・インターフェイス (SPI) フラッシュ構成をサポートするための設計の詳細は、以下のとおりです。

FPGA コントローラのマスタ・シリアル・ペリフェラル・インターフェイス・フラッシュ構成モード M[2..0] ピンは M[2:0] = 001 に変更する必要があります。

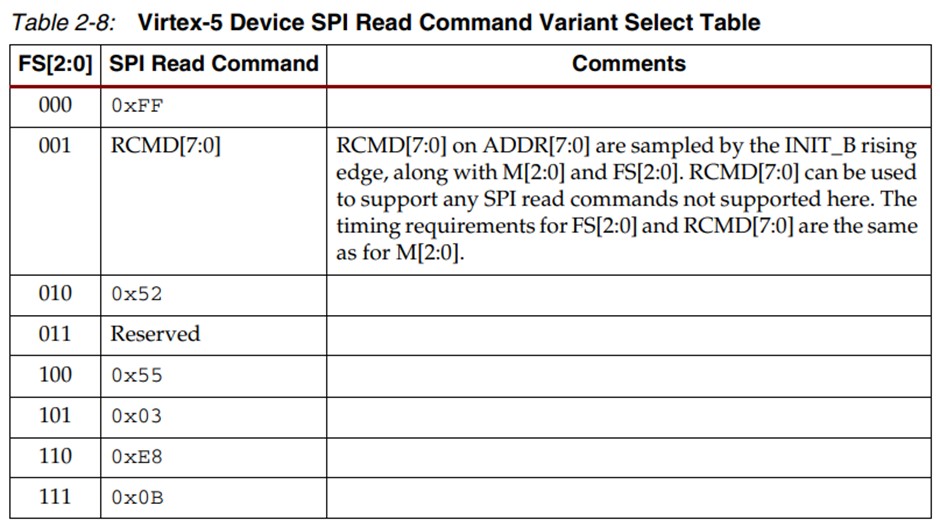

詳細については、『Xilinx Virtex-5 構成ガイド』UG191 の 62 ページを参照してください。FPGA コントローラへの接続に選択した SPI フラッシュが使用する読み取りコマンドの種類を決定するには、FS[2:0] ピンを正しく接続する必要があります。次の表 (UG191 –『Xilinx Virtex-5 構成ガイド』の表 2-8) に、利用可能な選択肢が記載されています。

FS2 = DLPC910 コントローラと DLPC410 コントローラのピン AB11

FS1 = DLPC910 コントローラと DLPC410 コントローラのピン AA13

FS0 = DLPC910 コントローラと DLPC410 コントローラのピン AA14