JAJT292 April 2019 SN74AUP2G00 , SN74HC00 , TPS53511

パワー コンバータは、通常、望ましくない障害シナリオから保護できるように設計されています。たとえば、コンバータ出力から流れ出す電流が大きすぎると、過電流保護が作動する可能性があります。これは、コンバータの出力端子が誤って互いに短絡した場合や、負荷電流が設計された最大電流を上回った場合に役立ちます。その他の一般的な故障状況としては、サーマル シャットダウンのトリップ ポイントの超過 (過熱) や出力電圧範囲の逸脱 (過電圧または低電圧) が挙げられます。

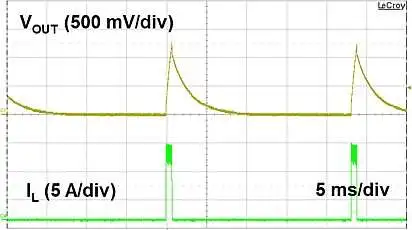

障害への対応として一般的な方法は、ヒカップと呼ばれるものです。パワー コンバータは自動的にオフになり、ある程度の時間 (たとえば 30ms) 待ってから、自動的に再起動します。この応答の例として、出力電圧とインダクタ電流の測定結果を図 1 に示します。ヒカップ障害応答であれば、外部から介入せずにシステムを回復できる可能性があります。また、出力短絡時の消費電力と発熱を低減するのにも役立ちます。

図 1 過電流シナリオに起因するヒカップ障害応答。

図 1 過電流シナリオに起因するヒカップ障害応答。ヒカップ応答が望ましくない場合もあります。おそらく、中央コントローラを使って、より複雑または高度な方法で障害応答を管理することになるでしょう。一部のシステムには冗長性が組み込まれています。障害が発生しているサブシステムを完全にオフにして、機能しているサブシステムに干渉しないようにするものです。このような場合に求められる障害応答は、障害の発生しているパワーコンバータをラッチオフすることです。パワー コンバータをラッチオフすると、イネーブル (EN) ピンまたは電源電圧をオフ / オンしてラッチをリセットしない限り、パワー コンバータの再起動を防止できます。TPS53511 など一部のデバイスにはラッチオフ応答が内蔵されていますが、ほとんどのデバイスには内蔵されていません。

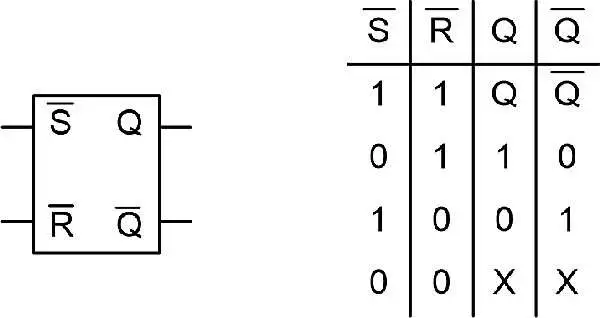

単純なセット / リセット (SR) ラッチ回路を使用して、ラッチオフ障害応答をパワー コンバータに追加できます。図 2 に、SR ラッチとその真理値表を示します。この例では、SR ラッチはアクティブ LOW 入力になっています。これは、入力が HIGH のとき、出力 Q および Q バーは変化しないことを意味します。セット (S) 入力が LOW になると、Q は HIGH (1) に設定されます。リセット (R) が LOW になると、Q は LOW (0) になります。両方の入力が LOW の場合は、出力が不定状態になるため、一般的には回避する必要があります。追加の論理ゲートを使用すると、この状況を解消できます。

図 2 アクティブ LOW 入力を備えた SR ラッチ、およびそれに対応する真理値表。

図 2 アクティブ LOW 入力を備えた SR ラッチ、およびそれに対応する真理値表。図 2 に、ラッチ回路を実装するためのアプローチの概要を示します。多くのパワー コンバータおよび監視回路には、パワー グッド (PGOOD) 出力があります。コンバータに障害が発生した場合、PGOOD 信号は LOW になり、コンバータに問題があることを示します。PGOOD 信号が LOW になると、ラッチ回路の出力 (Q) が HIGH になり、これによってコンバータの EN ピンが LOW になります。EN ピンが LOW になるとコンバータはオフになり、自動的には再起動しません。リセット信号がラッチに送られるとコンバータが再起動し、Q 出力が LOW になり、これによって EN ピンが HIGH になります。インターフェイスをより簡単にするためにインバータが内蔵されており、オープン ドレインの MOSFET (金属酸化膜半導体電界効果トランジスタ) を使用して実装されています。

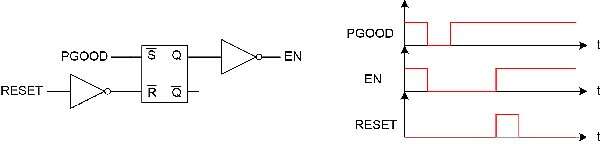

図 3 ラッチ回路の概要と信号例の図。

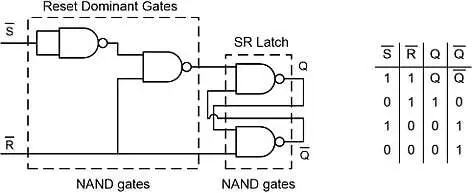

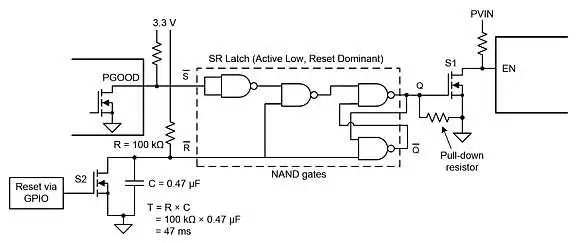

図 3 ラッチ回路の概要と信号例の図。PGOOD 信号が LOW のときでもコンバータが正しく起動または再起動できるようにするには、ラッチ回路をリセット優先状態にする必要があります。つまり、セット入力とリセット入力の両方が LOW のとき、リセット入力が優先されて、Q 出力は LOW になります。図 4 に、NAND ゲートのみを使用した簡単な実装、およびそれに対応する真理値表を示します。2 個のデュアル NAND ゲート SN74AUP2G00 IC、または 1 個のクワッド NAND ゲート SN74HC00 IC を使用してこの回路を作成できます。

図 4 NAND ゲートを使用したリセット優先ラッチ回路、およびそれに対応する真理値表。

図 4 NAND ゲートを使用したリセット優先ラッチ回路、およびそれに対応する真理値表。図 4 に、ラッチオフ回路の全体的な実装を示します。パワー コンバータの PGOOD ピンは、外付け抵抗を使用して HIGH にプルアップします (3.3V へ)。障害が発生するたびに、PGOOD に接続されたオープン ドレイン MOSFET は S バー入力を LOW にしてラッチします。これにより Q 出力が HIGH になり、MOSFET S1 がオンになります。EN ピンが LOW になって、コンバータがオフになり、ヒカップ自動再起動が防止されます。コンバータの入力電圧レール (PVIN) が上昇すると、ゲート-ドレイン間の寄生容量 (Cgd) を介した容量性結合が S1 のゲートをプルアップして、S1 がオンになる可能性があります。S1 のゲートにプルダウン抵抗を接続すると、S1 が誤ってオンになることを防止できます。

図 5 リセット可能なラッチオフ回路。

図 5 リセット可能なラッチオフ回路。SR ラッチへの R バー入力は、100kΩ 抵抗を介して HIGH にプルアップされます。オープン ドレイン MOSFET S2 は、S2 のゲートにリセット信号が供給されるたびに、R バー 信号を LOW にします。コンデンサ (C (S2 と並列に接続)) およびプルアップ抵抗 R によって遅延回路が形成されます。この例では、遅延の RC 時定数は約 47ms です。この遅延時間を調整することで、スタートアップ時に R バー入力を確実に LOW に維持できます。R バーのエッジ レートが遅いと、過剰な電流引き込みによって、一部の CMOS (Complementary Metal-Oxide Semiconductor) NAND ゲートの入力に損傷を与える可能性があります。しかし、SN74AUP2G00 ゲートはドライバが比較的弱いため、これによって損傷を受けることはありません。

別のアプローチは、シュミット トリガ入力 NAND ゲートを使用するか、または、R バー入力にシュミット トリガ バッファを追加することです。3 つ目の方法として、起動時にスイッチ S2 を継続的にオンにして、R バーを LOW にすることができます。また、R と C の値を調整して RC 遅延を短縮したり、RC 全体を取り除くこともできます。

ここで説明する回路は、障害応答のラッチオフを必要とするさまざまなパワー コンバータ アプリケーションで使用できます。ラッチオフ回路は、いくつかの単純な部品と論理ゲートを使用して、柔軟で信頼性の高いソリューションを実現します。

関連記事

この記事は、以前 EDN.com で公開された記事です。