JAJT299 July 2019 UCC28780 , UCC28782

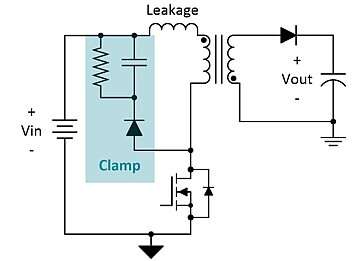

標準形式のフライバック コンバータでは、トランスの漏れインダクタンスにより、1 次側電界効果トランジスタ (FET) のドレインで電圧スパイクが発生します。このスパイクが過大になり損傷を与えないように、FET には 図 1 に示すようにクランプ回路が必要で、通常は散逸クランプを使用します。ただし、散逸クランプによる電力損失が原因で、フライバック コンバータの効率が制限されます。この Power Tip では、非散逸クランプ手法を使用して漏れエネルギーをリサイクルし、効率を改善するフライバック コンバータの 2 種類のバリエーションについて検討します。

図 1 ほとんどのフライバック コンバータは散逸クランプを採用しています

図 1 ほとんどのフライバック コンバータは散逸クランプを採用しています散逸クランプでの電力損失は、各スイッチング サイクルの漏れインダクタンス内に蓄積されたエネルギーに関連しています。FET がオンのとき、トランスの 1 次巻線の電流が、コントローラによって決定されたピーク電流値まで増加します。このピーク電流は、1 次側の磁化インダクタンスと漏れインダクタンスの両方に流れています。FET がオフになると、磁化エネルギーがトランスの 2 次巻線を経由して出力に供給されます。漏れエネルギーはトランスのコアを経由して結合しないため、1 次側にとどまり、クランプ内に流れます。

クランプ内で漏れエネルギーが消費されるだけでなく、磁化エネルギーの一部も消費されることを理解することが重要です。『Power Tip #17』で説明したように、1 次巻線の電圧を反射出力電圧よりはるかに高い値にクランプすると、クランプ内で消費される磁化エネルギーの量が最小化されます。

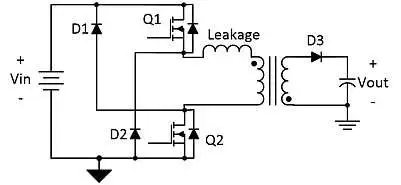

2 スイッチ フライバックは、漏れエネルギーを回収するフライバック コンバータの一般的なバリエーションです。図 2 は、2 スイッチ フライバックの概略回路図です。2 個の 1 次側 FET を、これらの FET の間にある 1 次巻線と直列に接続します。これら 2 つの FET は、同時にオンまたはオフになります。これらがオンのとき、1 次巻線は入力に接続され、ピーク電流まで励磁されます。FET がオフになると、2 次巻線によって磁化エネルギーが出力に供給され、漏れエネルギーは D1 と D2 を経由して入力にリサイクルされます。漏れエネルギーを再利用することで、2 スイッチ フライバックは、対応するシングル スイッチの散逸クランプよりも高い効率を誇ります。

図 2 2 スイッチ フライバックは、漏れエネルギーを入力へリサイクルします

図 2 2 スイッチ フライバックは、漏れエネルギーを入力へリサイクルします効率の向上は、2 つのスイッチが同時に導通していることによって多少相殺されます。そのため、特に低入力電圧のアプリケーションでは、導通損失が増加する傾向があります。幸い、両方の FET のドレイン - ソース間電圧は入力電圧にクランプされるため、シングル スイッチ フライバックよりも電圧定格の低い FET を使用できます。高入力電圧アプリケーションでは、クランプされた電圧ストレスもメリットがあります。

効率の向上は磁化インダクタンスに対する漏れインダクタンスの比率に関係し、通常は約 2% です。漏れエネルギーを再利用することには、効率の向上以外の利点もあります。大電力のフライバック アプリケーション (一般に 75W 超) では、散逸クランプでの損失が原因で、熱管理に大きな問題が生じる可能性があります。2 スイッチ フライバックを採用すると、この熱源を完全に排除できます。

このような効率の向上と放熱性能の改善の代償は、コストと複雑さの増大という形で発生します。追加の FET が必要になるだけでなく、ハイサイド FET 用の絶縁型ドライブも必要になります。また、トランスの巻線比は、反射出力電圧が最小入力電圧よりも低くなるように設定する必要があります。そうでない場合、出力電圧がクランプされ、トランスは適切にリセットされません。その結果、2 スイッチ フライバックは本質的に、最大 50% のデューティ サイクルに制限されます。実際には、漏れインダクタンスが迅速にリセットされるように、反射出力電圧は最小入力電圧よりも十分に低くする必要があります。

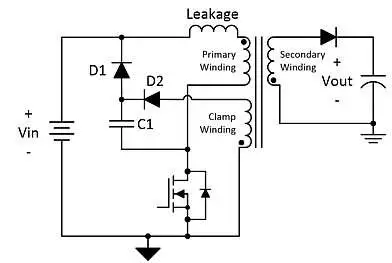

図 3 の回路に、漏れエネルギーを再利用する別の方法を示しますが、これはシングル スイッチ フライバックを使用します。この非散逸クランプは新しいものではありませんが、よく知られていません。この方式は、2 スイッチ フライバックの利点の多くを共有しています。

図 3 シングル スイッチ フライバックに追加された、シンプルな非散逸クランプ

図 3 シングル スイッチ フライバックに追加された、シンプルな非散逸クランプこのクランプを実装するには、トランスの 1 次側にクランプ巻線を追加する必要があります。この巻線は 1 次巻線と同じ巻数にする必要があります。クランプ コンデンサを追加し、FET のドレインに接続します。クランプ コンデンサのもう一方の端は、ダイオード D1 によって入力電圧に、またダイオード D2 によってクランプ巻線にクランプされます。

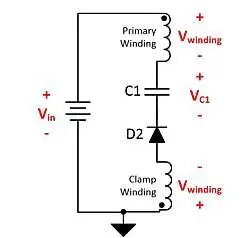

図 4 に示すように、クランプ巻線と D2 は、クランプ コンデンサの両端の電圧を入力電圧に等しい最大値に制限します。これは、1 次側ループの周囲にキルヒホッフの法則を適用すると簡単に分かります。2 つの 1 次巻線電圧は、極性や大きさに関係なく、互いに打ち消し合うことに注意してください。この方法は、両方の巻線で同じ数の巻線を使用する場合にのみ機能します。

図 4 クランプ コンデンサの電圧は入力電圧によって制限されます

図 4 クランプ コンデンサの電圧は入力電圧によって制限されますこのクランプの動作を理解するために、FET がオフになったときに何が起こるか考えてみます。1 次側 FET がオフになると、漏れインダクタンス内の電流がクランプ コンデンサと順バイアス ダイオード D1 を流れます。D1 がオンの間、漏れインダクタンスの両端の電圧は、入力電圧と反射出力電圧の差に等しくなります。漏れインダクタンス内の電流が 0 に低下すると、D1 はオフになります。クランプ コンデンサに供給される漏れエネルギーにより、クランプ コンデンサの電圧は一時的に入力電圧よりわずかに高くなります。D1 がオフになると、D2 クランプは、蓄積された電荷をトランス巻線のカップリングを経由して出力に効果的に伝達します。

このクランプ回路は、必要な部品点数が少なく、2 スイッチ フライバックよりも安価です。2 スイッチ フライバックと同様に、効率が数パーセント改善され、漏れエネルギーの放散に関連する熱の問題が解消されます。また、このクランプ回路はデューティ サイクルを最大 50% に制限します。トレードオフは、この回路が入力電圧の 2 倍以上の定格を持つ、より高い電圧の FET を必要とすることです。また、FET のドレインに高い電圧が印加されるため、2 スイッチ フライバックよりも電磁干渉の問題が大きくなる可能性があります。

アクティブ クランプ フライバックは、漏れエネルギーを回収すると同時にゼロ電圧スイッチングを実現するフライバックの別のバージョンです。アクティブ クランプ フライバックはより複雑で、UCC28780 のような特別なコントローラが必要で、独自の Power Tip が必要です。そのため、これは後ほど説明します。次回高出力フライバックを設計するときは、効率を向上させ、電源の温度が上がらないように、非散逸クランプの採用を検討してください。

関連記事

- 『低コストのフライバック コンバータ向けに効率を向上』

- Power Tips #76:『フライバック コンバータ設計上の検討事項』

- Power Tips #77:『CCM フライバック コンバータの設計』

- Power Tip #17:『フライバック コンバータの緩衝』

この記事は、以前 EDN.com で公開された記事です。