JAJT311 February 2024 LM5155 , LM51551 , LM5156 , TPS55340

絶縁型の低電力出力にどのトポロジを使用すればよいかを検討するとき、最初に挙げられるのはおそらくフライバックです。フライバックは優れたトポロジで、低コスト、少ないコンポーネント数、出力の追加が簡単などの利点がありますが、欠点もいくつかあります。フライバック トランスの漏れインダクタンスに関連する電界効果トランジスタ (FET) と整流器のリンギングは、電磁干渉 (EMI) を発生させ、部品へのストレスを増大させて、効率を低下させます。さらに、複数の出力が存在する場合、特に負荷の変動が大きい場合は、適切に制御された電圧を得ることが難しくなる可能性があります。これらの問題点のいくつかを軽減するため、SEPIC (シングル エンド 1 次側インダクタ コンバータ) を絶縁するという別の方法もあります。この方法について解説します。

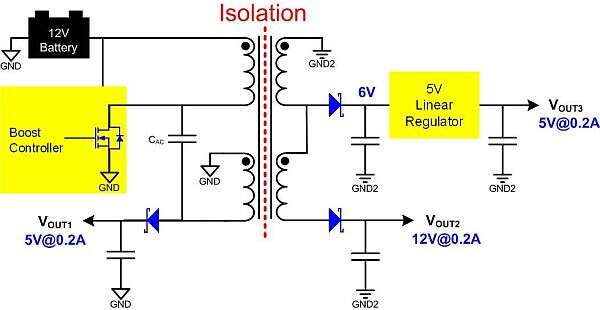

SEPIC は非絶縁トポロジです。ただし、フライバックと同様に、トランスの巻線を追加して絶縁型出力を作り出すのは簡単です。図 1 に示す概略回路図は、左側に単一の非絶縁型出力、右側に 2 つの追加の絶縁型出力を作り出す、標準的な SEPIC コンバータを示しています。1 つ目の絶縁巻線は、5V リニア レギュレータへの入力として、公称 6V の出力を供給します。2 つ目の絶縁型巻線は 1 つ目の巻線の上にスタックして、制御されていない 12V 出力を生成します。

VOUT1 のトランス巻線と絶縁巻線 (VOUT2、VOUT3) との間は密結合する必要があります。これらの巻線のエネルギーは 3 つの出力すべてに同時に転送されるからです。これらの巻線間の漏れインダクタンスは、電圧レギュレーションを劣化させるだけです。ただし、SEPIC の 1 次巻線と VOUT1 巻線を密結合する必要はありません。コンデンサ CAC は、昇圧 FET がオフになったとき VOUT1 へのリーケージ エネルギー用の低インピーダンス パスを提供するため、FET にわずかなリンギングが発生します。SEPIC の 1 次巻線電圧波形は、フライバックよりもリンギングが大幅に少ないため、極端なクロスロード条件でスパイク ピーク検出が多く発生する場合は特に、出力電圧レギュレーションの改善に役立ちます。

図 1 追加の巻線を持つ SEPIC コンバータには、絶縁型出力があります

図 1 追加の巻線を持つ SEPIC コンバータには、絶縁型出力がありますどの SEPIC でも同じですが、1 次側と VOUT1 との巻線比は 1:1 にする必要があります。ただし、他のすべての出力はこの巻線比に制限されていないため、必要な出力電圧が得られるように調整できます。この巻線比は、式 1 で簡単に計算できます。

SEPIC とフライバックの FET 電圧リンギングの違いを、図 2 に示します。フライバックへの変換を行う CAC を取り除くだけで、SEPIC 回路からフライバック FET 電圧波形を得ることができます。FET のリンギングを除去することで、絶縁型出力に伝達される非結合エネルギーが大幅に低減され、レギュレーションが改善されます。

図 2 SEPIC FET の電圧リンギングはフライバックより小さいため、ストレスの低減と出力電圧レギュレーションの改善につながります

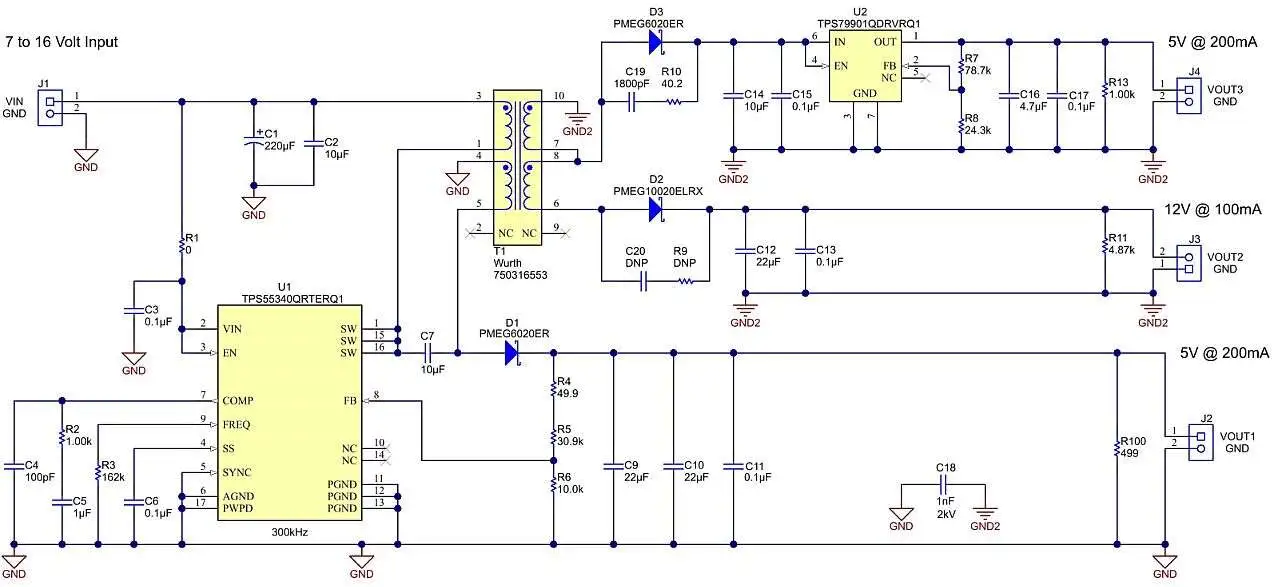

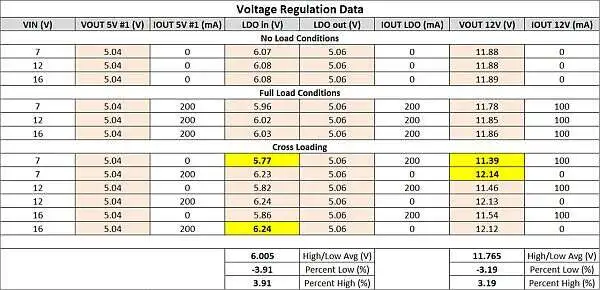

図 2 SEPIC FET の電圧リンギングはフライバックより小さいため、ストレスの低減と出力電圧レギュレーションの改善につながります図 4 のレギュレーション データを取得するために使用したテスト回路図を 図 3 に、実際のハードウェアの写真を 図 5 に示します。この設計では、VOUT1 の制御された電圧に 1 次側フィードバックを使用します。これらの絶縁型出力は、トランスの密結合と小さなプリロードを組み合わせることで、妥当な電圧レギュレーションを行います。リニア レギュレータは 5V の絶縁型出力を一定の値に保持するので、重要なのは入力の最低値と最高値です。リニア レギュレータへの入力が低すぎると、出力電圧が低下する可能性があります。逆に、リニア レギュレータへの入力が高すぎると、過剰な電力が消費されます。

絶縁型出力のレギュレーション データは、ワースト ケースの最低および最高電圧が極端なクロスロード状態で発生することを示しています。絶縁巻線が最大負荷で、VOUT1 が無負荷のとき、絶縁巻線の電圧が最低になります。絶縁巻線が無負荷で、VOUT1 が最大負荷のとき、絶縁巻線の電圧が最高になります。テスト データに基づき、レギュレーションの ±4% 未満の変動を測定しました。これらの結果はすべての設計に当てはまるものではありませんが、類似の設計では ±5% の電圧レギュレーションをある程度達成できる一方、フライバックは変動が少なくとも数 % 大きくなる可能性が高いことを示しています。

Brian King が Power Tips #78 で説明したように、同期整流器を実装して、フライバックのクロス レギュレーションを大幅に改善することも可能です。ただし、このような改善には、よりコストの高い FET と追加の駆動回路を使用する必要があります。この同じ技法を絶縁型 SEPIC コンバータにも適用できますが、非絶縁型出力の整流器も同期整流器にする必要があります。同期 SEPIC を簡単に実装する方法については、以前の テキサス・インスツルメンツのブログの投稿で解説しました。

図 3 デュアル絶縁型出力を採用した実際の SEPIC 設計

図 3 デュアル絶縁型出力を採用した実際の SEPIC 設計 図 4 測定された電圧レギュレーションのデータ

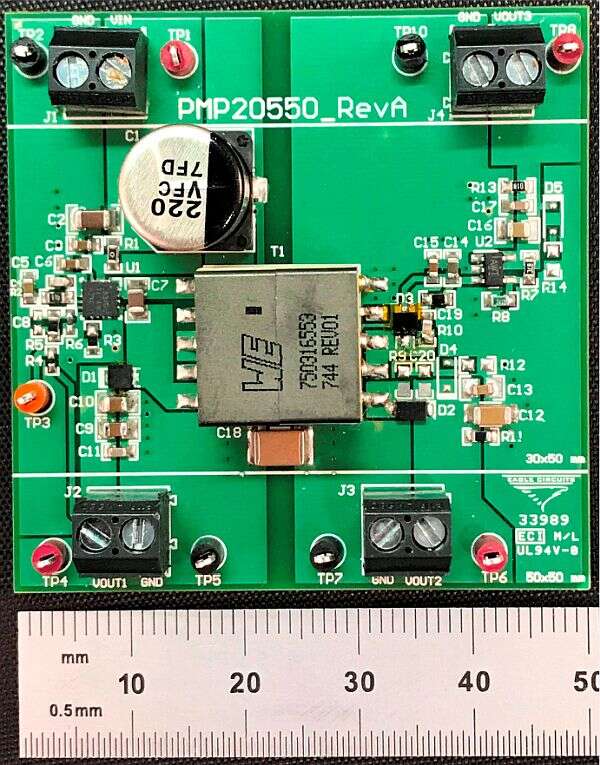

図 4 測定された電圧レギュレーションのデータ 図 5 プロトタイプ回路のハードウェア

図 5 プロトタイプ回路のハードウェア絶縁型 SEPIC コンバータは、絶縁型出力電圧を追加するとき最初に検討される選択肢ではないかもしれませんが、漏れインダクタンスに関連するリンギングへの耐性がフライバックよりも高いため、出力電圧のレギュレーションを改善できます。これにより、追加のポスト レギュレーションが不要になり、コストを削減できます。

さらに詳しい情報については、テキサス・インスツルメンツの Power House についての Power Tips をご覧ください。