KOKT041 February 2024 TMS320F280025C , TMS320F280039C , TMS320F280049C

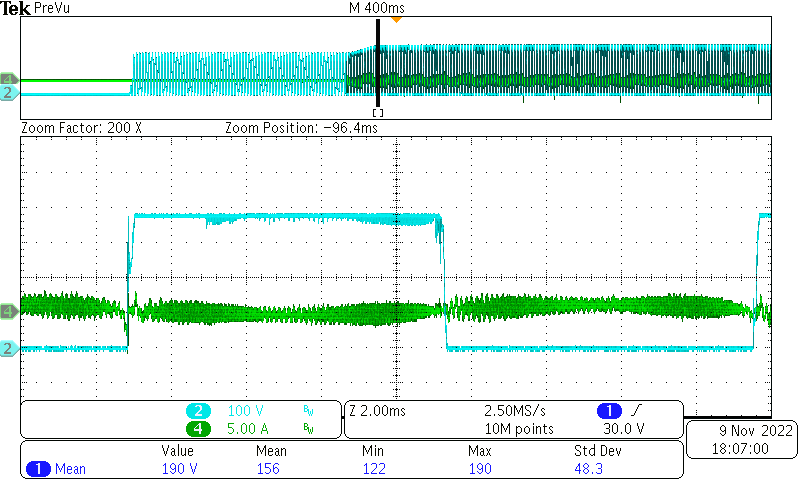

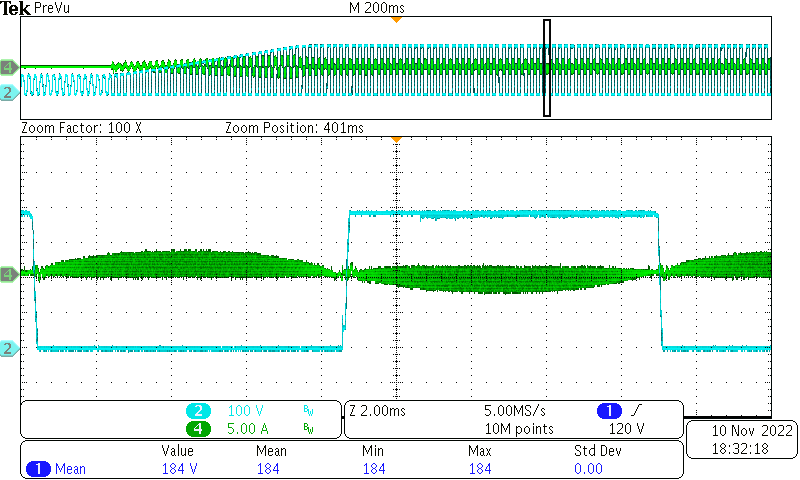

부스트 PFC(역률 보정)와 같은 디지털 전원 공급 장치를 설계할 때 그림 1에서 이런 전류 오실레이터가 표시된 것을 본 적이 있습니까?

그림 1 PFC 단계에서 전류 진동이 발생합니다. 출처: 텍사스 인스트루먼트

그림 1 PFC 단계에서 전류 진동이 발생합니다. 출처: 텍사스 인스트루먼트이러한 불안정한 진동은 너무 빠른 제어 대역에 의해 발생한다고 생각할 수 있으므로 PI(비례 적분) 컨트롤러의 KP(비례 이득)와 KI(적분 이득)를 줄이고 교차 주파수를 크게 줄입니다. 그러면 진동이 사라집니다.

하지만 이것이 가장 좋은 해결책일까요? 전류 루프 대역폭이 낮아지면 제어 속도가 감소하지만 THD(총 고조파 왜곡) 테스트가 실패할 수 있습니다. 그리고 소스 임피던스가 약간 높으면 진동이 다시 나타날 수도 있습니다.

이러한 불안정성의 다른 원인이 있을 수 있을까요? 어떻게 하면 충분한 위상 여유로 최고의 제어 대역폭을 얻을 수 있을까요? 디지털 제어 루프를 자세히 분석하여 이러한 잠재적 실수가 어떻게 발생했는지 살펴봅시다. 또한 제어 펌웨어에서 이러한 불안정이 발생하는지 확인하는 방법도 보여드리겠습니다.

MCU 기반 디지털 제어

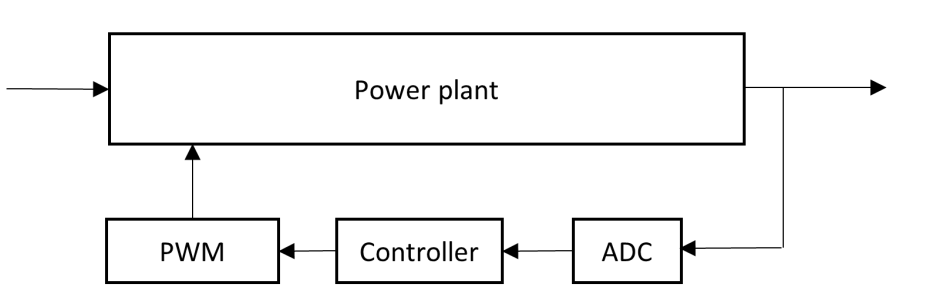

그림 2에는 MCU 기반 디지털 제어 시스템이 나와 있습니다.

그림 2 디지털 제어 시스템은 마이크로컨트롤러를 기반으로 제작되었습니다. 출처: 텍사스 인스트루먼트

그림 2 디지털 제어 시스템은 마이크로컨트롤러를 기반으로 제작되었습니다. 출처: 텍사스 인스트루먼트제어 루프에는 대상 전류/전압을 샘플링하는 아날로그-디지털 컨버터(ADC), 조정 값을 생성하는 디지털 컨트롤러, 조정을 실행하고 듀티 또는 주파수를 변경하여 목표 전류/전압을 변경하는 펄스 폭 변조기(PWM)가 포함되어 있습니다.

스위치 모드 전원 공급 장치(SMPS)의 ADC 샘플링은 종종 두 스위칭 사이클의 중간 지점에서 이루어지므로 스위칭으로 인한 잡음 장애를 방지할 뿐만 아니라 연속 전도 모드(CCM)에서 전력 인덕터의 평균 전류 값도 얻을 수 있습니다.

디지털 컨트롤러는 인터럽트 서비스 루틴(ISR)에서 계산되며 PWM 출력과 동기적으로 트리거될 수 있습니다. 트리거 이벤트는 PWM의 "카운터"가 "ZERO," "PERIOD" 또는 특정 값 "CMP"와 같은 경우 중 하나일 수 있습니다.

컨트롤러가 모든 계산을 완료하면 PWM을 즉시 업데이트할 수 없지만 PWM 카운터가"ZERO" 또는 "PERIOD"와 같은 전용 순간에 PWM 레지스터를 섀도우 레지스터로 로드해야 합니다. 카운터가 상승하거나 하락하는 동안 PWM 값이 변경되면 잘못된 PWM 동작, 누락된 펄스 또는 중복 펄스를 생성할 수 있습니다.

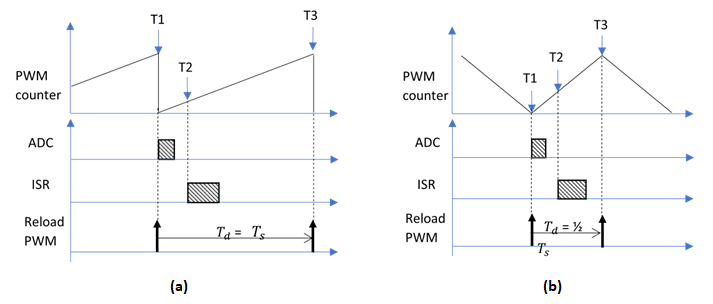

아날로그 제어 시스템과 달리 디지털 제어는 샘플링 주파수에 의해 실행되며, 새 값을 PWM에 다시 로드하기 위해 샘플링에서 지연 시간(Td)이 있어야 합니다. PWM 수정은 단일 에지 변조(카운트 업/카운트 다운 모드)에서 한 번 발생하는 플립 모멘트를 조정하여 구현되며, 이중 에지 변조(카운트 업 다운 모드)에서 두 번 발생합니다. 따라서 최소 Td는 선택한 변조 재로드 주파수에 따라 1 스위칭 사이클 Ts(그림 3a에 표시된 대로) 또는 1/2 스위칭 사이클 Ts/2(그림 3b에 표시된 대로)가 됩니다.

그림 3 PWM 조정으로 최소 지연 시간이 도입됩니다. (a) 업 모드, (b) 업-다운 모드. 출처: 텍사스 인스트루먼트

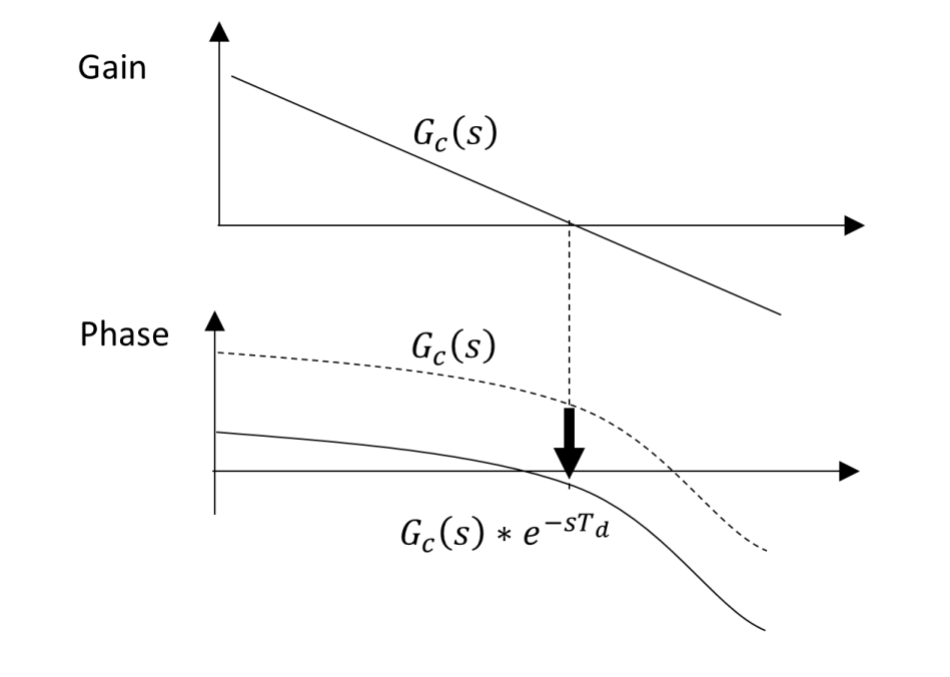

그림 3 PWM 조정으로 최소 지연 시간이 도입됩니다. (a) 업 모드, (b) 업-다운 모드. 출처: 텍사스 인스트루먼트그림 4을 보면 Td는 전달 함수에서 e-sxT d로 표현되며, 이는 위상 마진을 감소시킵니다. 물론 위상 마진이 45도 미만이면 시스템이 불안정해지고 진동이 발생합니다.

그림 4 시간 지연의 영향은 보드 플롯에 나와 있습니다. 출처: 텍사스 인스트루먼트

그림 4 시간 지연의 영향은 보드 플롯에 나와 있습니다. 출처: 텍사스 인스트루먼트디지털 제어 구현에서 코드 오류가 발생할 수 있습니다

올바르게 실행하면 최소 Td는 하나의 스위칭 사이클 Ts 절반 스위칭 사이클 Ts/2입니다. 그러나 ADC, ISR 및 PWM 재로드의 결과를 고려하지 않았다면 제어 지연을 두 개 이상의 스위칭 사이클로 확장하면 위상 마진이 감소하여 불안정해질 수 있습니다.

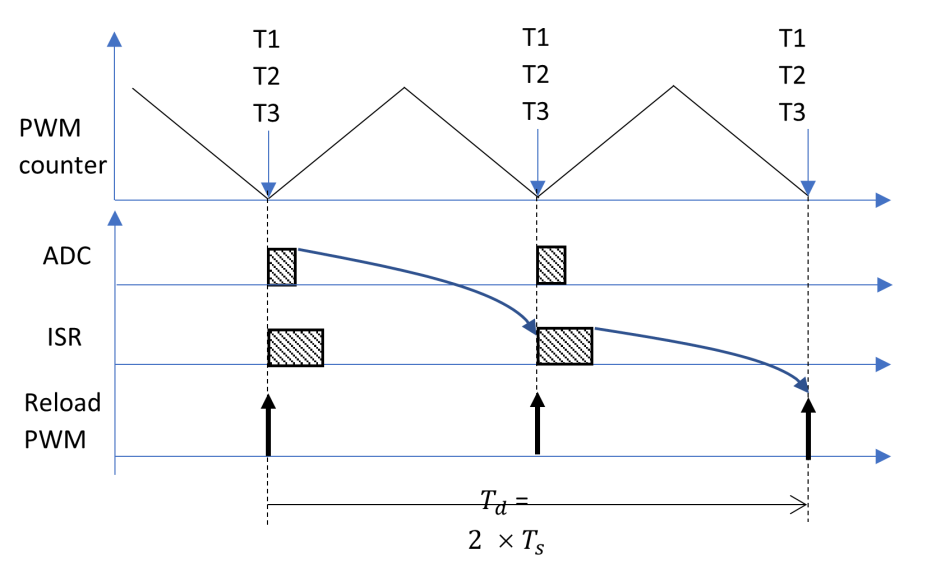

예를 들어 그림 5에서 ADC의 ISR 트리거와 PWM 재로드는 PWM 카운터가 0이 되면 동시에 시작됩니다.

모든 블록이 동시에 실행되지만 이 경우 Td가 0이 될 것으로 예상할 수 있습니까? 절대 아닙니다!

그림 5 다음은 지연 시간이 더 긴 잘못된 코드의 예입니다. 출처: 텍사스 인스트루먼트

그림 5 다음은 지연 시간이 더 긴 잘못된 코드의 예입니다. 출처: 텍사스 인스트루먼트이는 ADC 변환과 ISR 계산에 모두 둘 이상의 MCU 클로킹 사이클이 필요하고 ISR이 ADC 결과를 읽을 때 ADC 변환이 아직 완료되지 않았기 때문입니다. 따라서 ISR은 계산에 사용할 "이전" 샘플 값을 얻고 최신 값의 계산은 다음 스위칭 사이클까지 지연됩니다. ISR 계산이 완료된 후 새 PWM 값은 섀도우 레지스터에만 쓰여지고, 이후 스위칭 사이클에서 다시 로드됩니다. 실제로 Td의 총 제어 지연은 두 번의 스위칭 주기, 즉 2 x Ts가 됩니다.

여기에 표시된 예제 외에도 다른 구현에서는 유사한 확장된 제어 지연을 도입할 수 있습니다. 예를 들어 ISR 코드의 컨트롤러 계산 후에 ADC 값 판독을 삽입하거나 컨트롤러를 계산하기 전에 N 사이클 알고리즘 평균을 추가하는 경우 등이 있습니다.

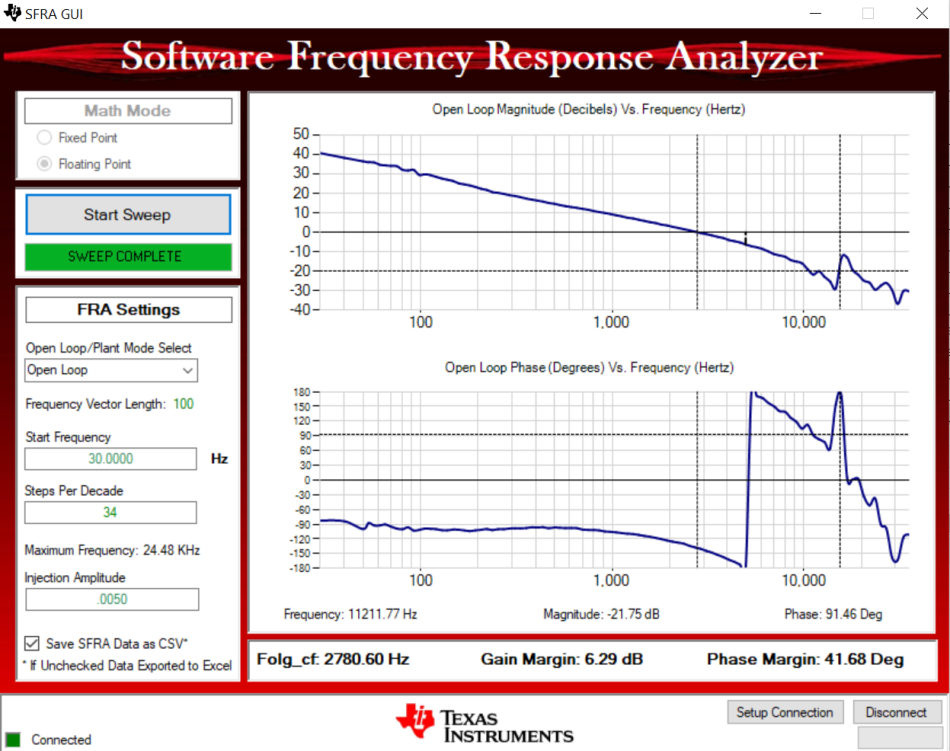

그림 6에서 보듯이 그림 5의 오구현으로 약 3kHz에서 게인 크로스 주파수를 설정하면 위상 마진은 41.68도입니다. 이것은 45도 미만이며, 초크 전류는 그림 1의 파형과 같이 상당한 진동을 가지고 있으므로 교차 주파수를 2kHz 미만으로 줄여야 합니다. 그러면 iTHD가 악화되어 요구 사항에 실패합니다.

그림 6 잘못된 코드 구현의 보드 플롯. 출처: 텍사스 인스트루먼트

그림 6 잘못된 코드 구현의 보드 플롯. 출처: 텍사스 인스트루먼트설계 솔루션

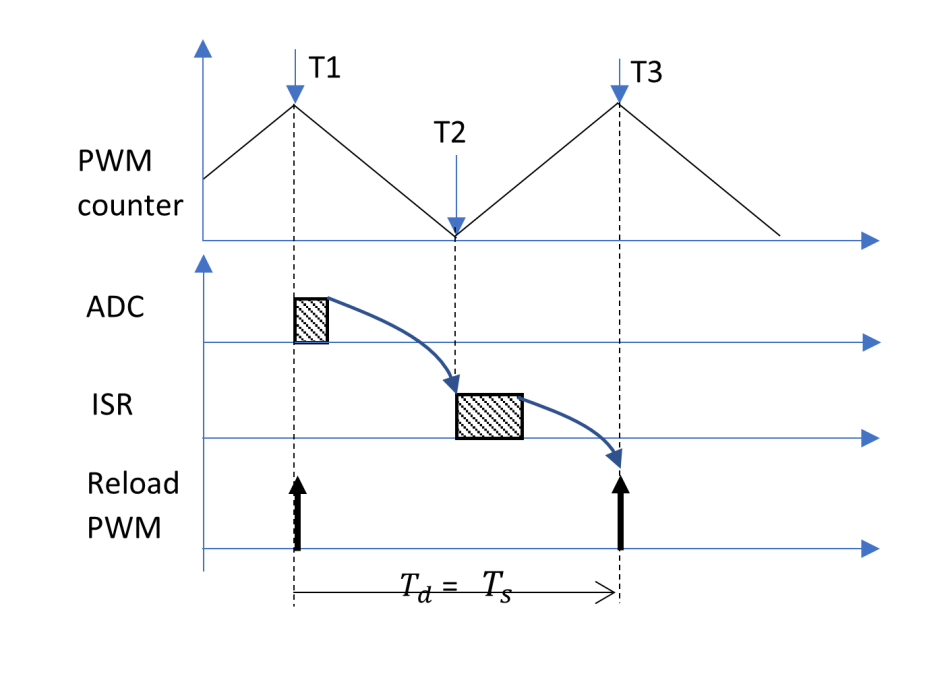

그림 7에 나와 있듯이 ADC 변환을 카운터 = 기간의 순위로 이동하여 이 문제를 손쉽게 해결할 수 있으며, 다음 카운터 = 기간에서 PWM 재로드가 발생합니다.

그림 7 코드를 개선하면 제어 지연을 줄일 수 있습니다. 출처: 텍사스 인스트루먼트

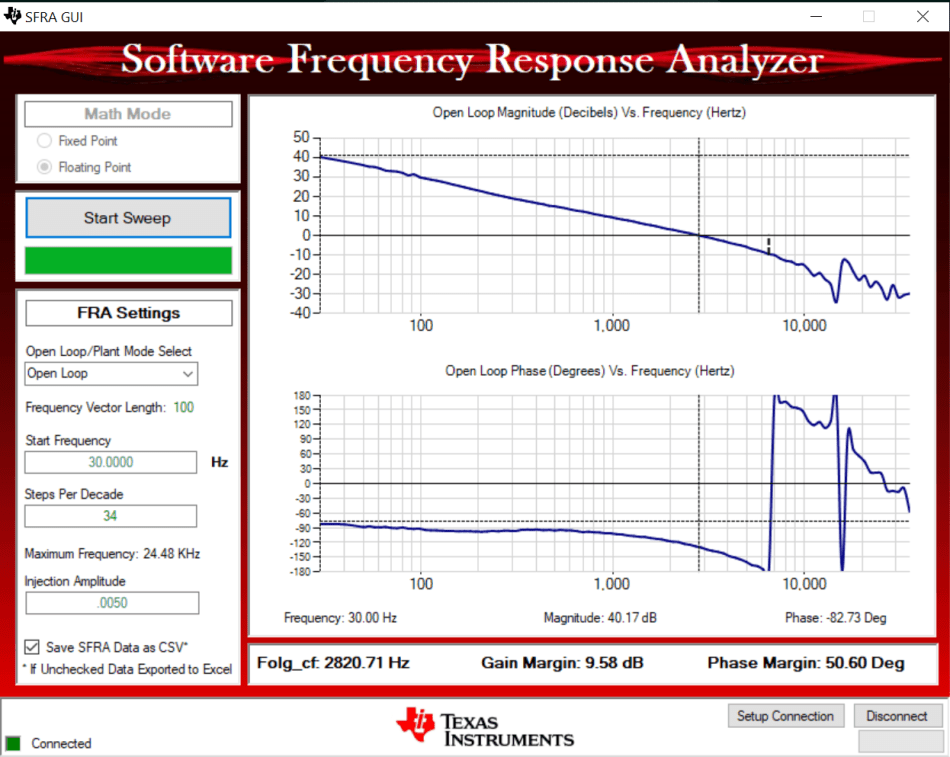

그림 7 코드를 개선하면 제어 지연을 줄일 수 있습니다. 출처: 텍사스 인스트루먼트제어 지연은 1개의 스위칭 사이클로 감소합니다. 그림 8 및 그림 9에서 보듯이 위상 마진은 크게 증가하고, 전류 진동은 사라집니다.

그림 8 향상된 코드의 보드 플롯. 출처: 텍사스 인스트루먼트

그림 8 향상된 코드의 보드 플롯. 출처: 텍사스 인스트루먼트 그림 9 코드가 개선된 파형. 출처: 텍사스 인스트루먼트

그림 9 코드가 개선된 파형. 출처: 텍사스 인스트루먼트잘 구성된 제어 체계

ADC 샘플링에서 PWM 조정까지 디지털 구현의 제어 지연은 위상 마진을 줄이고 진동을 발생시킵니다. 이 문제를 해결할 때는 ADC 샘플링, 컨트롤러 계산 및 PWM 재로드의 결과를 고려하십시오. 잘 구성된 제어 체계는 지연을 절반 또는 하나의 스위칭 사이클로 최소화하여 위상 마진과 루프 대역폭을 증가시킵니다.