SBAA532A February 2022 – March 2024 ADS1119 , ADS1120 , ADS1120-Q1 , ADS112C04 , ADS112U04 , ADS1130 , ADS1131 , ADS114S06 , ADS114S06B , ADS114S08 , ADS114S08B , ADS1158 , ADS1219 , ADS1220 , ADS122C04 , ADS122U04 , ADS1230 , ADS1231 , ADS1232 , ADS1234 , ADS1235 , ADS1235-Q1 , ADS124S06 , ADS124S08 , ADS1250 , ADS1251 , ADS1252 , ADS1253 , ADS1254 , ADS1255 , ADS1256 , ADS1257 , ADS1258 , ADS1258-EP , ADS1259 , ADS1259-Q1 , ADS125H01 , ADS125H02 , ADS1260 , ADS1260-Q1 , ADS1261 , ADS1261-Q1 , ADS1262 , ADS1263 , ADS127L01 , ADS130E08 , ADS131A02 , ADS131A04 , ADS131E04 , ADS131E06 , ADS131E08 , ADS131E08S , ADS131M02 , ADS131M03 , ADS131M04 , ADS131M06 , ADS131M08

- 1

- Abstract

- Trademarks

- 1Bridge Overview

- 2Bridge Construction

- 3Bridge Connections

- 4Electrical Characteristics of Bridge Measurements

- 5Signal Chain Design Considerations

-

6Bridge Measurement Circuits

- 6.1 Four-Wire Resistive Bridge Measurement with a Ratiometric Reference and a Unipolar, Low-Voltage (≤5 V) Excitation Source

- 6.2 Six-Wire Resistive Bridge Measurement With a Ratiometric Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source

- 6.3 Four-Wire Resistive Bridge Measurement With a Pseudo-Ratiometric Reference and a Unipolar, High-Voltage (> 5 V) Excitation Source

- 6.4 Four-Wire Resistive Bridge Measurement with a Pseudo-Ratiometric Reference and Asymmetric, High-Voltage (> 5 V) Excitation Source

- 6.5 Four-Wire Resistive Bridge Measurement With a Ratiometric Reference and Current Excitation

- 6.6 Measuring Multiple Four-Wire Resistive Bridges in Series with a Pseudo-Ratiometric Reference and a Unipolar, Low-Voltage (≤5V) Excitation Source

- 6.7 Measuring Multiple Four-Wire Resistive Bridges in Parallel Using a Single-Channel ADC With a Ratiometric Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source

- 6.8 Measuring Multiple Four-Wire Resistive Bridges in Parallel Using a Multichannel ADC With a Ratiometric Reference and a Unipolar, Low-Voltage (≤ 5 V) Excitation Source

- 7Summary

- 8Revision History

6.5.4 Design Notes

The IDAC current, IIDAC, in conjunction with the nominal bridge resistance, RBRIDGE, determine the total voltage across the bridge, VBRIDGE. Assuming zero lead wire resistance, VBRIDGE = VEXCITATION = VEXCITATION+ – VEXCITATION-, which is also used as the ADC reference voltage, VREF. Unlike the circuit described in Section 6.1 where VEXCITATION is fixed, VBRIDGE varies as RBRIDGE changes. This varying VBRIDGE voltage causes VREF and the input voltage to the ADC to change as well. Additionally, the current source does not inherently center the bridge common-mode voltage, VCM(Bridge), as it does in other bridge measurement circuits. The bias resistor, RBIAS, helps keep VCM(Bridge) within the common-mode range of the ADC analog and voltage reference inputs.

Small variations in RBRIDGE due to tension or compression cause the differential bridge output voltage to change. The PGA integrated into the ADC gains up this low-level signal to reduce system noise and utilize more of the ADC full-scale range (FSR). The ADC samples and converts this amplified voltage against VREF, which is the same voltage used to excite the bridge and therefore ratiometric. The excitation source noise and drift are seen equally in both VIN and VREF in a ratiometric reference configuration, effectively removing these errors from the ADC output code.

A four-wire resistive bridge measurement with a ratiometric reference and current excitation requires:

- Differential analog inputs (AINP and AINN)

- Differential reference inputs (REFP and REFN)

- Low-noise amplifier

- Constant-current source (IDAC)

- Bias resistor (optional in some cases)

Additionally, a four-wire resistive bridge measurement with a ratiometric reference and current excitation requires consideration of several factors, including:

- Absolute (VREFP and VREFN) and differential (VREF) reference voltages

- Bridge excitation current, IIDAC

- IDAC compliance voltage

- Bridge common-mode voltage, VCM(Bridge)

- Voltage across the bridge, VBRIDGE

- Bridge resistance, RBRIDGE

- Bias resistor value, RBIAS

All of these factors are inter-related such that selecting one influences the selection of one or more of the others. Several design iterations can be required to determine a final result that meets all of the system specifications.

To reduce the number of possible circuit configurations, it is recommended to begin the design by choosing an ADC with differential VREF inputs, integrated IDACs, and a PGA. The absolute and differential VREF specifications constrain the possible values of VBRIDGE. Integrated IDACs limit the choice of IIDAC to several discrete values and eliminate external circuitry to drive the bridge. The integrated IDACs also have a well-defined compliance voltage that helps determine the maximum values of RBRIDGE and RBIAS. The integrated PGA typically requires a common-mode voltage of half the analog supply voltage (AVDD / 2) to maximize the amplifier gain and keep the PGA output voltage within the linear range of operation. This sets a target VCM(Bridge) of AVDD / 2, which helps determine if an RBIAS resistor is necessary and, if it is, the required value.

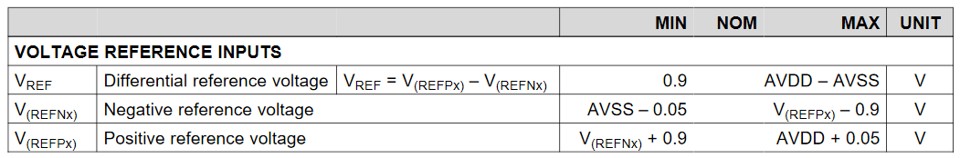

For example, the 24-bit ADS1261 integrates all of these necessary features. Figure 6-8 shows the differential and absolute VREF voltage requirements for the ADS1261. Using a unipolar supply such that AVDD = 5 V and AVSS = 0 V, Figure 6-8 shows that VREF must be between 0.9 V and 5 V. This bounds the possible values of VBRIDGE. Additionally, the absolute voltage on VREFN can extend down to AVSS while the absolute voltage on VREFP can extend up to AVDD. This wide absolute VREF voltage range typically does not limit the selection of the other system components, though this should always be verified in each design.

Figure 6-8 ADS1261 VREF Operating Conditions

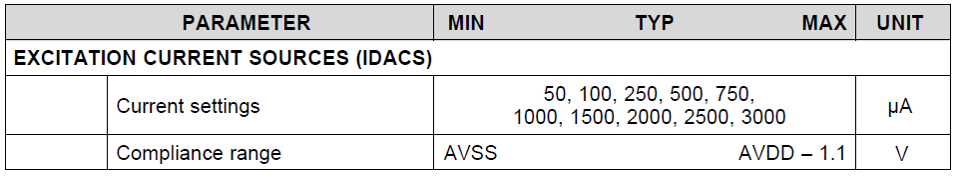

Figure 6-8 ADS1261 VREF Operating ConditionsFigure 6-9 shows the available IDAC current settings and the compliance voltage for the ADS1261. An IDAC integrated into a precision ADC requires some headroom with AVDD to maintain the current magnitude. Since AVDD = 5 V ±5% for the ADS1261, the IDAC compliance voltage = AVDD – 1.1 V = 3.9 V. This value sets an upper bound on RBRIDGE + RBIAS as well as IIDAC.

Figure 6-9 ADS1261 IDAC Current Settings and Compliance Voltage

Figure 6-9 ADS1261 IDAC Current Settings and Compliance VoltageTo determine if VCM(Bridge) is within the PGA linear region of operation, Section 6.3.4 introduced the ADS1261 Excel Calculator that plots the PGA output to reveal if the input parameters are valid. It is also possible to select a desired target value such as VCM(Bridge) = AVDD / 2 and design the rest of the system around this common-mode voltage. After the specific ADC operating conditions have been defined, begin selecting the remaining system component values.

For this example, assume that RBRIDGE can be any one of four common bridge resistance values: 120 Ω, 350 Ω, 1 kΩ, or 3.5 kΩ. Then, use the ADS1261 IDAC values given in Figure 6-9 to determine VBRIDGE using the equation in Table 6-19. Table 6-12 calculates VBRIDGE for all possible combinations of IIDAC and RBRIDGE.

RBRIDGE (Ω) | IIDAC (μA) | |||||||||

50 | 100 | 250 | 500 | 750 | 1000 | 1500 | 2000 | 2500 | 3000 | |

120 | 0.006 | 0.012 | 0.030 | 0.060 | 0.090 | 0.120 | 0.180 | 0.240 | 0.300 | 0.360 |

350 | 0.018 | 0.035 | 0.088 | 0.175 | 0.263 | 0.350 | 0.525 | 0.700 | 0.875 | 1.050 |

1000 | 0.050 | 0.100 | 0.250 | 0.500 | 0.750 | 1.000 | 1.500 | 2.000 | 2.500 | 3.000 |

3500 | 0.175 | 0.350 | 0.875 | 1.750 | 2.625 | 3.500 | 5.250 | 7.000 | 8.750 | 10.500 |

Assuming no lead resistance, VBRIDGE = VREF. Therefore, Table 6-12 also highlights in green all possible system combinations where 0.9 V < VBRIDGE < 5 V, as per the ADS1261 requirements. Out of the 40 possible combinations, only nine remain.

Next, determine the possible values of RBIAS for each of the remaining nine combinations by choosing a value for VCM(Bridge). This example uses VCM(Bridge) = AVDD / 2, though other voltages are possible. Always ensure that the PGA common-mode and absolute voltage requirements are met for the target gain value.

As per Table 6-19, VCM(Bridge) = VBRIDGE / 2 + VBIAS, VBRIDGE = IIDAC • RBRIDGE, and VBIAS = IIDAC • RBIAS. Rearranging these equations helps determine RBIAS in terms of IIDAC, RBRIDGE, and AVDD, as per Equation 60:

One important detail about Equation 60 is that RBIAS can be 0 Ω such that the VCM(Bridge) equation simplifies to VCM(Bridge) = VBRIDGE / 2. In other words, it is possible to eliminate the RBIAS resistor as long as the ADC and system requirements can still be met. However, this example assumes an RBIAS resistor is necessary. In either case, the next step is to calculate VCOMPLIANCE using the equation from Table 6-19. Table 6-13 reports the calculated values of RBIAS and VCOMPLIANCE for each of the nine valid combinations in Table 6-12. Additionally, Table 6-13 highlights in green the values of VCOMPLIANCE that are within the ADS1261 IDAC compliance voltage of 3.9 V.

| RBRIDGE (Ω) | IIDAC (μA) | RBIAS (Ω) | VCOMPLIANCE (V) |

|---|---|---|---|

| 350 | 3000 | 658 | 3.025 |

| 1000 | 1000 | 2000 | 3.000 |

| 1500 | 1167 | 3.250 | |

| 2000 | 750 | 3.500 | |

| 2500 | 500 | 3.750 | |

| 3000 | 333 | 4.000 | |

| 3500 | 500 | 3250 | 3.375 |

| 750 | 1583 | 3.813 | |

| 1000 | 750 | 4.250 |

As Table 6-13 shows, seven of the original nine combinations are within the IDAC 3.9-V compliance voltage specified by the ADS1261. Any of these options could be used in the final design. For example, Figure 6-10 shows a system where RBRIDGE = 1 kΩ, RBIAS = 2 kΩ, and IIDAC = 1 mA. The IDAC current path is highlighted in red and the resulting system voltages are highlighted in blue.

Figure 6-10 Current-Excited Bridge Measurement Using RBRIDGE = 1 kΩ, RBIAS = 2 kΩ, and IIDAC = 1 mA

Figure 6-10 Current-Excited Bridge Measurement Using RBRIDGE = 1 kΩ, RBIAS = 2 kΩ, and IIDAC = 1 mAOne important result from Figure 6-10 that was not previously-discussed is that VBRIDGE = VREF = 1 V. In other words, the current-excited system has VEXCITATION = 1 V, while a voltage-excited system typically has VEXCITATION ≥ 5 V. Assuming each bridge has the same sensitivity, the output voltage from the current-excited bridge is 20% compared to the voltage-excited bridge. This can reduce the dynamic range of the system to an unacceptable level given the system noise targets. In this case, repeat the design process using a different ADC, a discrete current source, or a wider range of RBRIDGE values.

After the system configuration has been selected, identify the maximum differential output voltage of the bridge, VOUT(Bridge Max), using the equation from Table 6-19 and parameters from Table 6-18. This value provides the maximum output voltage possible from the bridge under normal operating conditions and corresponds to the maximum load that can be applied to the bridge, Load(Bridge Max). If the system does not use the entire output range of the bridge, VOUT(System Max) defines the maximum differential output signal that is applied to a specific system and Load(System Max) is the corresponding maximum load. For example, if VOUT(Bridge Max) corresponds to Load(Bridge Max) = 5 kg, but the system specifications only require that Load(System Max) = 2.5 kg, then VOUT(System Max) is given by Equation 61:

Note that if Load(System Max) = Load(Bridge Max), then VOUT(System Max) = VOUT(Bridge Max).

After VOUT(System Max) has been determined, choose the corresponding gain value for the ADC PGA. The maximum gain value is limited by the previously-selected value of VCM(Bridge) and the ADC FSR. The amplifier gain should be the largest allowable value that keeps the PGA output voltage within the linear range of operation given the VCM(Bridge) voltage and is less than the ADC FSR. In some cases it is not possible to choose an amplifier gain that uses the entire ADC FSR. While this is often an acceptable tradeoff between resolution and ease-of-use, care should be taken to ensure that all system requirements are still met when the ADC FSR cannot be maximized.

Finally, follow the instructions in Section 5.5 if calibration is required.