SBAU412A November 2022 – May 2024 AFE7900 , AFE7903 , AFE7906 , AFE7920 , AFE7921 , AFE7950

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Prerequisites

- 3 Typical Bare-Metal Design Flow

- 4 Background

- 5 Add Microblaze and SPI IP for Use in Vitis for Embedded Development

- 6 Create New Platforms in Vitis

- 7 Create New Application Projects in Vitis

- 8 Build Application Projects

- 9 Generate SPI Log for AFE79xx EVM

- 10AFE79xxEVM Board Modifications

- 11Configure the AXI GPIO

- 12Configure the AXI SPI

- 13Set Up and Power on Hardware

- 14Set up ZCU102 Board Interface for VADJ_FMC

- 15Debug Application Projects and Set up Vitis Serial Terminal

- 16Execute the Application

- 17Revision History

14 Set up ZCU102 Board Interface for VADJ_FMC

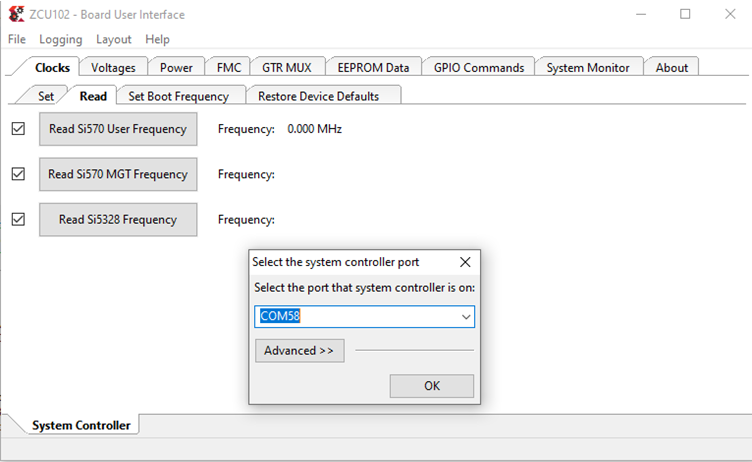

To set the ZCU102 board interface for VADJ_FMC, follow these steps:

- Execute the ZCU102-Board User Interface software (available for download from Xilinx.com).

- Select the appropriate COM Port

to enable communication between the onboard MSP430 of the ZCU102 and the PC.

This software is required to turn on the FMC_AUX supply of 1.8V for the FMC bank

of FPGA (see Figure 14-1).

Figure 14-1 ZCU102 Board User

Interface

Figure 14-1 ZCU102 Board User

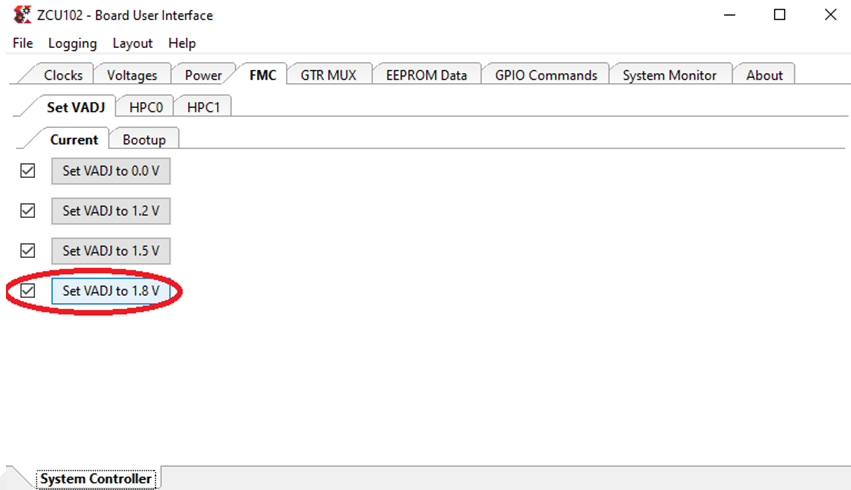

Interface - Select the Set VADJ to

1.8V check box (see Figure 14-2).

Figure 14-2 Setting VADJ

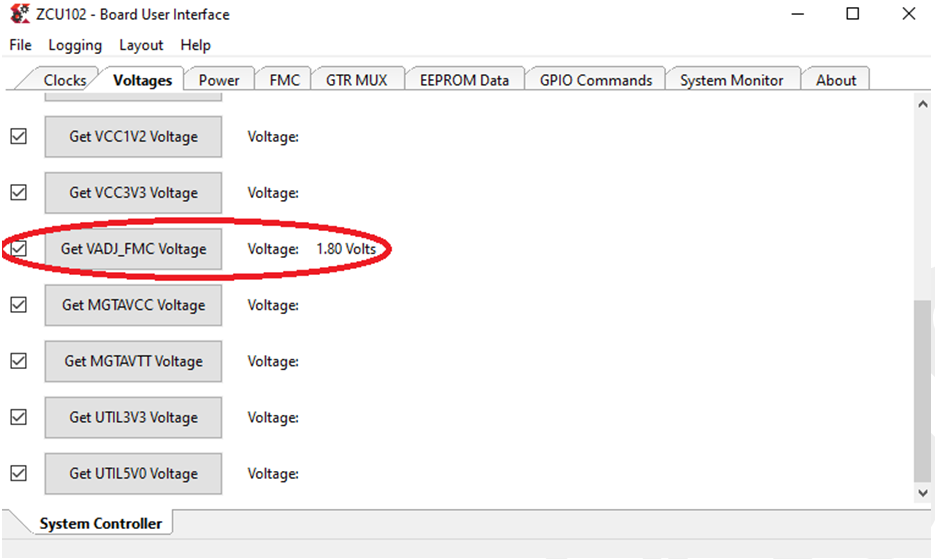

Figure 14-2 Setting VADJ - Confirm

the same by reading the VADJ_FMC voltage. The voltage value must be 1.80V (see

Figure 14-3).

Figure 14-3 VADJ_FMC

Voltage

Figure 14-3 VADJ_FMC

Voltage