SLUAAE9B May 2022 – November 2023 TPS62860 , TPS62861 , TPS62864 , TPS62866 , TPS62868 , TPS62869 , TPS62870 , TPS62870-Q1 , TPS62871 , TPS62871-Q1 , TPS62872 , TPS62872-Q1 , TPS62873 , TPS62873-Q1 , TPS62874-Q1 , TPS62875-Q1 , TPS62876-Q1 , TPS62877-Q1 , TPS6287B10 , TPS6287B25 , TPSM8287A06 , TPSM8287A12 , TPSM8287A15

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Smart Routing and Tiny IC Packages

- 3 Selectable Forced-PWM/PSM operation

- 4 Dynamic Output Voltage Adjustment During Operation

- 5 Thermal Considerations

- 6 Droop Compensation

- 7 Step-Down Converter with an I2C Interface Selection Table

- 8 Conclusion

- 9 References

- 10Revision History

4 Dynamic Output Voltage Adjustment During Operation

The I2C interface allows adjustment of the output voltage during operation. One or more I2C registers usually sets the output voltage, and these can be directly re-written during operation. Some devices also contain VID or VSEL pins, which switch between two or more output voltages. In this case, the registers can still be re-written as needed during operation, or can be written once to specific operating voltages.

For example, LPDDR5 DRAMs VDDQ rail can be set to either 0.5 V or 0.3 V. This voltage change is accomplished by either rewriting the I²C register to change the output voltage or using the VID pin to change to a different I²C register with its different output voltage. LPDDR5 DRAMs provide additional power-savings compared to previous generations. In an idle condition when the LPDDR5 DRAM is in a low-power operating state, the memory controller can reduce both the supply voltage and frequency of operation using the dynamic voltage and frequency scaling VDDQ (DVFSQ) feature of the LPDDR5 DRAM.

Figure 4-1 shows a typical block diagram for powering LPDDR5 memory, with dynamic output voltage adjustment on the VDDQ rail.

Figure 4-1 The TPS62869 Powers all Rails on LPDDR5 DRAM with Dynamic Output Voltage Adjustment on the VDDQ Rail

Figure 4-1 The TPS62869 Powers all Rails on LPDDR5 DRAM with Dynamic Output Voltage Adjustment on the VDDQ RailThe system design determines if dual rail mode will be used for additional power savings. Unlike the VDDQ rail – which can be changed dynamically – VDD2H/L are always operated at fixed voltages, regardless of whether single rail or dual rail mode is used.

TPS62869 provides different voltage ramp speeds to enable system engineers to select the right conditions for a DVFSQ low-to-high transition. For instance, if a fast response is required when VDDQ is returned to a 0.5 V nominal level for high-speed operations, TPS62869 can adapt its Voltage Ramp Speed from 1mV/us up to 20mV/us.

Table 4-1 shows the maximum VDDQ Ramp Rates for a DVFSQ transition.

| VDDQ Slew Rate | Max Value | Units |

|---|---|---|

| Fast response mode (high current) | 20 | mV/us |

| Normal operation (default) | 4,8 | mV/us |

Furthermore, operating parameters for example, Forced PWM mode during output voltage change can be enabled to address strict timing requirements during the Low-to-High transition of VDDQ. This provides a fast transition in a lower operating state and can prevent the slow discharge of the output stage to limit the voltage ramp speed in a low load condition.

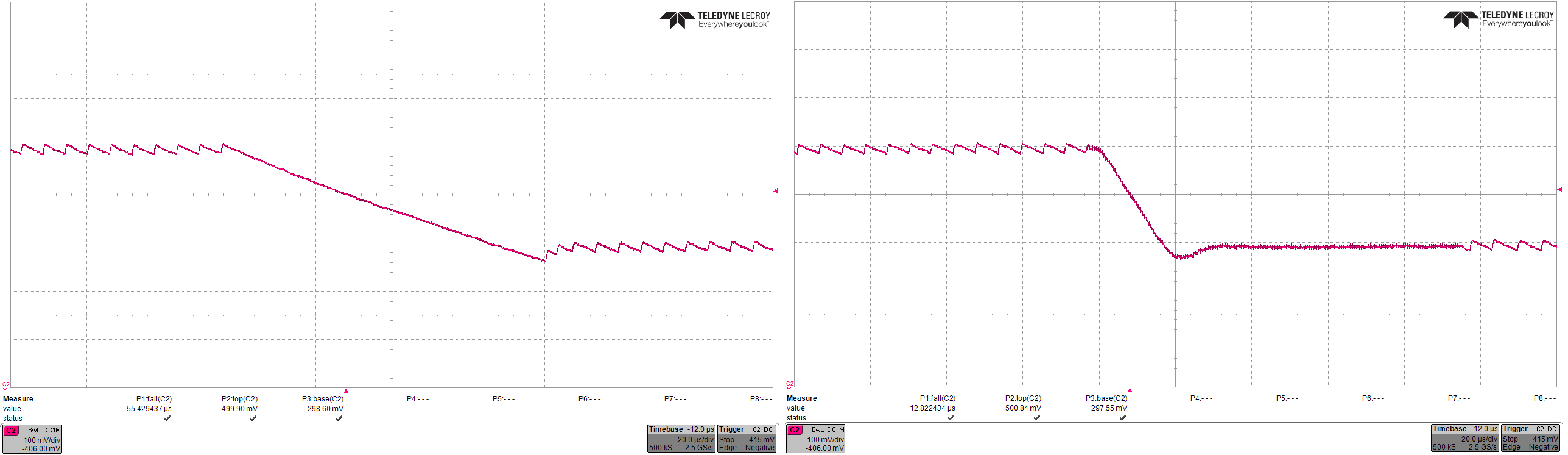

Figure 4-2 shows an example of a 0.5 V to 0.3 V transition with and without Forced PWM mode during output voltage change at a 100 mA load condition.

Figure 4-2 0.5 V to 0.3 V Output Transition in a 20 mV/us

Slew Rate, IOUT=100mA Without FPWM During Change Enabled (left) and With

(right)

Figure 4-2 0.5 V to 0.3 V Output Transition in a 20 mV/us

Slew Rate, IOUT=100mA Without FPWM During Change Enabled (left) and With

(right)