SPRACM3E August 2021 – January 2023 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- Using the Fast Serial Interface (FSI) With Multiple Devices in an Application

- Trademarks

- 1Introduction to the FSI Module

- 2FSI Applications

- 3Handshake Mechanism

- 4Sending and Receiving FSI Data Frames

- 5Daisy-Chain Topology Tests

- 6Star Topology Tests

-

7Event Synchronization Over FSI

- 7.1 Introduction

- 7.2 C2000Ware FSI EPWM Sync Examples

- 7.3 Additional Tips and Usage of FSI Event Sync

- 8References

- 9Revision History

7.1.3 Functional Overview of FSI Event Sync Mechanism

To showcase the event sync mechanism, a particular case of EPWM sync in a daisy chain network has been taken in the example provided. The task is to ensure that all the EPWM signals of respective node devices remain synchronized with the EPWM signal of lead device. In general, any event can be synchronized using the FSI event sync configuration as per the application. Since all the control applications use EPWM time base, it is sufficient to keep the EPWM of all the node devices synchronized. Typically, activities relating to ADC, comparator or any event function in the node device are based on EPWM event or triggers.

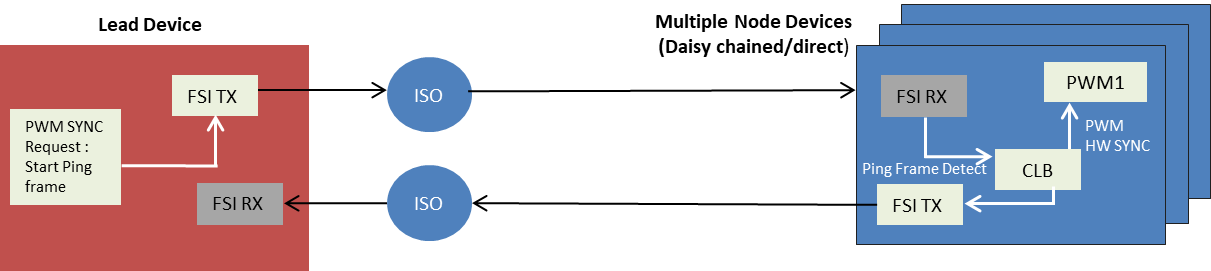

The functioning of the PWM Sync over FSI can be understood considering one lead device and two node devices as shown in Figure 7-3. In the daisy chain network, FSI communication link is first established using the handshake mechanism as described in Section 3.1.

Figure 7-3 Daisy-Chain Communication

Block Diagram

Figure 7-3 Daisy-Chain Communication

Block DiagramThe ping packet, being the shortest possible FSI packet in terms of length, is sent by the lead device to all node devices at regular time intervals to verify the communication link and signal the node devices to synchronize with the lead device. The lead device FSITX trigger is controlled by the local EPWM compare event configured by the user. On rising or falling edge of the EPWM as configured, FSITX is triggered to send the ping packet to node devices. The counter compare value for the EPWM signal depends on the number of devices in the chain, distance between devices, and so forth, which is to be configured as per the application by user.

As the ping packet sent by the lead device is received at a node, the FSI ping frame received signal (RX_PING_FRAME) generated at the node is connected internally to the Configurable Logic Block (CLB) module of the same node, as seen in Figure 7-3. The CLB routes the RX_PING_FRAME signal to immediately trigger the FSI TX ping forwarding to the next device in the chain. A configurable delay counter implemented inside CLB acts as a timer with period as ‘match’ value fed to the CLB and restarts counting on reaching the ‘match’ value. When CLB receives the RX_PING_FRAME signal, the counter starts counting and on reaching the ‘match’ value, it generates an EPWM sync-in signal for the EPWM module of that node. In other words, the ‘match’ value helps to provide a calculated delay from the time a ping packet signal is received at the node to the time when the PWM sync-in signal is generated at the local node device. Ideally, EPWM sync-in signal for every node will be generated at the same time and aligned with the lead device EPWM counter equals to zero event. A functional representation of process flow within a node device is showcased in Figure 7-4.

The PWM signals would not have remained synchronized over time since the oscillator clock cannot be identical for every device. The node devices in the chain experience the uncertainties in the form of jitter present in their respective EPWM signals as shown in Figure 7-5. The last device in the chain will experience the highest amount of jitter for a daisy-chain configuration because of the additive jitter from packet forwarding and synchronizer deviations at each device, discussed in Section 7.2.5. This way of utilizing the ping packet to generate the EPWM sync-in signal would keep the EPWMs synchronized for all devices in the chain.

Depending on the node in the daisy-chain network, the delay needed in generating the EPWM signal is different. For example, for node 1, the ping packet will be received in a short time and for 8th node, the time taken for the ping packet signal to reach it will be higher due to forwarding and propagation delay, so the CLB counter count (‘match’ value) for node 1 has to be higher to ensure more delay in generation of EPWM sync-in signal than the count for node 8 to adjust for the transmission delay. The ‘match’ value to be fed to the counter has to be set by the user and configured in the CLB configuration block, which is dependent on the isolation barrier used, the distance between the nodes and the device in operation. Approximate value for ‘match’ count to start has been provided in the project source file introduction section.