SPRACY1 May 2021 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P550SJ , TMS320F28P559SJ-Q1 , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

2.2 Simultaneous Writes to Registers Between Modules

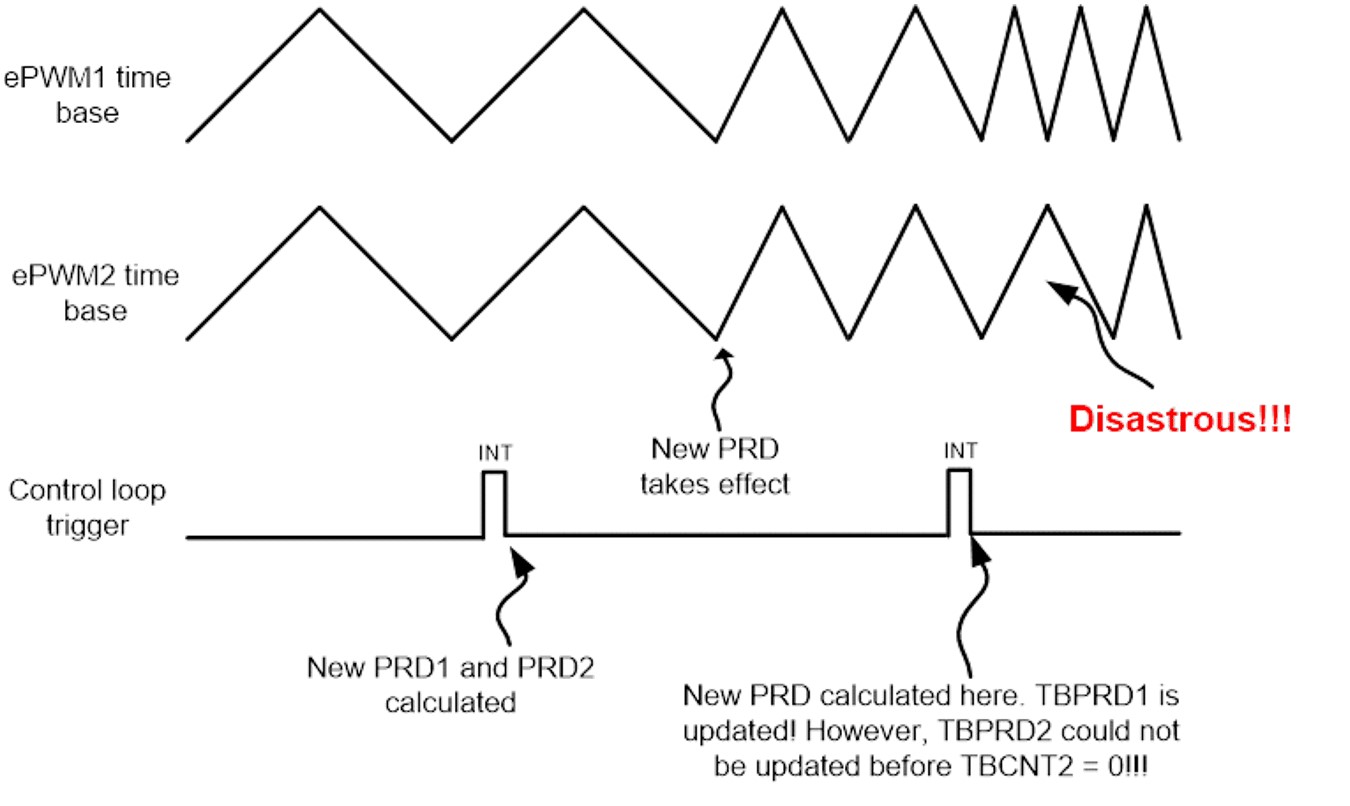

In variable frequency applications, like LLC, the control ISR, where the period and compare registers will be updated, runs at a fixed frequency, which is asynchronous to the PWM switching frequency. Thus, it may happen that the ISR is triggered at a point in time close to the end of the switching cycle. If this is the case, it is possible that some part of the ISR code that updates the ePWM registers executes before the end of the cycle, while the remainder of the code executes in the next switching cycle. As shown in Figure 2-4, the period register for ePWM1 gets updated before the end of the switching cycle, while the period register for ePWM2 does not get updated on time. As a result, ePWM2 operates with the old PWM frequency, while ePWM1 operates with the new frequency, which can be disastrous for the power stage.

Figure 2-4 Potential Issue if the ISR Occurs

at the Switching Cycle Boundary

Figure 2-4 Potential Issue if the ISR Occurs

at the Switching Cycle Boundary In order to update the shadow registers of different ePWM modules as soon as possible, new types of ePWM provide register linking scheme, with the link register EPWMXLINK. This prevents situations where a SyncIn pulse forces a shadow to active load of these registers before all registers are updated among ePWM modules. TBPRD:TBPRDHR, CMPA:CMPAHR, CMPB:CMPBHR, CMPC, and CMPD registers can be enabled with EPWMXLINK. The corresponding register will simultaneously be written with the same value which is written to the register of the ePWM module being linked to.

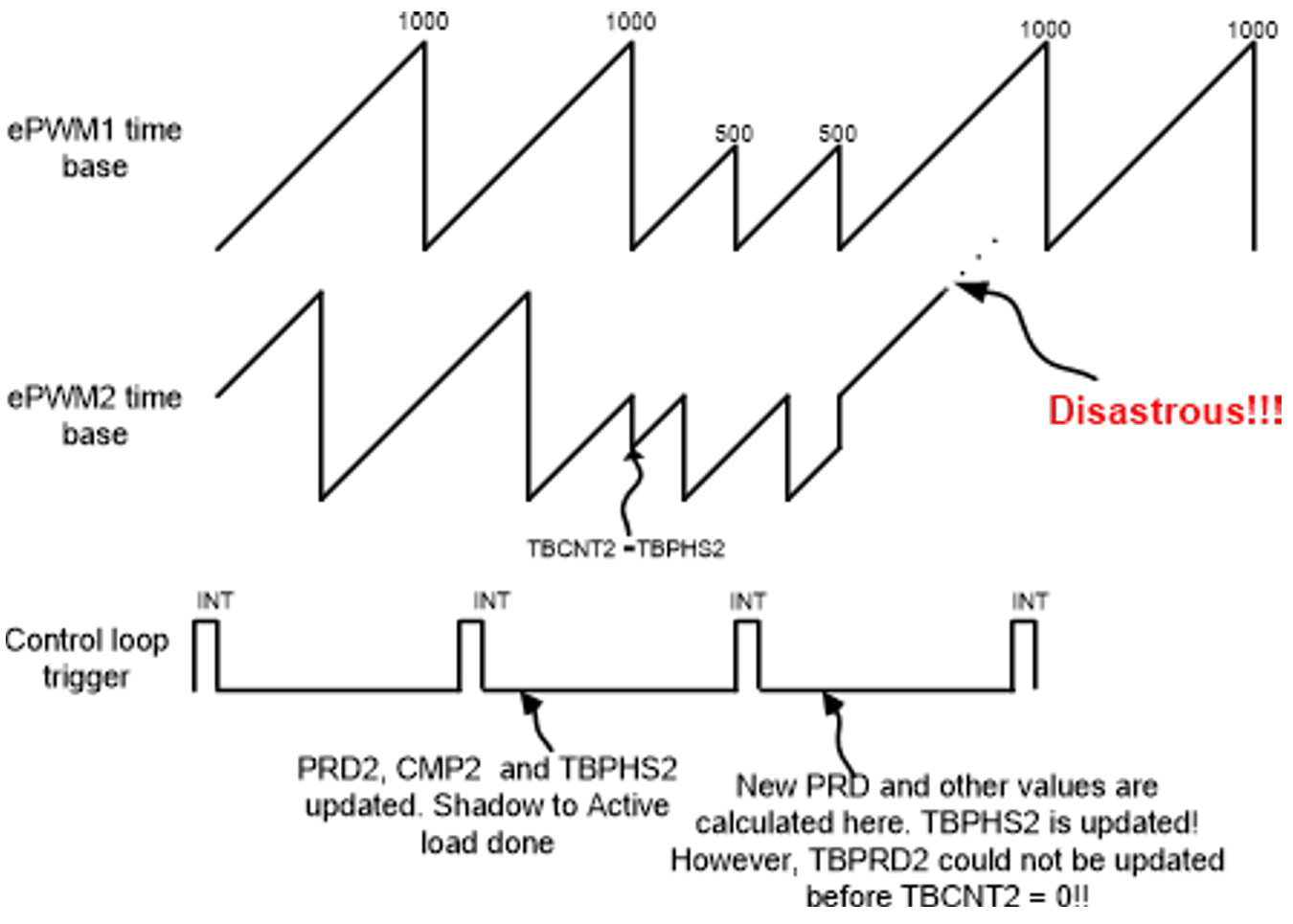

With the simultaneous write feature, the same register among different ePWM modules can be ensured to be updated always at the same time. However, since different shadow registers within the same ePWM module are still required to be updated in software manually one by one, it might happen that not all the ePWM registers are updated before the shadow to active load event. One disastrous result might occur as shown in Figure 2-5.

Figure 2-5 Disastrous Result When Different

Registers are not Updated Simultaneously

Figure 2-5 Disastrous Result When Different

Registers are not Updated Simultaneously