SPRADB1 September 2023 ADS127L11 , ADS127L21 , AM2434

1 Introduction

Sensors are linked via an analog front-end (AFE) to facilitate signal conditioning and bias voltage adjustments for sensor data. In the case of IEPE sensors, which produce low voltages, amplification is necessary prior to Analog-to-Digital Conversion (ADC) for capturing sensor samples. These samples are subsequently made accessible to a microprocessor for further signal processing.

A significant technical challenge arises when aiming to synchronize and collect data from four parallel ADCs over a serial interface. This is due to the requirement of capturing data from four individual lines while utilizing the serial capabilities of the microcontroller's peripherals, such as the Serial Peripheral Interface (SPI). Addressing this challenge necessitates a microcontroller that supports four SPI data input lines, or involves additional technical complexities like external hardware incorporation or ADC daisy chaining. However, these solutions can hinder SPI communication speed for reading ADC samples or result in increased Bill of Materials (BOM) costs.

This application note explains the microprocessor's role in interfacing with these four ADC data streams and outlines how to parallelly connect the SPI data lines of all four ADCs to the microprocessor. This configuration enables rapid retrieval of ADC samples. The SPI interface is implemented utilizing Sitara's Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS), which empowers the incorporation of FPGA-like functionality within a real-time core on the MCU chip. Subsequently, the ADC sample buffers/bins are processed on the MCU using Fast Fourier Transformation (FFT), and the results are transmitted via JSON/MQTT protocols over a single pair Ethernet connection to an SPE gateway. This gateway facilitates the visualization and analysis of vibration sensor samples.

The described use case facilitates predictive maintenance by allowing the identification of motor, generator, and gearbox degradation during operation. This timely recognition permits the scheduling of maintenance before system failure occurs. As a result, maintenance costs are minimized, and the risk of unexpected machinery breakdowns is mitigated.

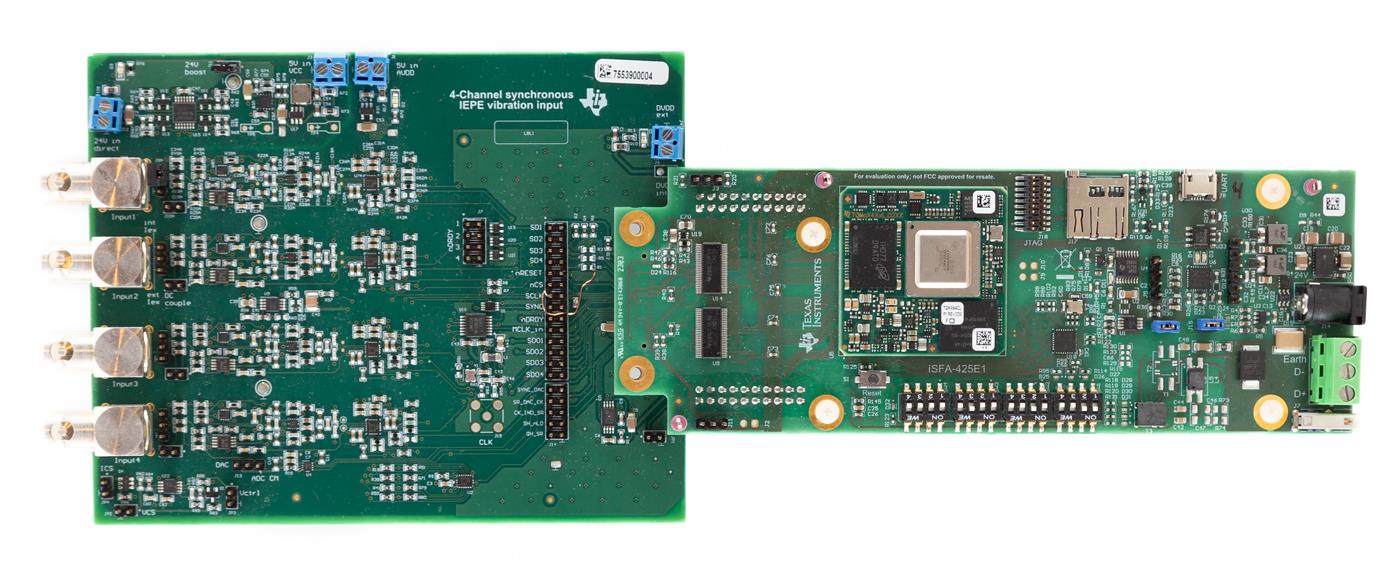

Figure 1-1 TIDA-010249 and TIDA-010261 EVMs Utilizing the Multi-Channel SPI

Figure 1-1 illustrates the configuration of the TIDA-010249 and TIDA-010261 Evaluation Modules (EVMs) employing the multi-channel SPI interface. The TIDA-010249 EVM comprises the four-channel ADCs, while the TIDA-010261 EVM features the AM243x microprocessor equipped with ARM Cortex R5F and PRU-ICSSG. The interconnection of these components forms the foundation for achieving synchronized ADC data acquisition and high-speed communication with the microprocessor for subsequent signal processing.