SPRUIT1B May 2020 – November 2020

- Trademarks

- 1Introduction

- 2GESI Expansion Board Overview

- 3GESI Expansion Board - User Setup/Configuration

- 4GESI Expansion Board Hardware Architecture

- A Interface Mapping

- B GESI Board GPIO Mapping

- C I2C Address Mapping

- D Revision History

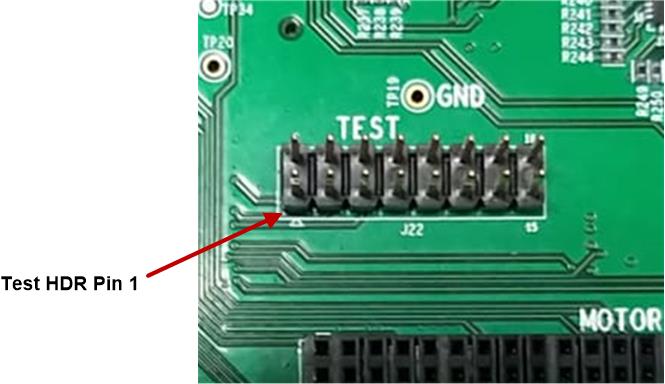

4.12 Test Header

Table 4-10 contains the pin out details of Test header. Test Header on GESI Board is shown in Figure 4-19.

Table 4-10 Pin Outs of J22 (Test Header)

Connector

| J22 Connector Pin Outs | |||

|---|---|---|---|

| Pin | Net Name | Pin | Net Name |

| 1 | TH_EHRPWM0_SYNCI | 9 | EHRPWM0_B |

| 2 | EHRPWM1_B | 10 | EHRPWM_TZn_IN2 |

| 3 | TH_EHRPWM0_SYNCO | 11 | EHRPWM1_A |

| 4 | EHRPWM_TZn_IN1 | 12 | TH_UART4_RTSn |

| 5 | TH_EHRPWM_TZn_IN0 | 13 | TH_UART4_TXD |

| 6 | EHRPWM2_A | 14 | TH_UART4_RXD |

| 7 | EHRPWM0_A | 15 | TH_UART4_CTSn |

| 8 | EHRPWM2_B | 16 | DGND |

Figure 4-19 Test Header

Figure 4-19 Test Header