SPRUJ09D March 2022 – September 2023 AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1

- 1

- Abstract

- Trademarks

- 1Preface: Read This First

- 2Control Card Overview

- 3Board Setup

- 4Hardware Description

- 5References

- Revision History

- A E2 Design Changes

- B E1 HSEC Pinout Table

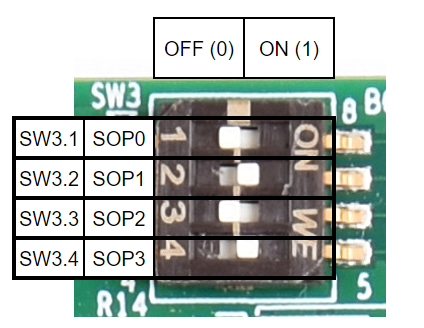

3.3 Boot Mode Selection

The bootmode for the AM263x is selected by a DIP switch (SW3) or the test automation header. The test automation header uses an I2C IO expansion buffer to drive the bootmode when PORz is toggled. The supported boot modes are as shown in Table 3-4.

Table 3-4 Supported Boot Modes

| Boot Mode/Peripheral | Boot Media/Host | Notes |

|---|---|---|

| QSPI (4S) - Quad Read Mode | QSPI Flash | Download and boot SBL from QSPI flash in quad read mode. Attempt Primary SBL, followed by Secondary SBL if primary loading fails. |

| UART | External Host | Download and boot SBL from UART. Device is expected to get SBL from UART. Device supports the XMODEM protocol for download over UART. |

| QSPI (1S) - Single Read Mode | QSPI Flash | Download and boot SBL from QSPI flash in single read mode. Attempt Primary SBL,followed by Secondary SBL if primary loading fails. |

| QSPI (4S) - Quad Read UART Fallback Mode | QSPI Flash / External Host | Download and boot SBL from QSPI flash in quad read mode. Attempt Primary SBL, followed by Secondary SBL if primary loading fails. If Secondary SBL also fails then boot from external host via UART interface. |

| QSPI (1S) - Single Read UART Fallback Mode | QSPI Flash / External Host | Download and boot SBL from QSPI flash in single read mode. Attempt Primary SBL, followed by Secondary SBL if primary loading fails. If Secondary SBL also fails then boot from external host via UART interface. |

| DevBoot | N/A | No SBL. Used for development purposes only. |

Figure 3-7 SW3 Switch Positions

Figure 3-7 SW3 Switch PositionsTable 3-5 Boot-Mode Selection

Table

| Boot Mode | SPI0_D0_pad (SOP3) | SPI0_CLK_pad (SOP2) | QSPI_D1 (SOP1) | QSPI_D0 (SOP0) |

|---|---|---|---|---|

| QSPI (4S) - Quad Read Mode | 0 | 0 | 0 | 0 |

| UART | 0 | 0 | 0 | 1 |

| QSPI (1S) - Single Read Mode | 0 | 0 | 1 | 0 |

| QSPI (4S) - Quad Read UART Fallback Mode | 0 | 1 | 0 | 0 |

| QSPI (1S) - Single Read UART Fallback Mode | 0 | 1 | 0 | 1 |

| DevBoot | 1 | 0 | 1 | 1 |

| Unsupported Boot Mode | All other combinations not defined above | |||