SSZT978 august 2017 TPS543C20

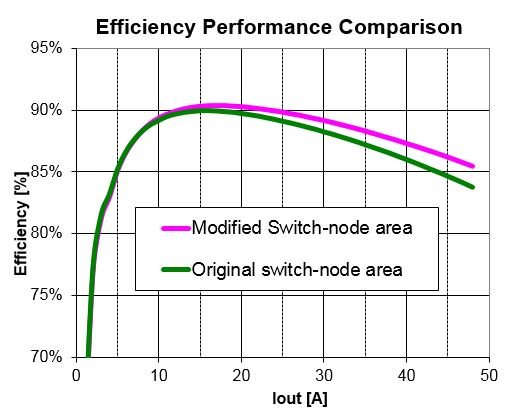

The demand for energy has gone up significantly but overall solution size continues to shrink. To adapt, you can decrease the size of a buck converter but it must still be able to handle the increasing power consumption in the electronic system. Optimizing the layout to increase the efficiency of the buck converter will result in less electricity needed to power the system.

Many electronic systems require several buck converters to supply power to different rails. Some systems may need two converters or more to power a single rail with a high current demand. The challenge of designing a smaller buck converter to satisfy this demand becomes a daunting task, but it is possible.

New technologies and processes are now in place that enable integrated circuit (IC) designers to design buck converters that can handle up to 40A for a single output. However, this capability introduces other issues. One is the printed circuit board (PCB) layout. You can design the best buck converter and power stage with space constraints in mind, but if you fail to lay out the PCB correctly, all will be lost.

With the current at 40A per output, PCB layout is crucial in regards to heat dissipation and efficiency. If you don’t optimize the board design, the DC loss at 40A can increase greatly due to the higher resistance of the copper-poured area. So in this post, I’ll explain the importance of the copper-poured area, via size and quantity, and current loop path on a multi-layer circuit board.

Copper Poured Area

Figure 1 Modified Switch Node Area Showing a Size Increase vs. Original Switch Node Area

Figure 1 Modified Switch Node Area Showing a Size Increase vs. Original Switch Node AreaVia Size and Quantity

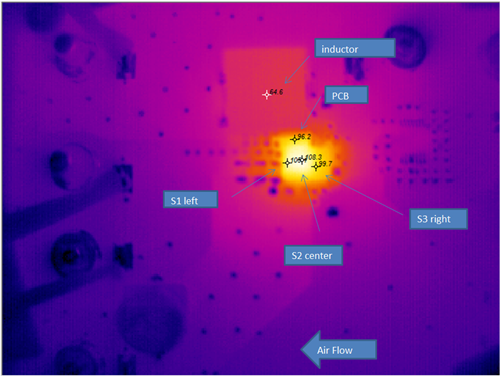

Figure 2 PCB with 11 Vias under the Thermal Pad

Figure 2 PCB with 11 Vias under the Thermal Pad*S2 (Site 2): Location of the Integrate FET on the IC

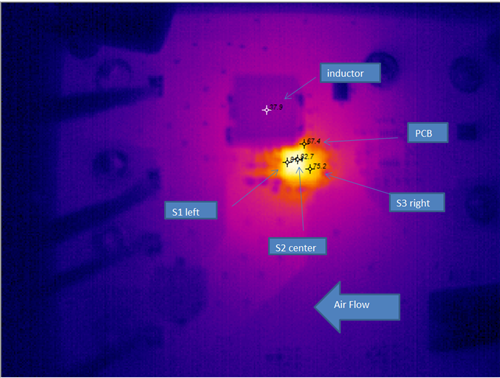

Figure 3 PCB with 35 Vias under the Thermal Pad

Figure 3 PCB with 35 Vias under the Thermal Pad