KOKT006 march 2023

3 액티브 클램프 레그 설계 고려 사항

PSFB에 액티브 스너버를 구현하면 변압기 권선 전류가 출력 인덕터 전류처럼 유효 듀티 사이클(Deff) 기간(TS)(0이 아닌 출력 권선 전압 기간) 동안 더 이상 단조적으로 상승하지 않습니다. 그 이유는 액티브 스너버 커패시터 에너지가 입력 측의 에너지 전달에만 의존하지 않고 출력 인덕터에 전원을 공급하는 데에도 참여하기 때문입니다. 입력 또는 변압기 권선 전류가 보통 피크 전류 감지에 사용되고, 더 높은 입력 또는 변압기 권선 전류가 반드시 더 큰 듀티 사이클을 나타내는 것이 아니기 때문에 비단조 전류 램프 특성은 피크 전류 모드 제어를 어렵게 만들 수 있습니다.

전류가 단조적으로 상승할 때 피크 전류 감지가 일어나도록 하려면, 반드시 전체 작동 전압 및 부하 범위에서 DeffTS가 전류-초 균형이 완료되는 지속 시간(DCSBTS)보다 항상 더 크도록 해야 합니다. 더 큰 Deff를 갖는 PSFB에 대해서는 높은 효율이 기대되기 때문에, PSFB는 일반적으로 Deff >> DCSB가 기대되는 중간-중부하에서 더 큰 Deff를 갖도록 설계합니다. 경부하에서 컨버터는 불연속 전도 모드에서 작동할 것으로 기대되며, 이 모드에서 Deff는 입력/출력 전압 조건이 같을 때 연속 보드 하에서의 Deff보다 더 작습니다. 경부하에서도 DeffTS를 DCSBTS보다 더 크게 유지하기 위해 부하 전류를 바탕으로 주파수 감소 제어를 구현했습니다.

DCSBTS의 지속 시간은 피크 전류 모드 제어에서 중요한 요소가 됩니다. 전류-초 균형을 완료하는 데 걸리는 시간이야 말로 이제 백만 달러짜리 질문이 되었습니다. 이 질문에 답하려면 액티브 클램프 레그를 통과하는 전류 흐름을 계산해야 합니다.

VCL이 항수이고 Lm = ∞라고 가정하면, 방정식 2은(는) 듀티 사이클 손실 기간(VSEC = 0이고 iSR1과 iSR2가 정류 중인 기간) 동안 정류기 전류 변동률을 다음과 같이 표시합니다.

여기서 VLr은 Lr에 걸친 전압입니다.

방정식 3은(는) 출력 인덕터 전류의 변동률을 계산합니다.

방정식 4은(는) 키르히호프(Kirchhoff)의 전류 법칙과 함께 방정식 2 및 방정식 3을(를) 사용해 액티브 클램프 전류의 변동률을 계산합니다.

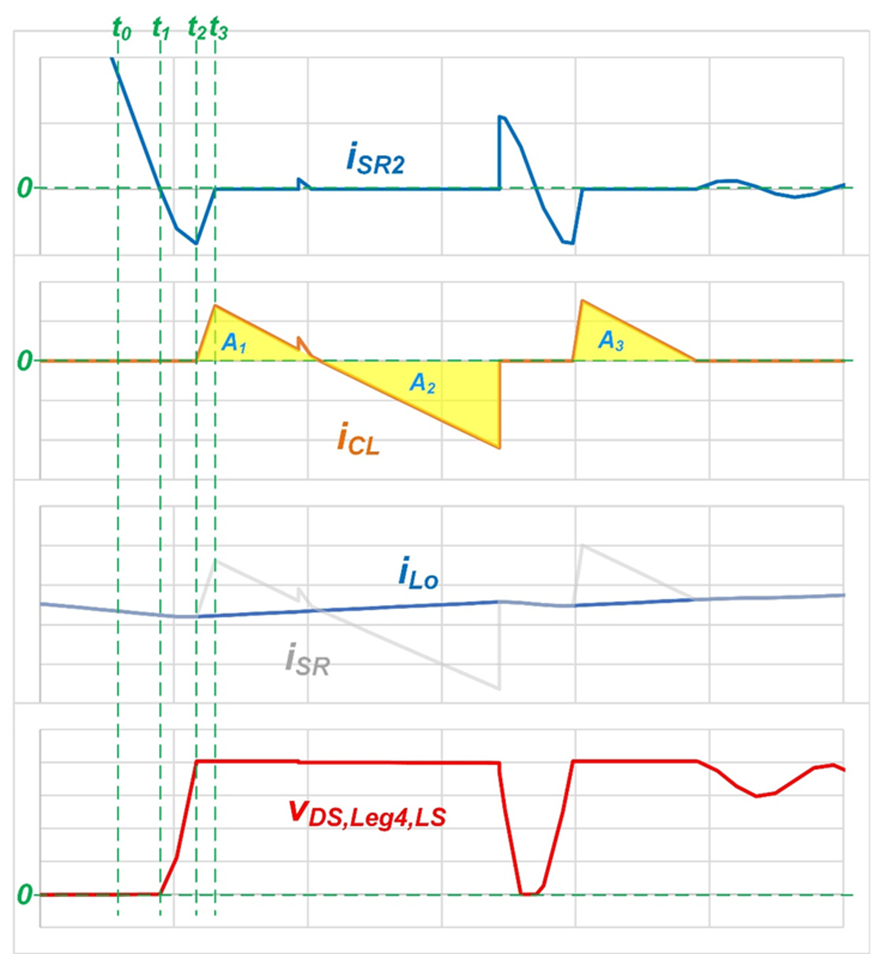

VCL ≈ VIN x NS/NP [3]이기 때문에 방정식 4에서 총 액티브 클램프 레그 전도 시간을 Δt로 적용하고 ΔiCL을 풀기만 하면 됩니다. 하지만, iCL RMS(제곱 평균 제곱근) 값을 계산하려면 iCL의 피크 값을 알아야 합니다. 그림 3에 나와 있는 것처럼, 시간 t2에서 iSEC = iLo(Coss to VCL 변동 후)이고 시간 t3에서 iSEC = iSR(CCL 변동 시작)인 경우 방정식 5은(는) iCL,peak를 다음과 같이 도출합니다.

그림 3 액티브 클램프 전류 전도 기간 주변의 주요 파형.

그림 3 액티브 클램프 전류 전도 기간 주변의 주요 파형.t2에서 방정식 6은(는) iSR2 값을 다음과 같이 도출합니다.

t0부터 t2까지 iSR2 전류 감소율이 같다고 가정하면, 방정식 7은(는) t2-t1 시간 기간을 다음과 같이 도출합니다.

CL은 전류-초 균형을 유지해야 하기 때문에, 면적 A1과 A3의 합계는 면적 A2와 같습니다.

방정식 7에서 보는 것처럼, SR Coss는 액티브 클램프 레그에서 피크 전류를 제어합니다. 낮은 Coss SR FET를 선택하는 경우, 액티브 클램프 레그 RMS 전류가 더 낮아지기 때문에 따라서 컨버터 효율을 개선하는 데 도움이 됩니다.

다음은 액티브 스너버가 있는 PSFB 컨버터를 설계할 때 사용할 수 있는 몇 가지 설계 지침입니다.

- QCL은 CCL 전류가 1차측으로 역류하는 것을 방지하려면 반드시 듀티 사이클 손실 기간 이후에 전원을 켜야 합니다.

- QCL은 바디 다이오드가 ZVS에 아직 전류를 전도하고 있는 동안은 계속 켠 상태를 유지해야 합니다.

- QCL 온타임이 길어질수록 VCL과 SR 전압 스트레스가 감소하지만 QCL RMS 전류는 증가합니다.

- SR Coss는 액티브 클램프 레그 RMS 전류를 줄여줄 뿐 아니라 SR 전압 스트레스를 줄이는 데에도 도움을 줍니다.

액티브 클램프 방법은 풀 브리지 정류기에만 한정된 것이 아니며, 전류 더블러[4] 또는 센터 탭형 정류기 등 다른 유형의 정류기에도 적용 가능합니다. 그림 4은(는) 센터 탭형 정류기에 액티브 클램프를 적용한 PSFB 컨버터를 보여주며, 액티브 클램프 레퍼런스 설계를 적용한 3kW 위상 전환 풀 브리지(전력 밀도 >270-W/in3)에서 구현한 것입니다.

그림 4 센터 탭형 정류기 상에 액티브 스너버가 있는 PSFB 컨버터.

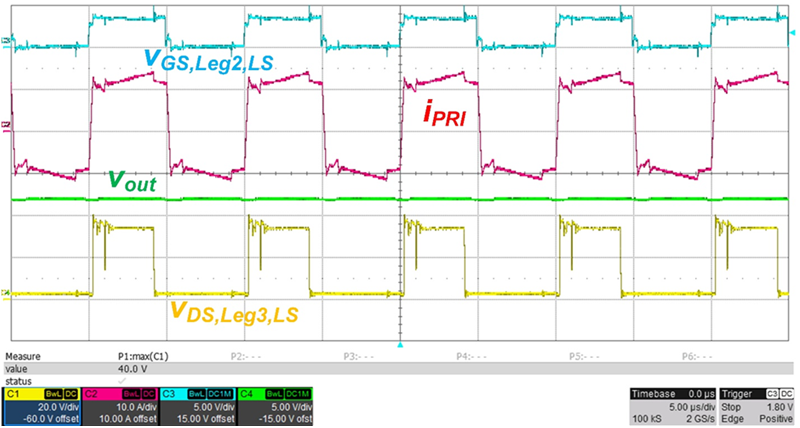

그림 4 센터 탭형 정류기 상에 액티브 스너버가 있는 PSFB 컨버터.그림 5에서 보다시피, 250A 부하 전류에서 클램핑 손실 거의 없이 듀얼 액티브 클램프 레그를 사용해 SR 전압 스트레스를 40V 미만으로 클램핑할 수 있습니다.

그림 5 12V/3kW 출력에서 센터 탭형 정류기와 액티브 스너버를 적용한 PSFB 컨버터의 안정적 상태 파형.

그림 5 12V/3kW 출력에서 센터 탭형 정류기와 액티브 스너버를 적용한 PSFB 컨버터의 안정적 상태 파형.