KOKT008 january 2023 TPS543B22 , TPS548A28 , TPS56121

4 전압 모드 제어 아키텍처

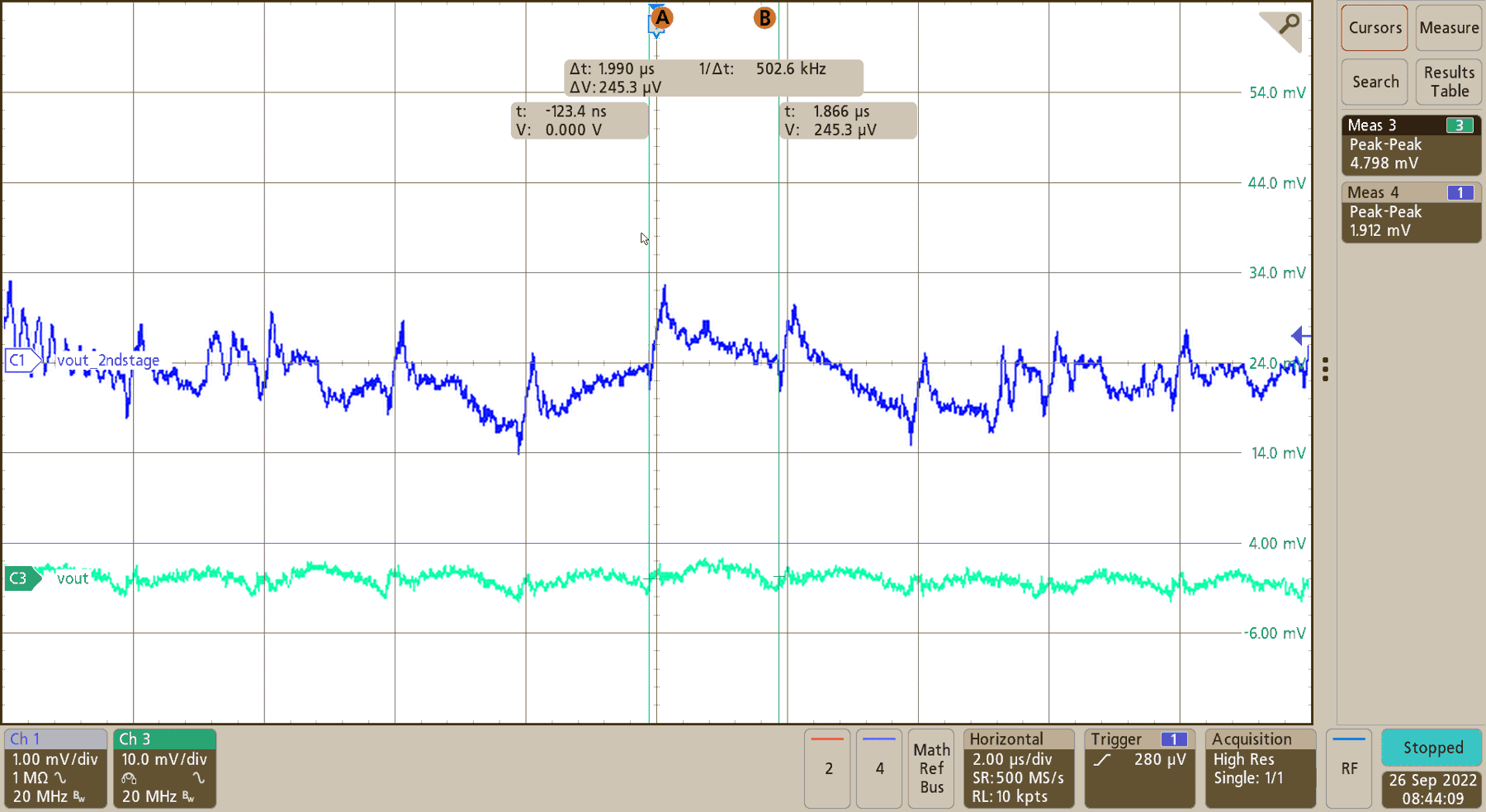

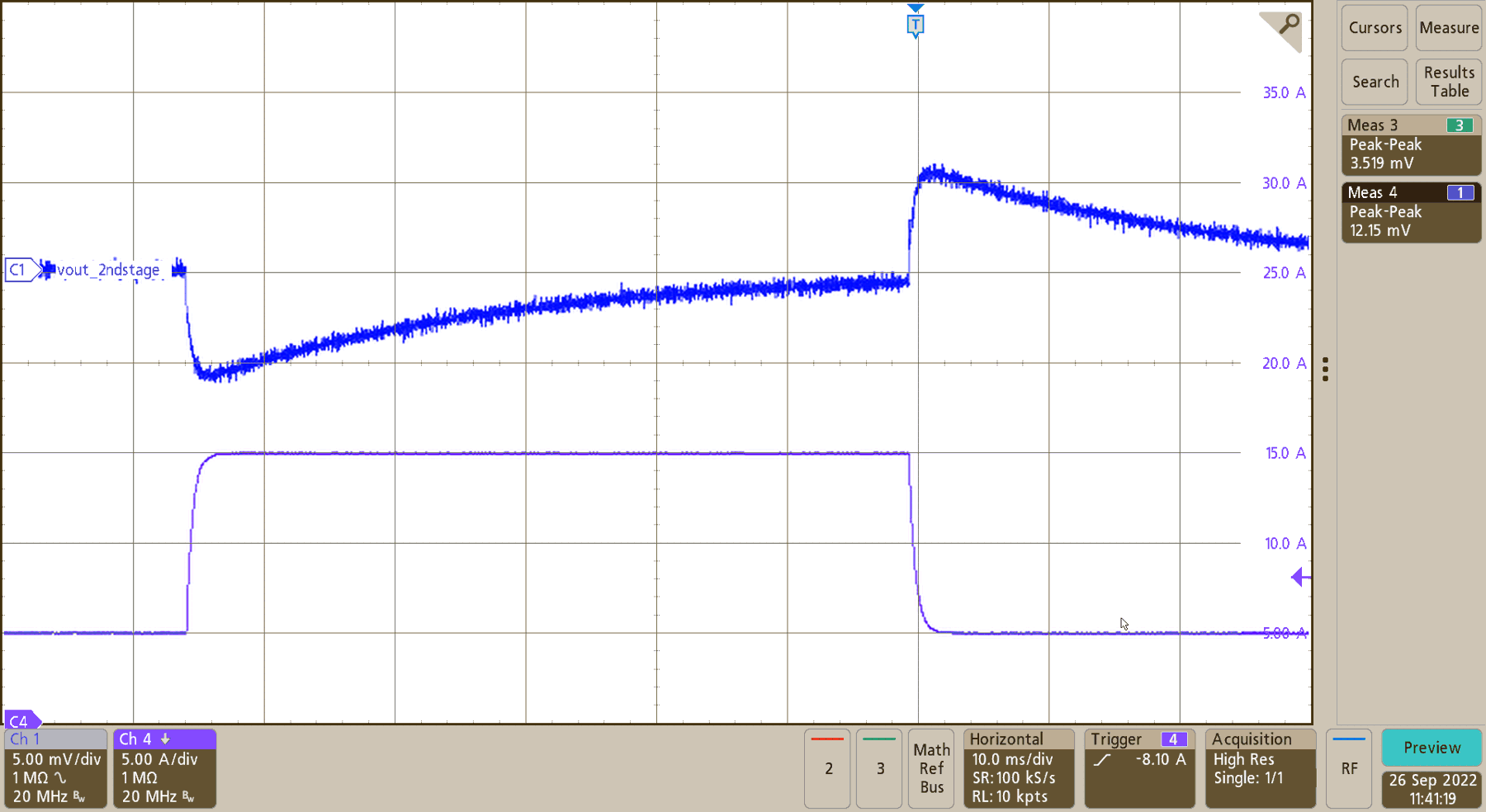

전압 모드 제어 아키텍처를 적용한 PWM(펄스 폭 변조)은 출력 전압과 레퍼런스 전압의 전압 오류 신호를 일정한 톱니파 램프 파형과 비교하는 방법으로 수행합니다. 램프는 오실레이터의 클록 신호에 의해 개시됩니다. TPS56121은 두 번째 단계 필터를 추가한 후 컨버터가 재보상되는 것을 허용하는 쌍극 전력계외부 보상을 처리하는 타입 3 보상을 사용합니다. 두 번째 단계 필터를 추가한 후 외부 저항기와 커패시터 값을 조정하기 때문에 안정성이 보장됩니다. 추가 필터 없는 출력 전압 피크 투 피크 리플은 4.8mV입니다. 추가 필터를 적용 시 출력 전압 리플은 (그림 2에서 보다시피) 1.9mV입니다. 이 경우 TPS56121 설계에는 안정성 보장을 위한 루프 보상 조정이 필요 없습니다. 그림 3은(는) 10A 부하 단계의 부하 과도 파형을 나타내며, 두 번째 단계 필터 구현 이후 출력 전압 파형에는 불안정성 징후가 전혀 보이지 않습니다.

그림 2 두 번째 단계 필터를 추가했을 때와 추가하지 않았을 때의 TPS56121 출력 전압 리플.

그림 2 두 번째 단계 필터를 추가했을 때와 추가하지 않았을 때의 TPS56121 출력 전압 리플. 그림 3 전압 모드 제어를 사용하는 TPS56121의 과도 응답.

그림 3 전압 모드 제어를 사용하는 TPS56121의 과도 응답.