SLUAAG2 October 2021 UCC28782

2 Control Law across Entire Load Range

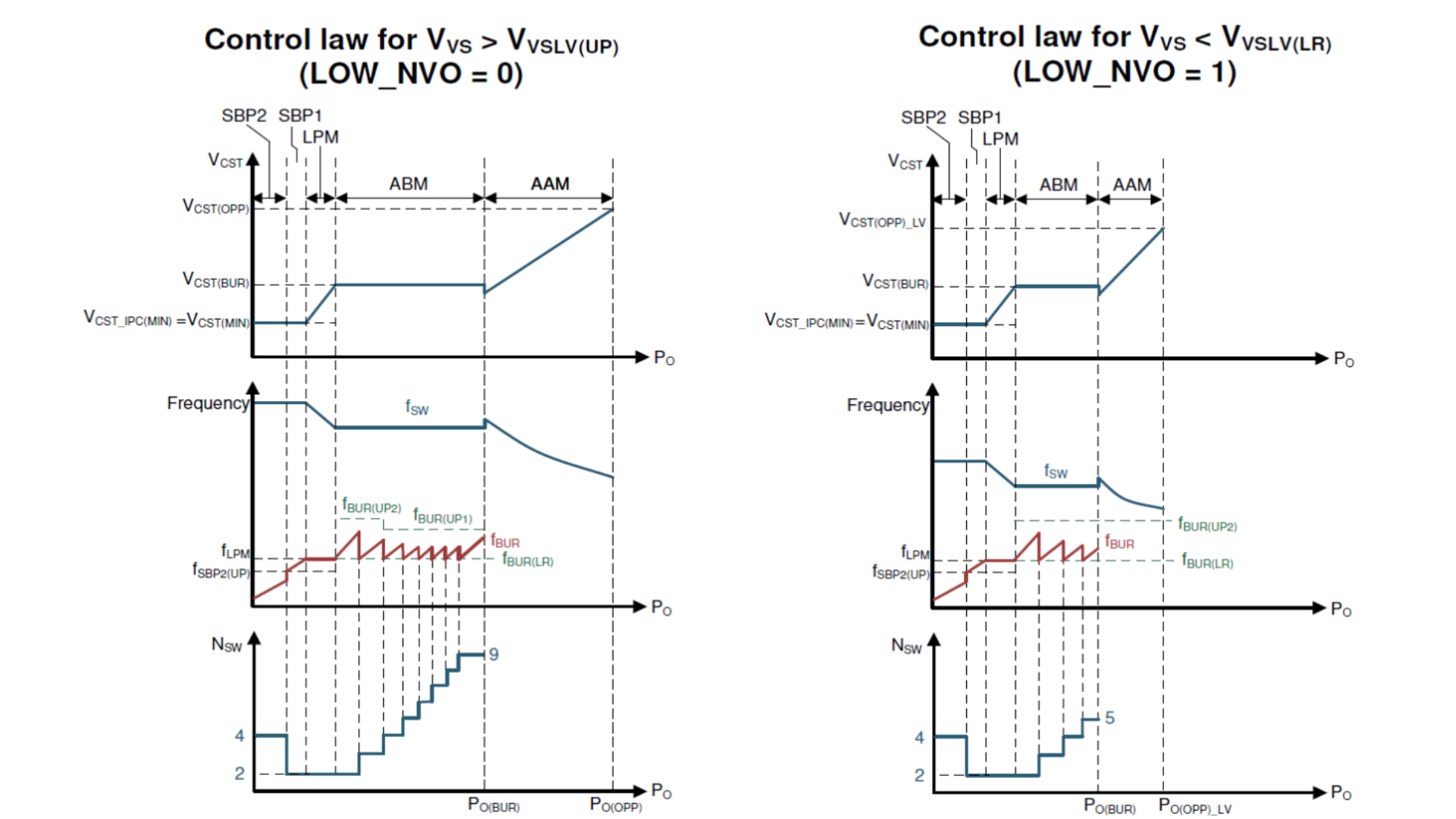

UCC28782 contains six modes of operation summarized in Table 2-1. Starting from heavier load, the AAM mode forces PWML and PWMH into complementary switching with ZVS tuning enabled. ABM mode generates a group of PWML and PWMH pulses as a burst packet, and adjusts the burst off-time to regulate the output voltage. At the same time, the burst frequency variation is confined above 20kHz by adjusting the number of PWML and PWMH pulses per packet to mitigate audible noise and reduce burst output ripple. In LPM, SBP1, and SBP2 modes, PWMH and the ZVS tuning loop are disabled, so the converter operates in valley-switching. The survival mode is to maintain VVDD higher than VVDD(OFF) in a long burst off time, and also performs the clamping capacitor balancing function to reduce the voltage stress of the secondary-side rectifier .

Table 2-1 and Figure 2-1 also show the frequency and power level at each mode, so it helps to understand the mode operation.

| MODE | OPERATION | PWMH | ZVS | |

|---|---|---|---|---|

| AAM | Adaptive Amplitude Modulation | ACF operation with PWML and PWMH in complementary switching | Enabled | Yes |

| ABM | Adaptive Burst Mode | Variable FBUR > FBUR(LR), ACF operation in complementary switching | Enabled | Yes |

| LPM | Low Power Mode | Fix FBUR ≈ FLPM, valley-switching | Disabled | No |

| SBP1 | First Standby Power Mode | Variable FBUR between FSBP2(LR) and FSBP2(UP), valley- switching | Disabled | No |

| SBP2 | Second Standby Power Mode | Variable FBUR< FSBP2(UP) as VBUR < 0.9 V; Variable FBUR< FSBP2(LR) as VBUR > 0.9 V; Both are in valley-switching | Disabled | No |

| INT_STOP | Survival Mode |

When VVDD < VVDD(OFF) + VVDD(PCT), a series of PWML pulses followed by a long PWMH pulse is generated |

Enabled in the lastswitching cycle of a survival-mode burst packet | No |

Figure 2-1 Control Law Over Entire Load

Range Based on the VVS Condition as VIPC < 0.9

V

Figure 2-1 Control Law Over Entire Load

Range Based on the VVS Condition as VIPC < 0.9

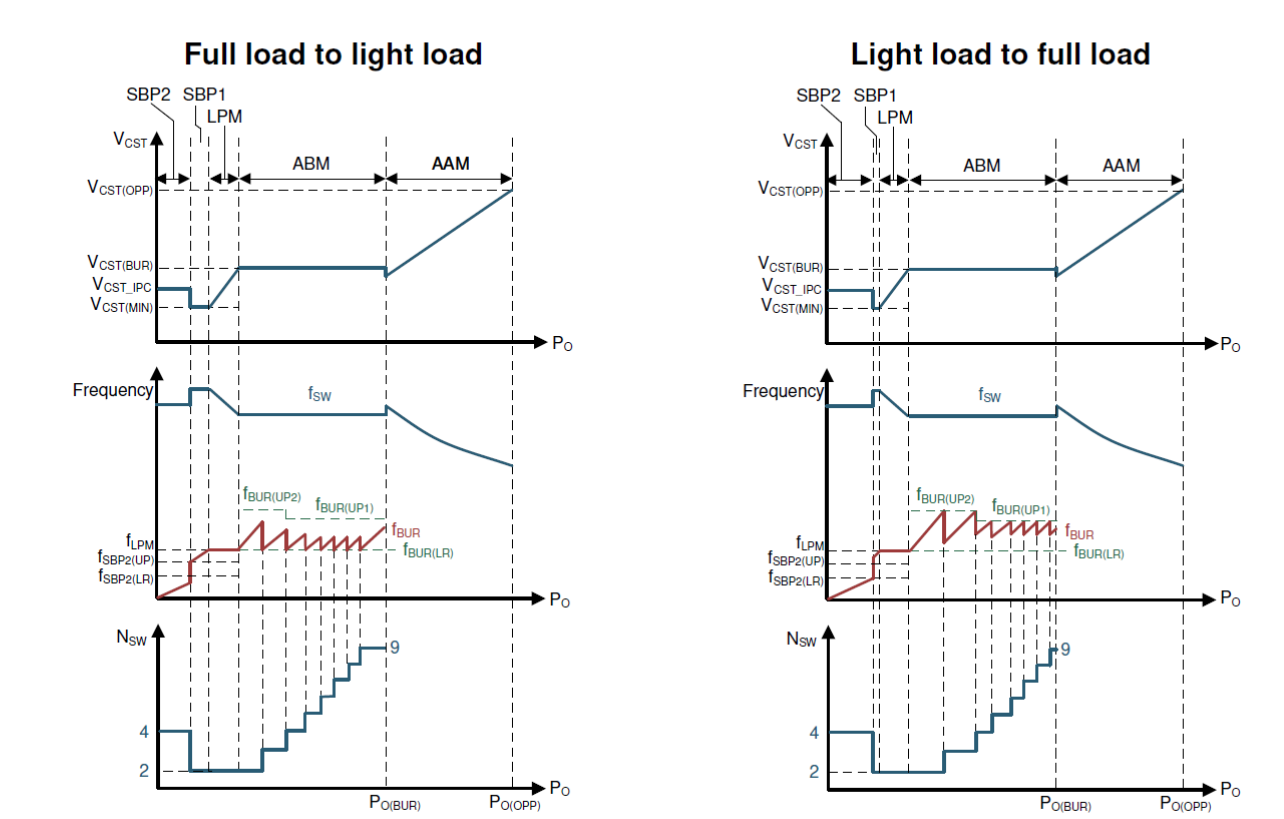

V Figure 2-2 Control Law Under Different

Load Sweep Direction as VIPC > 0.9 V and VVS >

VVSLV(UP)

Figure 2-2 Control Law Under Different

Load Sweep Direction as VIPC > 0.9 V and VVS >

VVSLV(UP)