SPRADG5 January 2024 DRA821U , DRA821U-Q1 , TDA4AL-Q1 , TDA4VH-Q1 , TDA4VL-Q1 , TDA4VM , TDA4VM-Q1

4.1 Change MAIN_UARTx for MAIN Domain

The default terminal output on the different Jacinto 7 series processors is not the same. For example, UART0 is used for the terminal output on the J721E and J7200 EVMs, but UART8 is the primary UART interface for the J721S2 and J784S4 EVMs. As the pins of UART ports can also be used by other applications, it is a common request to customize the UART port depending on customers’ use cases. The following was an example of changing the default UART8 to UART2 on TDA4VH main domain base on SDK 8.6, and this also can be a reference of changing to other ports on other Jacinto 7 processors.

- Add the clock setting for

UART2.

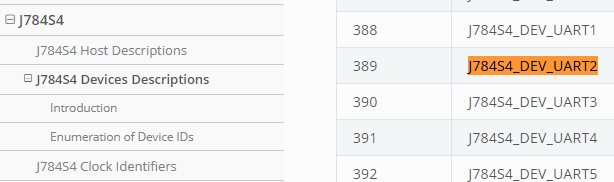

The 389 is the device ID of J784S4 series, and can be found from the link.

Figure 4-1 TDA4VH UART Clock

ID

Figure 4-1 TDA4VH UART Clock

IDdiff --git a/arch/arm/mach-k3/j784s4/clk-data.c b/arch/arm/mach-k3/j784s4/clk-data.c index a266735cc0..081c6d8970 100644 --- a/arch/arm/mach-k3/j784s4/clk-data.c +++ b/arch/arm/mach-k3/j784s4/clk-data.c @@ -283,7 +283,7 @@ static const struct clk_data clk_list[] = { CLK_MUX("emmcsd_refclk_sel_out1", emmcsd_refclk_sel_out1_parents, 4, 0x1080b4, 0, 2, 0), CLK_MUX("gtc_clk_mux_out0", gtc_clk_mux_out0_parents, 16, 0x108030, 0, 4, 0), CLK_DIV_DEFFREQ("usart_programmable_clock_divider_out0", "hsdiv4_16fft_main_1_hsdivout0_clk", 0x1081c0, 0, 2, 0, 0, 48000000), - CLK_DIV("usart_programmable_clock_divider_out5", "hsdiv4_16fft_main_1_hsdivout0_clk", 0x1081d4, 0, 2, 0, 0), + CLK_DIV("usart_programmable_clock_divider_out2", "hsdiv4_16fft_main_1_hsdivout0_clk", 0x1081c8, 0, 2, 0, 0), CLK_DIV("usart_programmable_clock_divider_out8", "hsdiv4_16fft_main_1_hsdivout0_clk", 0x1081e0, 0, 2, 0, 0), CLK_DIV("k3_pll_ctrl_wrap_main_0_chip_div24_clk_clk", "k3_pll_ctrl_wrap_main_0_sysclkout_clk", 0x41011c, 0, 5, 0, 0), CLK_DIV("k3_pll_ctrl_wrap_wkup_0_chip_div24_clk_clk", "k3_pll_ctrl_wrap_wkup_0_sysclkout_clk", 0x4201011c, 0, 5, 0, 0), @@ -405,8 +405,8 @@ static const struct dev_clk soc_dev_clk_data[] = { DEV_CLK(279, 2, "wkup_i2c_mcupll_bypass_out0"), DEV_CLK(279, 3, "hsdiv4_16fft_mcu_1_hsdivout3_clk"), DEV_CLK(279, 4, "gluelogic_hfosc0_clkout"), - DEV_CLK(392, 0, "usart_programmable_clock_divider_out5"), - DEV_CLK(392, 3, "k3_pll_ctrl_wrap_main_0_chip_div1_clk_clk"), + DEV_CLK(389, 0, "usart_programmable_clock_divider_out2"), + DEV_CLK(389, 3, "k3_pll_ctrl_wrap_main_0_chip_div1_clk_clk"), DEV_CLK(395, 0, "usart_programmable_clock_divider_out8"), DEV_CLK(395, 3, "k3_pll_ctrl_wrap_main_0_chip_div1_clk_clk"), DEV_CLK(398, 0, "k3_pll_ctrl_wrap_main_0_chip_div1_clk_clk"), - Add the device ID and LPSC

setting in the list for UART2.

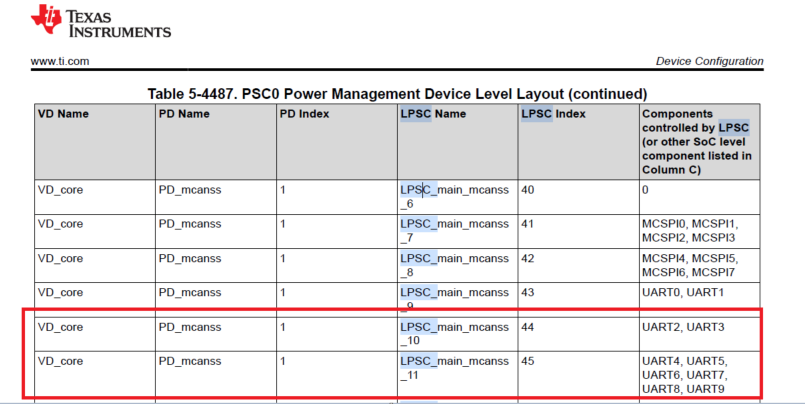

The 44 is the LPSC index of UART2 for J784S4 series, and could be searched from device-specific TRM.

Figure 4-2 TDA4VH UART

LPSC

Figure 4-2 TDA4VH UART

LPSCdiff --git a/arch/arm/mach-k3/j784s4/dev-data.c b/arch/arm/mach-k3/j784s4/dev-data.c index e44afad3ec..b5ae132b4a 100644 --- a/arch/arm/mach-k3/j784s4/dev-data.c +++ b/arch/arm/mach-k3/j784s4/dev-data.c @@ -51,6 +51,7 @@ static struct ti_lpsc soc_lpsc_list[] = { [20] = PSC_LPSC(81, &soc_psc_list[2], &soc_pd_list[6], &soc_lpsc_list[18]), [21] = PSC_LPSC(120, &soc_psc_list[2], &soc_pd_list[7], &soc_lpsc_list[22]), [22] = PSC_LPSC(121, &soc_psc_list[2], &soc_pd_list[7], NULL), + [23] = PSC_LPSC(44, &soc_psc_list[2], &soc_pd_list[3], NULL), }; static struct ti_dev soc_dev_list[] = { @@ -76,7 +77,7 @@ static struct ti_dev soc_dev_list[] = { PSC_DEV(141, &soc_lpsc_list[14]), PSC_DEV(140, &soc_lpsc_list[15]), PSC_DEV(146, &soc_lpsc_list[16]), - PSC_DEV(392, &soc_lpsc_list[17]), + PSC_DEV(389, &soc_lpsc_list[23]), PSC_DEV(395, &soc_lpsc_list[17]), PSC_DEV(198, &soc_lpsc_list[18]), PSC_DEV(202, &soc_lpsc_list[19]), -- - Set serial port and pin, this

should set for both UBOOT dts and Kernel dts

files.

diff --git a/arch/arm/dts/k3-j784s4-evm-u-boot.dtsi b/arch/arm/dts/k3-j784s4-evm-u-boot.dtsi index 9d6f7dbbd5..3846d90f9a 100644 --- a/arch/arm/dts/k3-j784s4-evm-u-boot.dtsi +++ b/arch/arm/dts/k3-j784s4-evm-u-boot.dtsi @@ -12,7 +12,7 @@ aliases { serial0 = &wkup_uart0; serial1 = &mcu_uart0; - serial2 = &main_uart8; + serial2 = &main_uart2; i2c0 = &wkup_i2c0; i2c1 = &mcu_i2c0; i2c2 = &mcu_i2c1; @@ -105,6 +105,10 @@ u-boot,dm-spl; }; +&main_uart2_pins_default { + u-boot,dm-spl; +}; + &main_mmc1_pins_default { u-boot,dm-spl; }; @@ -132,6 +136,10 @@ u-boot,dm-spl; }; +&main_uart2 { + u-boot,dm-spl; +}; + &mcu_uart0 { u-boot,dm-spl; }; diff --git a/arch/arm/dts/k3-j784s4-evm.dts b/arch/arm/dts/k3-j784s4-evm.dts index 5e213b2c11..7f8f507318 100644 --- a/arch/arm/dts/k3-j784s4-evm.dts +++ b/arch/arm/dts/k3-j784s4-evm.dts @@ -21,7 +21,7 @@ stdout-path = "serial2:115200n8"; }; aliases { - serial2 = &main_uart8; + serial2 = &main_uart2; mmc0 = &main_sdhci0; mmc1 = &main_sdhci1; can0 = &mcu_mcan0; @@ -402,6 +402,15 @@ >; }; + main_uart2_pins_default: main-uart2-pins-default { + pinctrl-single,pins = < + J784S4_IOPAD(0x0c4, PIN_INPUT, 11) /* (AD36) CTSn */ + J784S4_IOPAD(0x0c8, PIN_OUTPUT, 11) /* (AJ32) RTSn */ + J784S4_IOPAD(0x0dc, PIN_OUTPUT, 11) /* (AM36) TXD */ + J784S4_IOPAD(0x0d8, PIN_INPUT, 11) /* (AM35) RXD*/ + >; + }; + main_i2c3_pins_default: main-i2c3-pins-default { pinctrl-single,pins = < J784S4_IOPAD(0x064, PIN_INPUT_PULLUP, 13) /* (AF38) MCAN0_TX.I2C3_SCL */ @@ -743,11 +752,13 @@ status = "disabled"; }; -&main_uart1 { - status = "disabled"; +&main_uart2 { + status = "okay"; + pinctrl-names = "default"; + pinctrl-0 = <&main_uart2_pins_default>; }; -&main_uart2 { +&main_uart1 { status = "disabled"; }; diff --git a/arch/arm/dts/k3-j784s4-r5-evm.dts b/arch/arm/dts/k3-j784s4-r5-evm.dts index 4a697e2738..154a07c802 100644 --- a/arch/arm/dts/k3-j784s4-r5-evm.dts +++ b/arch/arm/dts/k3-j784s4-r5-evm.dts @@ -13,7 +13,7 @@ / { chosen { firmware-loader = &fs_loader0; - stdout-path = &main_uart8; + stdout-path = &main_uart2; tick-timer = &timer1; }; @@ -151,6 +151,15 @@ >; }; + main_uart2_pins_default: main-uart2-pins-default { + pinctrl-single,pins = < + J784S4_IOPAD(0x0c4, PIN_INPUT, 11) /* (AD36) CTSn */ + J784S4_IOPAD(0x0c8, PIN_OUTPUT, 11) /* (AJ32) RTSn */ + J784S4_IOPAD(0x0dc, PIN_OUTPUT, 11) /* (AM36) TXD */ + J784S4_IOPAD(0x0d8, PIN_INPUT, 11) /* (AM35) RXD*/ + >; + }; + main_mmc1_pins_default: main-mmc1-pins-default { pinctrl-single,pins = < J784S4_IOPAD(0x104, PIN_INPUT, 0) /* (AB38) MMC1_CLK */ @@ -253,6 +262,12 @@ pinctrl-0 = <&main_uart8_pins_default>; }; +&main_uart2 { + status = "okay"; + pinctrl-names = "default"; + pinctrl-0 = <&main_uart2_pins_default>; +}; - Configure the boot command for

UART2.

diff --git a/include/configs/j784s4_evm.h b/include/configs/j784s4_evm.h index eb609100b0..942d6c3dbe 100644 --- a/include/configs/j784s4_evm.h +++ b/include/configs/j784s4_evm.h @@ -75,7 +75,7 @@ "setenv fdtfile ${name_fdt}\0" \ "name_kern=Image\0" \ "console=ttyS2,115200n8\0" \ - "args_all=setenv optargs earlycon=ns16550a,mmio32,0x02880000 " \ + "args_all=setenv optargs earlycon=ns16550a,mmio32,0x02820000 " \ "${mtdparts}\0" \ "run_kern=booti ${loadaddr} ${rd_spec} ${fdtaddr}\0" -- - Rebuild the OPTEE if it is

Used.

Just change 8 to 2 in export CFG_CONSOLE_UART=0x8 according to this link.

- Change the Arm® Trust

Firmware.

diff --git a/plat/ti/k3/include/platform_def.h b/plat/ti/k3/include/platform_def.h index 690c68e5c..db083ca2f 100644 --- a/plat/ti/k3/include/platform_def.h +++ b/plat/ti/k3/include/platform_def.h @@ -91,14 +91,14 @@ /* Platform default console definitions */ #ifndef K3_USART_BASE -#define K3_USART_BASE 0x02800000 +#define K3_USART_BASE 0x02820000 #endifAfter modifying the above K3_USART_BASE for UART2, then the following instructions are needed to recompile bl31.bin

- cd $SDK_PATH/board-support/trusted-firmware-a-2.8+gitAUTOINC+2fcd408bb3

- make CROSS_COMPILE=aarch64-none-linux-gnu- ARCH=aarch64 PLAT=k3 TARGET_BOARD=generic SPD=opted

- cp ./build/k3/generic/release/bl31.bin ../prebuilt-images/

Then based on the rebuilt bl31.bin, the below instructions are required to make it as part of tispl.bin, and copy tispl.bin and u-boot.img to the BOOT in the SD card.

- cd ../../

- make u-boot-spl-jacinto

- cp board-support/u-boot_build/a72/tispl.bin board-support/u-boot_build/a72/u-boot.img /media/$USER/BOOT

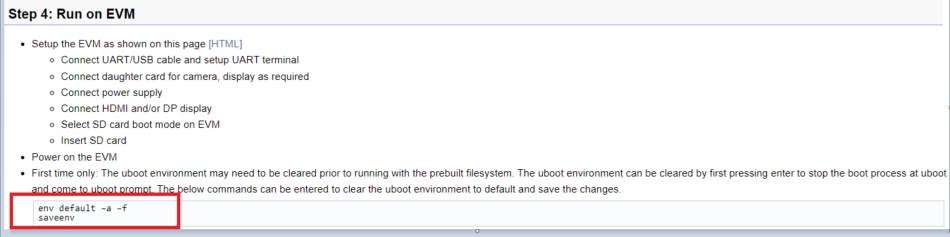

- Clear the UBOOT Environment to the Default and Save the

Changes.

Figure 4-3 UBOOT Environment

Set. CAUTION: Step 7 is not requested anymore starting from SDK9.0. It is sufficient to apply the above 7 steps to change the default main UART port from 8 to 2 on TDA4VH.

Figure 4-3 UBOOT Environment

Set. CAUTION: Step 7 is not requested anymore starting from SDK9.0. It is sufficient to apply the above 7 steps to change the default main UART port from 8 to 2 on TDA4VH.