SPRUIT1B May 2020 – November 2020

- Trademarks

- 1Introduction

- 2GESI Expansion Board Overview

- 3GESI Expansion Board - User Setup/Configuration

- 4GESI Expansion Board Hardware Architecture

- A Interface Mapping

- B GESI Board GPIO Mapping

- C I2C Address Mapping

- D Revision History

4.4.1 RGMII Clocking Scheme

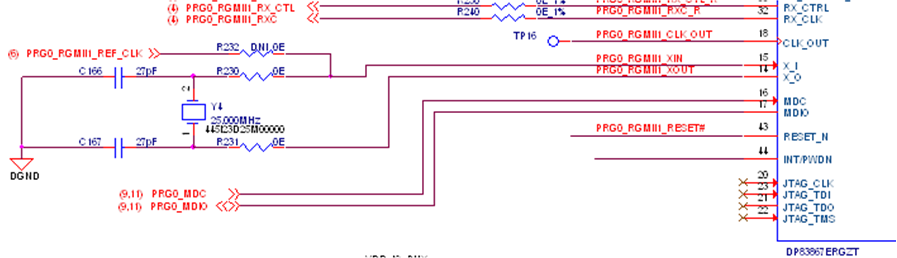

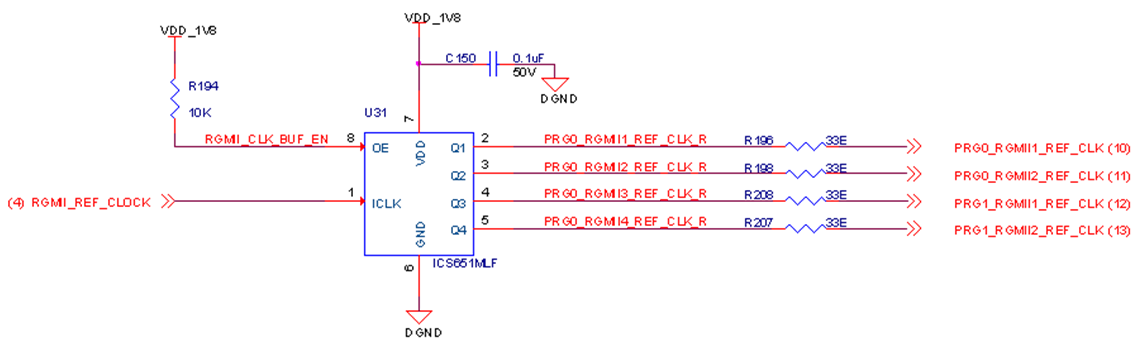

Reference clock for Ethernet PHY DP83867 is provided by a 25 MHz Crystal attached to the each PHY chip. Also, the system has an option to source the reference clock to the Ethernet PHY from CP Board Clock Generator with the low skew 1:4 clock buffer ICS651MLF on GESI Expansion board.

Figure 4-4 RGMII PHY Default Reference Clock Source

Figure 4-4 RGMII PHY Default Reference Clock Source Figure 4-5 Ethernet PHY Reference Clock buffer (Optional)

Figure 4-5 Ethernet PHY Reference Clock buffer (Optional)