SPRUJ09D March 2022 – September 2023 AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1

- 1

- Abstract

- Trademarks

- 1Preface: Read This First

- 2Control Card Overview

- 3Board Setup

- 4Hardware Description

- 5References

- Revision History

- A E2 Design Changes

- B E1 HSEC Pinout Table

4.3 Reset

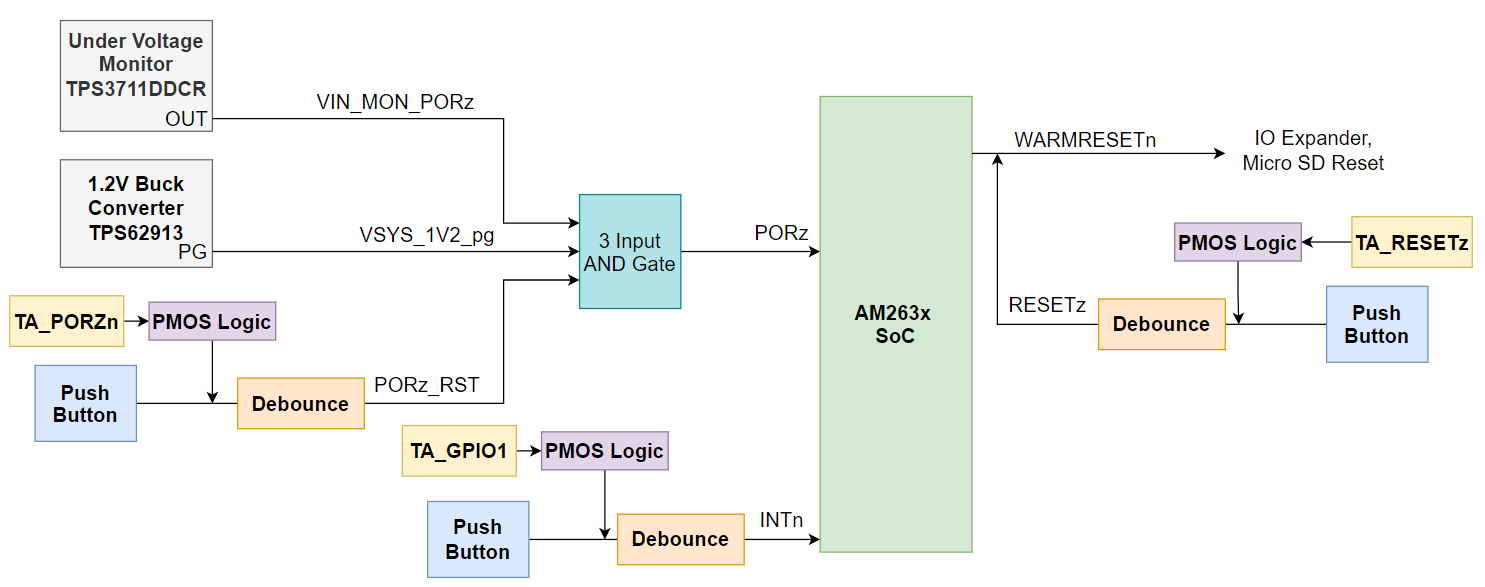

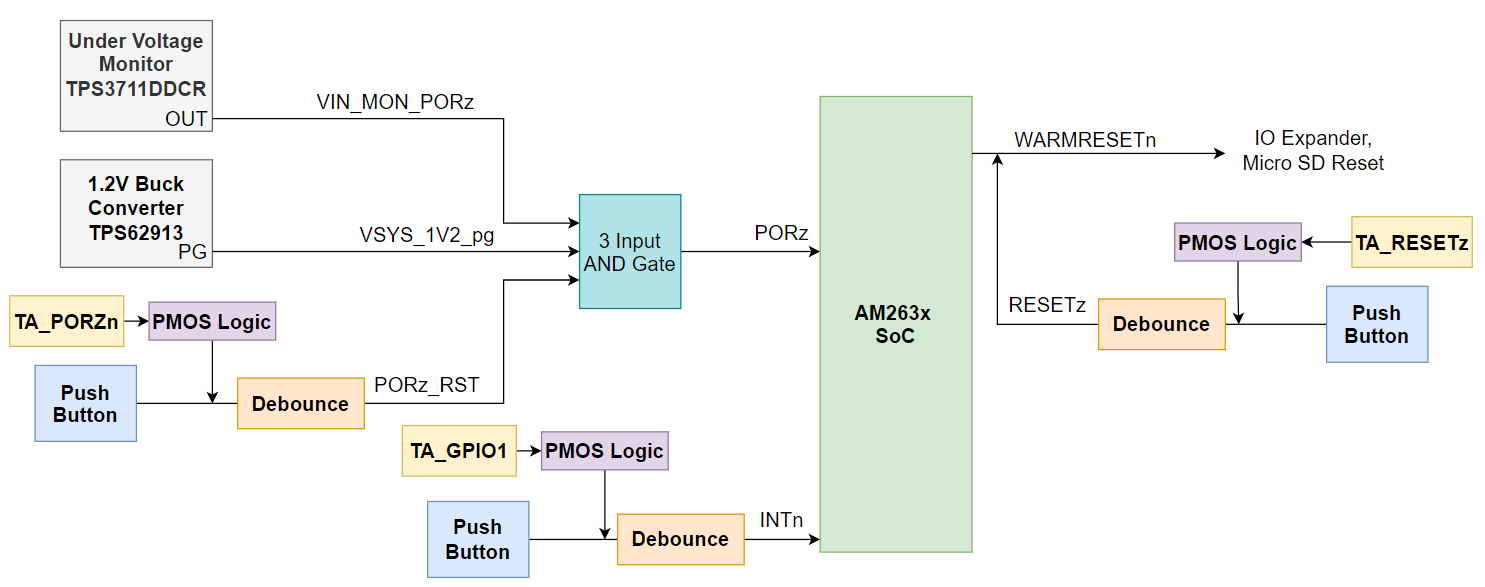

Figure 4-2 shows the reset architecture of the AM263x Control Card.

Figure 4-2 Reset Architecture

Figure 4-2 Reset Architecture

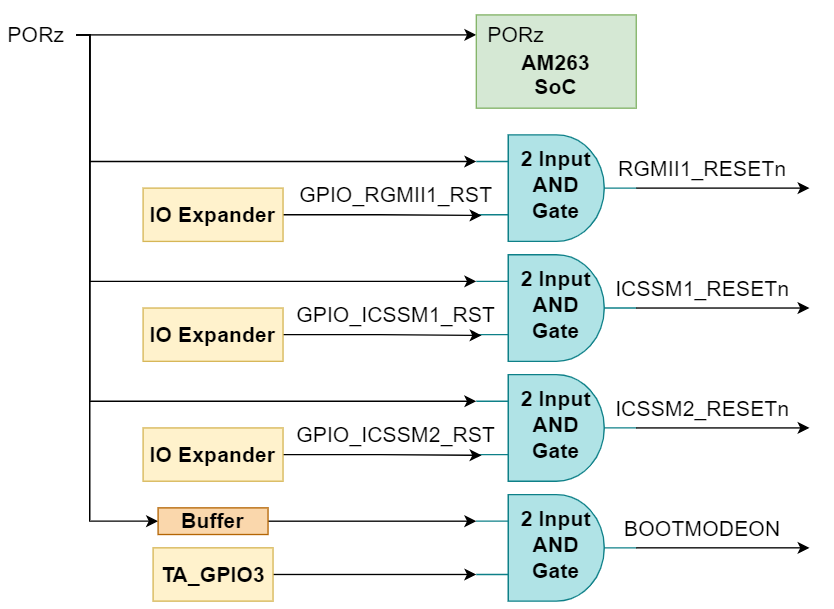

Figure 4-3 PORz Reset Signal Tree

Figure 4-3 PORz Reset Signal Tree

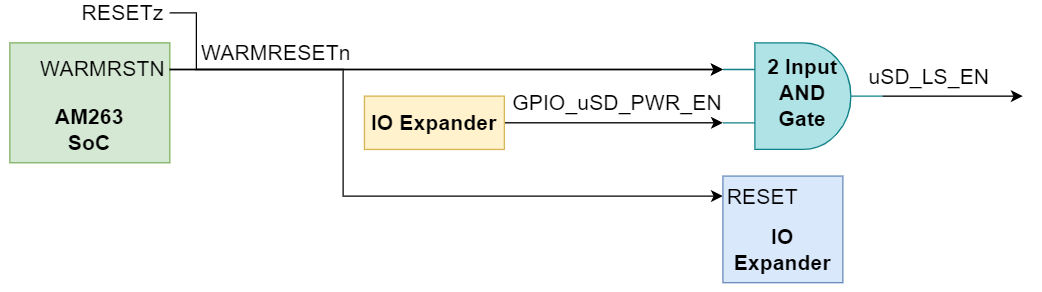

Figure 4-4 WARMRESETn Reset Signal

Tree

Figure 4-4 WARMRESETn Reset Signal

Tree

Figure 4-2 Reset Architecture

Figure 4-2 Reset ArchitectureThe AM263x SoC has the following resets:

- PORz is the Power-On-Reset for the MAIN Domain.

- WARMRESETn is the Warm Reset to MAIN Domain.

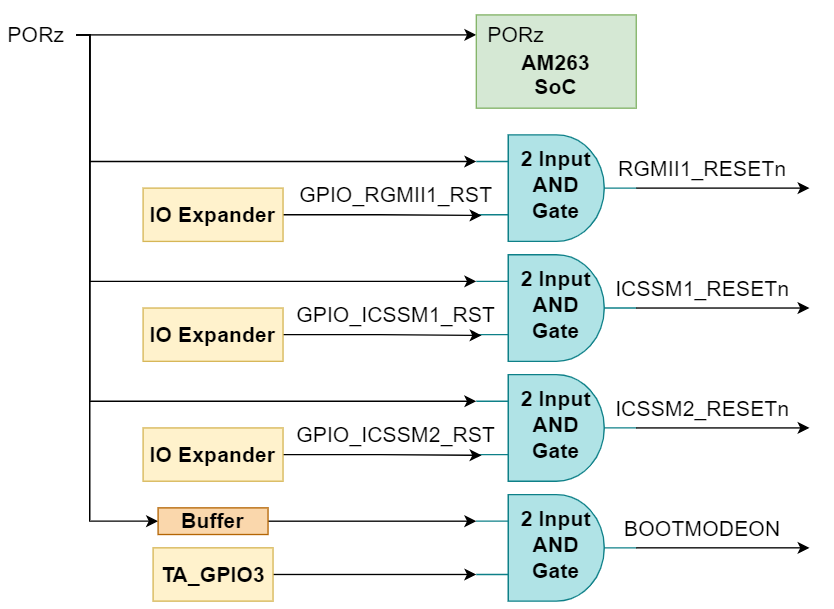

Figure 4-3 PORz Reset Signal Tree

Figure 4-3 PORz Reset Signal TreeThe PORz signal is driven by a 3-input AND gate that generates a power on reset for the MAIN domain when:

- The under voltage monitor (TPS3711DDCR) has an input voltage, VMAIN, that is below 4.48 V.

- The 1.2-V buck converter (TPS62913RPUR) power good output is driven low by having an output voltage that is below the power-good threshold.

- The user push button (SW2) is pressed.

- The Test Automation Header outputs a logic LOW signal (TA_PORZn) to a P-Channel MOSFET gate which causes V_GS of the PMOS to be less than zero and so the PORz signal connects to the PMOS drain which is tied directly to ground.

The PORz signal is tied to:

- AM263x SoC PORz input

- RGMII1 Ethernet PHY reset

- ICSSM1 Gigabit Ethernet PHY reset

- ICSSM2 Industrial Ethernet PHY reset

- BOOTMODE buffer output enable

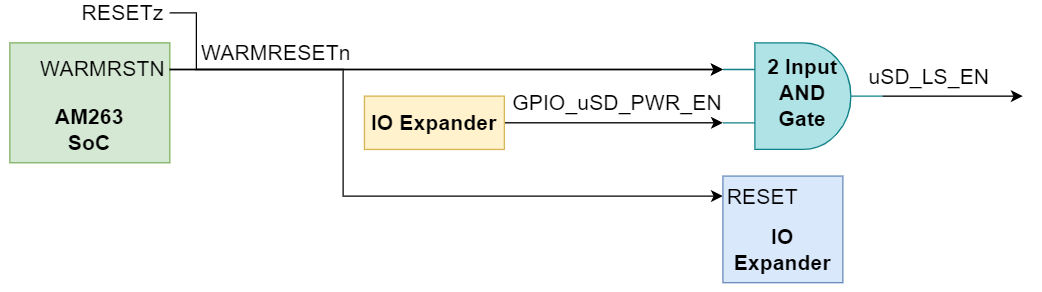

Figure 4-4 WARMRESETn Reset Signal

Tree

Figure 4-4 WARMRESETn Reset Signal

TreeThe WARMRESETn signal creates a warm reset to the MAIN domain when:

- The user push button (SW4) is pressed.

- The Test Automation Header outputs a logic LOW signal (TA_RESETz) to a P-Channel MOSFET gate which causes V_GS of the PMOS to be less than zero and so the RESETz signal connects to the PMOS drain which is tied directly to ground.

The WARMRESETn signal is tied to:

- AM263x SoC WARMRESETN output

- RESETz signal created from push button + PMOS logic

- IO Expander reset

- Micro SD reset

The AM263x Control Card also has an external interrupt to the SoC, INTn, that occurs when:

- The user push button (SW1) is pressed.

- The Test Automation Header outputs a logic LOW signal (TA_GPIO1) to a P-Channel MOSFET gate which causes V_GS of the PMOS to be less than zero and so the INTn signal connects to the PMOS drain which is tied directly to ground.