SPRUJA2 November 2023

- 1

- Description

- Get Started

- Features

- 5

- 1Evaluation Module Overview

-

2Hardware

- 2.1 Additional Images

- 2.2 Key Features

- 2.3 Interface Mapping

- 2.4 Power ON/OFF Procedure

- 2.5 Clocking

- 2.6 Reset

- 2.7 CSI Interface

- 2.8 OLDI Interface

- 2.9 DSI Interface

- 2.10 Audio Codec Interface

- 2.11 HDMI Display Interface

- 2.12 JTAG Interface

- 2.13 Test Automation Header

- 2.14 UART Interface

- 2.15 USB Interface

- 2.16 Memory Interfaces

- 2.17 Ethernet Interface

- 2.18 GPIO Port Expander

- 2.19 GPIO Mapping

- 2.20 Power

- 2.21 EVM User Setup/Configuration

- 2.22 Expansion Headers

- 2.23 Interrupt

- 2.24 I2C Address Mapping

- 3Hardware Design Files

- 4Compliance Information

- 5Additional Information

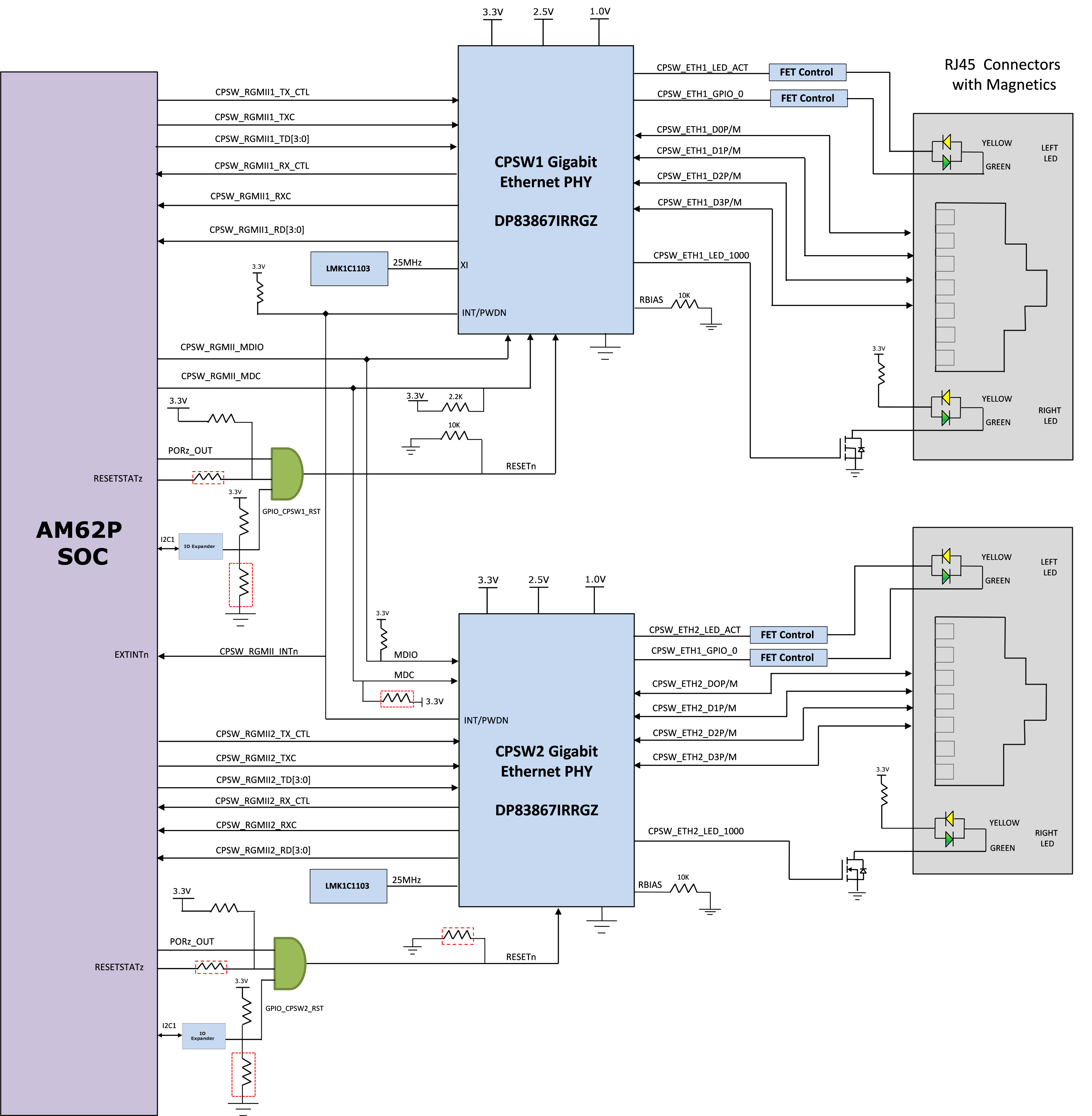

2.17 Ethernet Interface

The AM62P SK EVM offers two Ethernet Ports of 1 Gigabit Speed for external Communication. Two channels of RGMII Gigabit Ethernet CPSW Ports from AM62P SoC are connected to separate Gigabit Ethernet PHY Transceivers DP83867, which are finally terminated on two RJ45 connectors with integrated magnetics.

The 48pin version of the PHY DP83867 is configured to advertise 1Gb operation with the Tx & Rx clock skew set to accommodate the internal delay inside the AM62P. CPSW_RGMII1 and CPSW_RGMII2 Ports share a common MDIO Bus to communicate with the external PHY Transceiver.

Two Single port RJ45 Connectors Mfr Part# LPJG16314A4NL from Link-PP are used on the board for Ethernet 10/100/1000 Mbps Connectivity. RJ45 Connectors have integrated magnetics and LEDs for indicating 1000BASE-T link as well as receive or transmit Activity.

I/O supply to the Ethernet PHY is set 3.3V IO level.

Figure 2-23 Ethernet Interface

Figure 2-23 Ethernet Interface