TIDUD61E October 2020 – April 2021

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements, and Test Results

- 3.1

Required Hardware and Software

- 3.1.1 Hardware

- 3.1.2

Software

- 3.1.2.1 Opening Project Inside CCS

- 3.1.2.2 Project Structure

- 3.1.2.3 Using CLA on C2000 MCU to Alleviate CPU Burden

- 3.1.2.4 CPU and CLA Utilization and Memory Allocation

- 3.1.2.5

Running the Project

- 3.1.2.5.1 Lab 1: Open Loop, DC (PFC Mode)

- 3.1.2.5.2 Lab 2: Closed Current Loop DC (PFC)

- 3.1.2.5.3 Lab 3: Closed Current Loop, AC (PFC)

- 3.1.2.5.4 Lab 4: Closed Voltage and Current Loop (PFC)

- 3.1.2.5.5 Lab 5: Open loop, DC (Inverter)

- 3.1.2.5.6 Lab 6: Open loop, AC (Inverter)

- 3.1.2.5.7 Lab 7: Closed Current Loop, DC (Inverter with resistive load)

- 3.1.2.5.8 Lab 8: Closed Current Loop, AC (Inverter with resistive load)

- 3.1.2.5.9 Lab 9: Closed Current Loop (Grid Connected Inverter)

- 3.1.2.6 Running Code on CLA

- 3.1.2.7

Advanced Options

- 3.1.2.7.1 Input Cap Compensation for PF Improvement Under Light Load

- 3.1.2.7.2 83

- 3.1.2.7.3 Adaptive Dead Time for Efficiency Improvements

- 3.1.2.7.4 Phase Shedding for Efficiency Improvements

- 3.1.2.7.5 Non-Linear Voltage Loop for Transient Reduction

- 3.1.2.7.6 Software Phase Locked Loop Methods: SOGI - FLL

- 3.2 Testing and Results

- 3.1

Required Hardware and Software

- 4Design Files

- 5Software Files

- 6Related Documentation

- 7About the Author

- 8Revision History

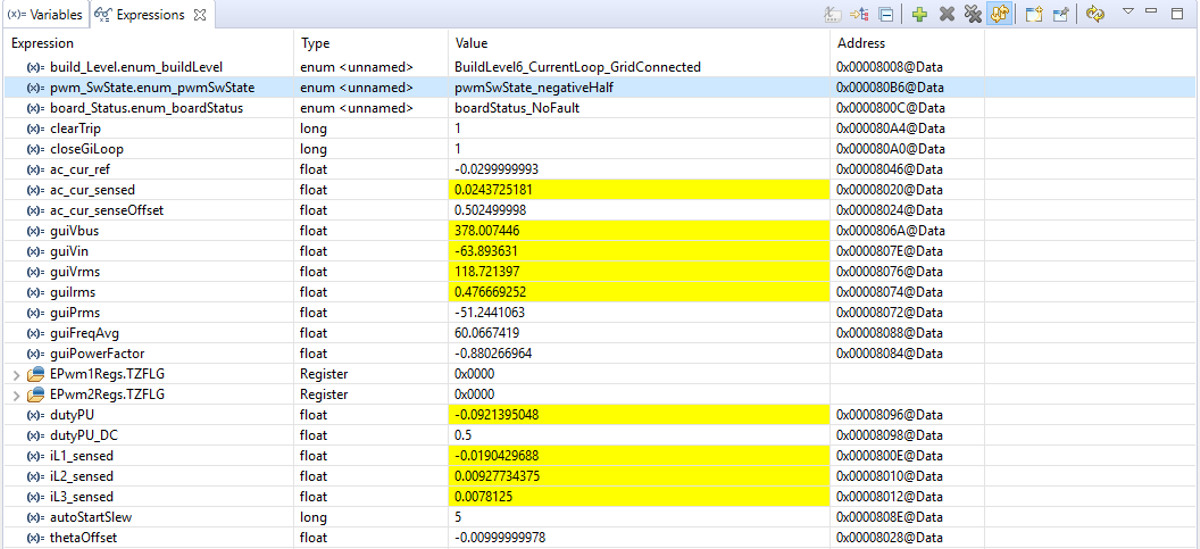

3.1.2.5.9.3 Running Code: Emulated Grid-tied Condition (Verification purpose only)

Figure 3-40 HW setup for Build 6 Emulated Grid Condition

Figure 3-40 HW setup for Build 6 Emulated Grid Condition- The project is programmed to wait for dc bus voltage and ac source voltage to exceed approximately 340 V and 75 Vrms to drive the in rush relay, and clear the trip.

- Run the project by clicking

.

. - Now apply an input voltage of approximately 340 V, the board comes out of the undervoltage condition. To run the solution, ac voltage in the output of the inverter has to be higher than 75 V rms and then inrush relay is driven. TTPLPFC_ac_cur_ref is set to -0.03 by default.

- Change TTPLPFC_pwmSwState from pwmSwState_defaultState to pwmSwState_normalOperation to enable pwm output. The pwm output is turned off by default and the inverter does not work without selecting this option.

- Slowly increase TTPLPFC_ac_cur_ref to -0.05 and inverter output current is close to 0.8 A in RMS value. The output voltage of the inverter is determined by the ac voltage source.

- As the source impedance of the emulgated grid condition is not as small as the actual grid, the bandwidth of the current loop is much lower than the designed target and the system suffers from huge current spikes near zero crossing.

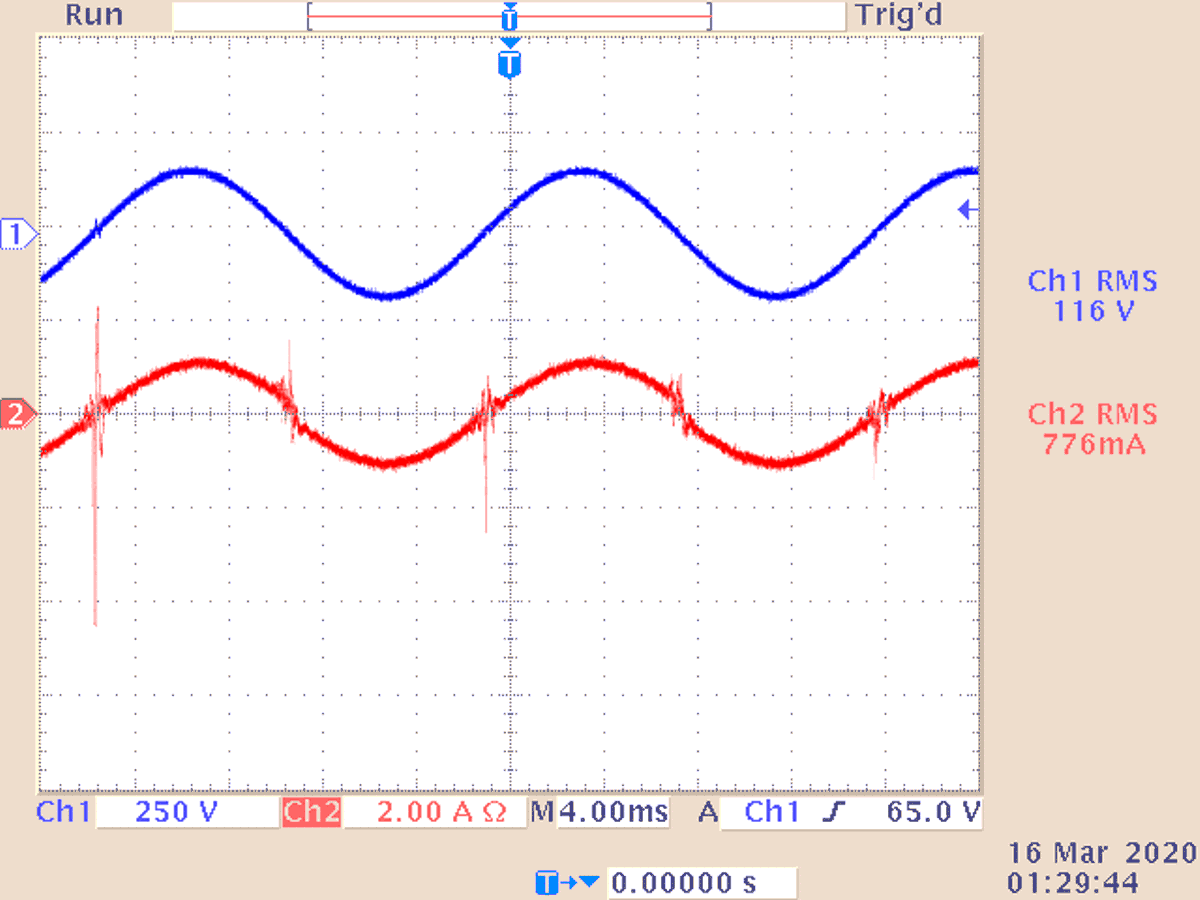

Figure 3-41 Lab 9: Closed Current Loop after close the current loop

Figure 3-41 Lab 9: Closed Current Loop after close the current loop Figure 3-42 Voltage and current waveform (Lab 9 Emulated Grid Condition)

Figure 3-42 Voltage and current waveform (Lab 9 Emulated Grid Condition) - To bring the system to a safe stop, switch off the output from the AC power supply first and switch off the input DC power supply subsequently. This will eliminate the risk of the undesired reverse power flow in the inverter mode. Bring input AC voltage down to zero and observe the TTPLPFC_ac_volRms_sensed_Volts comes down to zero as well. After AC voltage is fully switched off, the the input DC voltage has to be down to zero, observe the TTPLPFC_vBus_sensed_Volts becomes zero.

- Fully halting the MCU when in real-time mode is a two-step process. First halt the processor by using the Halt button on the toolbar (

) or by using Target → Halt. Then take the MCU out of real-time mode by clicking on

) or by using Target → Halt. Then take the MCU out of real-time mode by clicking on  . Finally, reset the MCU (

. Finally, reset the MCU ( ) .

) . - Close the CCS debug session by clicking Terminate Debug Session (Target → Terminate all).