SNAS192G April 2003 – May 2016 ADCS7476 , ADCS7477 , ADCS7478

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DBV|6

Thermal pad, mechanical data (Package|Pins)

Orderable Information

7 Detailed Description

7.1 Overview

The ADCS747x devices are successive-approximation analog-to-digital converters designed around a charge-redistribution digital-to-analog converter. Simplified schematics of the ADCS747x in both track and hold operation are shown in Figure 25 and Figure 26. In Figure 26, the device is in track mode where the switch SW1 connects the sampling capacitor to the input, and SW2 balances the comparator inputs. The device is in this state until CS is brought low, at which point the device moves to hold mode.

7.2 Functional Block Diagram

7.3 Feature Description

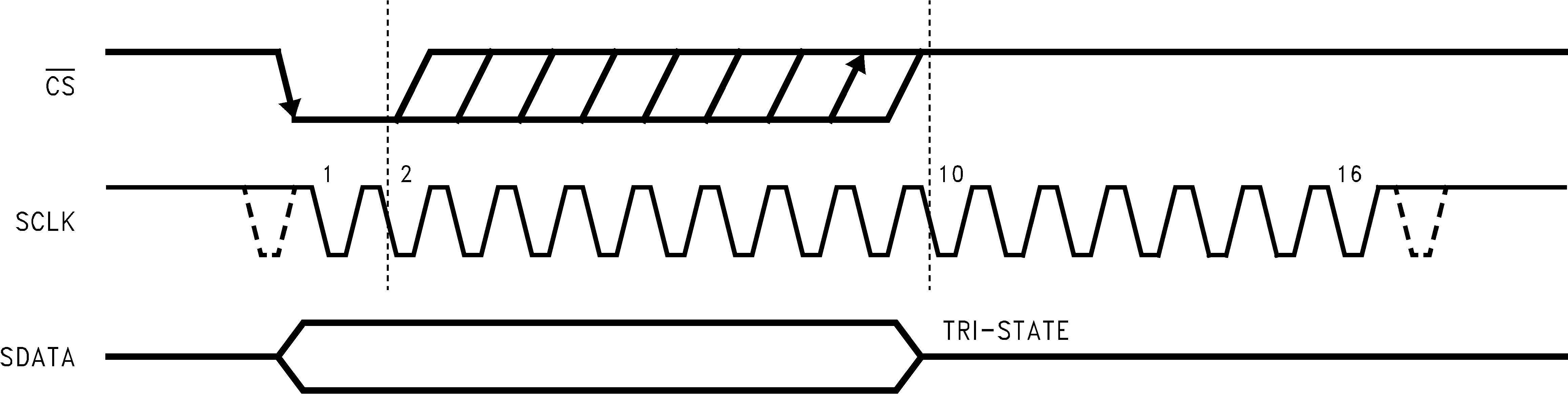

Serial interface timing diagrams for the ADCS747x are shown in Figure 2, Figure 3, and Figure 4. CS is chip select, which initiates conversions and frames the serial data transfers. SCLK (serial clock) controls both the conversion process and the timing of serial data. SDATA is the serial data out pin, where a conversion result is found.

Basic operation of the ADCS747x begins with CS going low, which initiates a conversion process and data transfer. Subsequent rising and falling edges of SCLK will be labeled with reference to the falling edge of CS; for example, the third falling edge of SCLK shall refer to the third falling edge of SCLK after CS goes low.

At the fall of CS, the SDATA pin comes out of TRI-STATE, and the converter moves from track mode to hold mode. The input signal is sampled and held for conversion at the falling edge of CS. The converter moves from hold mode to track mode on the 13th rising edge of SCLK (see Figure 2, Figure 3, or Figure 4). The SDATA pin is placed back into TRI-STATE after the 16th falling edge of SCLK, or at the rising edge of CS, whichever occurs first. After a conversion is completed, the quiet time tQUIET must be satisfied before bringing CS low again to begin another conversion.

Sixteen SCLK cycles are required to read a complete sample from the ADCS747x. The sample bits (including any leading or trailing zeroes) are clocked out on falling edges of SCLK, and are intended to be clocked in by a receiver on subsequent falling edges of SCLK. ADCS747x produces four leading zeroes on SDATA, followed by twelve, ten, or eight data bits (the most significant first). After the data bits, the ADCS7477 clocks out two trailing zeros, and the ADCS7478 clocks out four trailing zeros. The ADCS7476 does not clock out any trailing zeros; the least significant data bit is valid on the 16th falling edge of SCLK.

Depending upon the application, the first edge on SCLK after CS goes low may be either a falling edge or a rising edge. If the first SCLK edge after CS goes low is a rising edge, all four leading zeroes are valid on the first four falling edges of SCLK. If instead the first SCLK edge after CS goes low is a falling edge, the first leading zero may not be set up in time for a microprocessor or DSP to read it correctly. The remaining data bits are still clocked out on the falling edges of SCLK.

7.4 Device Functional Modes

Figure 25 shows the device in hold mode where the switch SW1 connects the sampling capacitor to ground, maintaining the sampled voltage, and switch SW2 unbalances the comparator. The control logic then instructs the charge-redistribution DAC to add or subtract fixed amounts of charge from the sampling capacitor until the comparator is balanced. When the comparator is balanced, the digital word supplied to the DAC is the digital representation of the analog input voltage. The device moves from hold mode to track mode (Figure 26) on the 13th rising edge of SCLK.

Figure 25. ADCS747x in Hold Mode

Figure 25. ADCS747x in Hold Mode

Figure 26. ADCS747x in Track Mode

Figure 26. ADCS747x in Track Mode

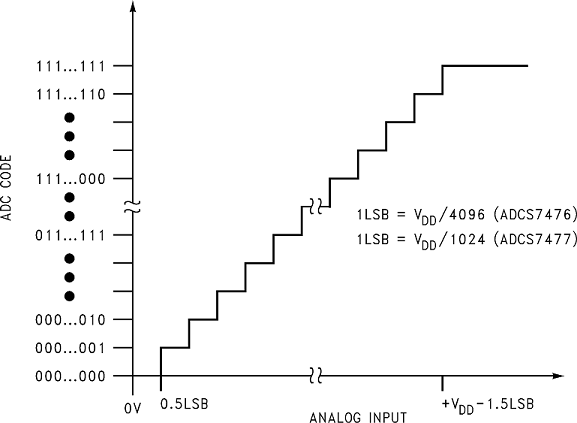

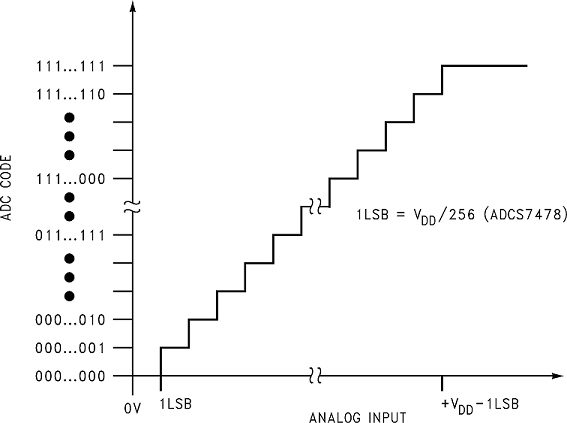

7.4.1 Transfer Function

The output format of ADCS747x is straight binary. Code transitions occur midway between successive integer LSB values. The LSB widths for the ADCS7476 is VDD / 4096; for the ADCS7477 the LSB width is VDD / 1024; for the ADCS7478, the LSB width is VDD / 256. The ideal transfer characteristic for the ADCS7476 and ADCS7477 is shown in Figure 27, while the ideal transfer characteristic for the ADCS7478 is shown in Figure 28.

Figure 27. ADCS7476/77 Ideal Transfer Characteristic

Figure 27. ADCS7476/77 Ideal Transfer Characteristic

Figure 28. ADCS7478 Ideal Transfer Characteristic

Figure 28. ADCS7478 Ideal Transfer Characteristic

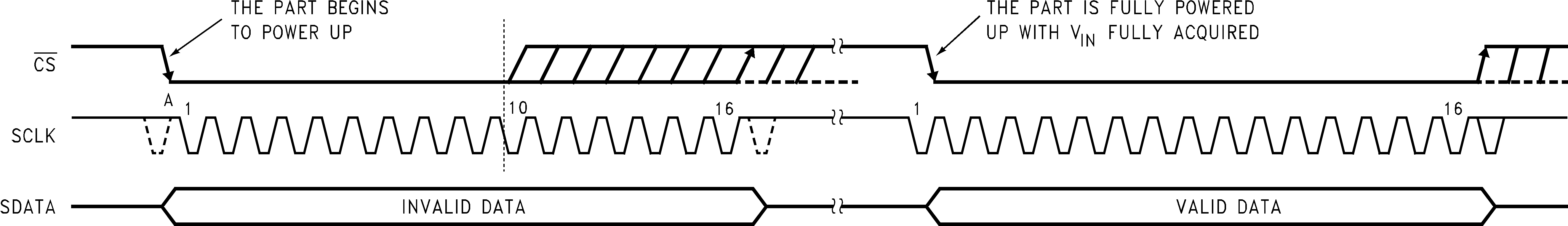

7.4.2 Power-Up Timing

The ADCS747x typically requires 1 µs to power up, either after first applying VDD, or after returning to normal mode from shutdown mode. This corresponds to one dummy conversion for any SCLK frequency within the specifications in this document. After this first dummy conversion, the ADCS747x performs conversions properly.

NOTE

The tQUIET time must still be included between the first dummy conversion and the second valid conversion.

7.4.3 Modes of Operation

The ADCS747x has two possible modes of operation: Normal Mode and Shutdown Mode. ADCS747x enters normal mode (and a conversion process is begun) when CS is pulled low. The device enters shutdown mode if CS is pulled high before the tenth falling edge of SCLK after CS is pulled low, or stays in normal mode if CS remains low. Once in shutdown mode, the device stays there until CS is brought low again. By varying the ratio of time spent in the normal and shutdown modes, a system may trade off throughput for power consumption.

7.4.3.1 Normal Mode

The best possible throughput is obtained by leaving the ADCS747x in normal mode at all times, so there are no power-up delays. To keep the device in normal mode continuously, CS must be kept low until after the 10th falling edge of SCLK after the start of a conversion (remember that a conversion is initiated by bringing CS low).

If CS is brought high after the 10th falling edge, but before the 16th falling edge, the device remains in normal mode, but the current conversion is aborted, and SDATA returns to TRI-STATE (truncating the output word).

Sixteen SCLK cycles are required to read all of a conversion word from the device. After sixteen SCLK cycles have elapsed, CS may be idled either high or low until the next conversion. If CS is idled low, it must be brought high again before the start of the next conversion, which begins when CS is again brought low.

After sixteen SCLK cycles, SDATA returns to TRI-STATE. Another conversion may be started, after tQUIET has elapsed, by bringing CS low again.

7.4.3.2 Start-Up Mode

When the VDD supply is first applied, the ADCS747x may power up in either of the two modes: normal or shutdown. As such, one dummy conversion should be performed after start-up, exactly as described in Power-Up Timing. The part may then be placed into either normal mode or the shutdown mode, as described in Normal Mode and Shutdown Mode.

7.4.3.3 Shutdown Mode

Shutdown mode is appropriate for applications that either do not sample continuously, or are willing to trade throughput for power consumption. When the ADCS747x is in shutdown mode, all of the analog circuitry is turned off.

To enter shutdown mode, a conversion must be interrupted by bringing CS back high anytime between the second and tenth falling edges of SCLK, as shown in Figure 29. Once CS has been brought high in this manner, the device enters shutdown mode; the current conversion is aborted and SDATA enters TRI-STATE. If CS is brought high before the second falling edge of SCLK, the device does not change mode; this is to avoid accidentally changing mode as a result of noise on the CS line.

Figure 29. Entering Shutdown Mode

Figure 29. Entering Shutdown Mode

Figure 30. Entering Normal Mode

Figure 30. Entering Normal Mode

To exit shutdown mode, bring CS back low. Upon bringing CS low, the ADCS747x begins powering up. Power up typically takes 1 µs. This microsecond of power-up delay results in the first conversion result being unusable. The second conversion performed after power-up, however, is valid, as shown in Figure 30.

If CS is brought back high before the 10th falling edge of SCLK, the device returns to shutdown mode. This is done to avoid accidentally entering normal mode as a result of noise on the CS line. To exit shutdown mode and remain in normal mode, CS must be kept low until after the 10th falling edge of SCLK. The ADCS747x is fully powered up after 16 SCLK cycles.