Typical values at TA =

+25°C with nominal supplies. Unless otherwise noted, TX input data rate = 491.52

MSPS, fDAC = 11796.48 MSPS, interleave mode, AOUT = –1

dBFS, 1st Nyquist zone output, Internal PLL, fREF = 491.52

MSPS, 24x Interpolation, DSA = 0 dB, Sin(x)/x enabled, DSA calibrated

| Aout = -0.5 dFBS, 3.5 GHz Matching,

included PCB and cable losses |

|

Figure 6-444 TX

Output Power vs DSA Setting at 3.5 GHz

| 3.5

GHz Matching, included PCB and cable losses |

| Differential Gain Error = POUT(DSA Setting –

1) – POUT(DSA Setting) + 1 |

Figure 6-446 TX

Uncalibrated Differential Gain Error vs DSA Setting and Channel at 3.5

GHz

| 3.5

GHz Matching, included PCB and cable losses |

| Integrated Gain Error = POUT(DSA Setting) –

POUT(DSA Setting = 0) + (DSA

Setting) |

Figure 6-448 TX

Uncalibrated Integrated Gain Error vs DSA Setting and Channel at 3.5

GHz

| 3.5

GHz Matching, included PCB and cable losses |

| Differential Phase Error = PhaseOUT(DSA

Setting – 1) – PhaseOUT(DSA Setting) |

Figure 6-450 TX

Uncalibrated Differential Phase Error vs DSA Setting and Channel at 3.5

GHz

| 3.5

GHz Matching, included PCB and cable losses |

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 6-452 TX

Uncalibrated Integrated Phase Error vs DSA Setting and Channel at 3.5

GHz

| 3.5

GHz Matching, 1TX |

| Differential Phase Error = PhaseOUT(DSA

Setting – 1) – PhaseOUT(DSA Setting) |

Figure 6-454 TX

Uncalibrated Differential Gain Error vs DSA Setting and Temperature at 3.5

GHz

| 3.5

GHz Matching, 1TX |

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 6-456 TX

Uncalibrated Integrated Gain Error vs DSA Setting and Temperature at 3.5

GHz

| 3.5

GHz Matching, 1TX |

| Differential Phase Error = PhaseOUT(DSA

Setting – 1) – PhaseOUT(DSA Setting) |

Figure 6-458 TX

Uncalibrated Differential Phase Error vs DSA setting and Temperature at 3.5

GHz

| 3.5

GHz Matching, 1TX |

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting=0) |

Figure 6-460 TX

Uncalibrated Integrated Phase Error vs DSA Setting and Temperature at 3.5

GHz

A.

| fDAC = 11796.48 MSPS, interleave mode,

matching at 3.5 GHz, Aout = –13 dBFS. |

|

Figure 6-462 TX

NSD vs DSA Setting at 3.5 GHz

A.

| fDAC = 12 MSPS, external clock mode,

non-interleave mode |

|

Figure 6-464 TX

NSD vs Digital Amplitude and Channel at 3.75 GHz

| 20-MHz

tone spacing, 3.5 GHz Matching |

|

Figure 6-466 TX

IMD3 vs Digital Amplitude and Channel at 3.5 GHz

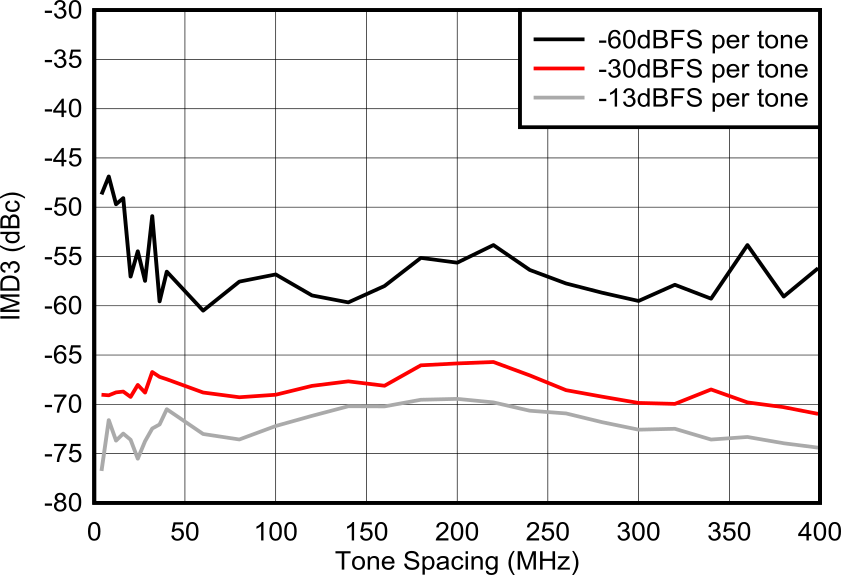

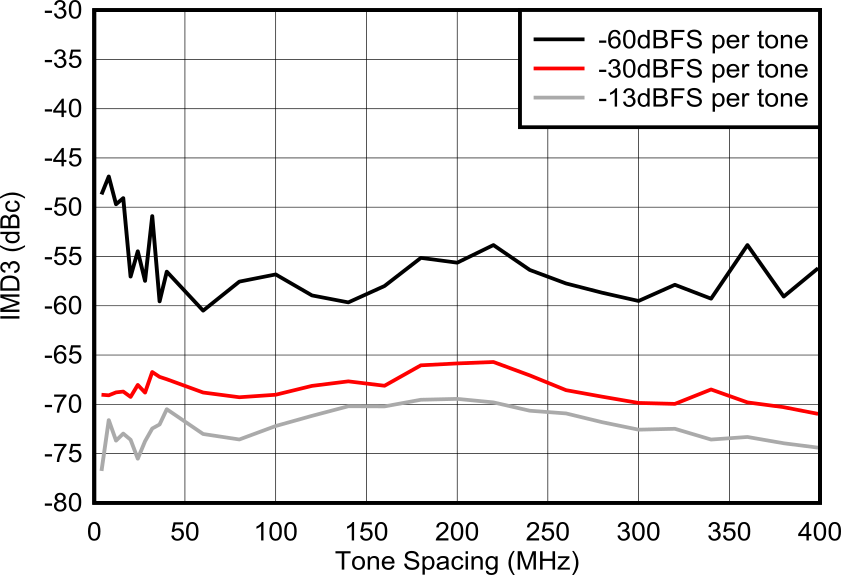

| 50-MHz

tone spacing, external clock mode, non-interleave

mode |

|

Figure 6-468 TX

IMD3 vs Tone Spacing and Channel at 3.75 GHz

| 50-MHz

tone spacing, external clock mode, non-interleave

mode |

|

Figure 6-470 TX

IMD3 vs Digital Amplitude and Dither at 3.75 GHz

| 3.5

GHz Matching, single carrier 20-MHz BW TM1.1 LTE |

Figure 6-472 TX

20-MHz LTE Output Spectrum at 3.5 GHz (Band 42)

| 3.5

GHz Matching, single carrier 100-MHz BW NR TM1.1 |

Figure 6-474 TX 2

carrier 100-MHz NR Output Spectrum at 3.45 GHz and 3.75 GHz

| 3.5

GHz Matching, single carrier 20-MHz BW TM1.1 LTE |

Figure 6-476 TX

20-MHz LTE alt-ACPR vs DSA Setting at 3.5 GHz

| 3.5

GHz Matching, single carrier 100-MHz BW NR TM1.1 |

Figure 6-478 TX

100-MHz NR alt-ACPR vs DSA Setting at 3.5 GHz

| 3.5

GHz Matching, single carrier 20-MHz BW TM1.1 LTE |

Figure 6-480 TX

20-MHz LTE alt-ACPR vs Digital Level at 3.5 GHz

| 3.5

GHz Matching, single carrier 100-MHz BW NR TM1.1 |

|

Figure 6-482 TX

100-MHz NR alt-ACPR vs Digital Level at 3.5 GHz

| Matching at 3.5 GHz, fDAC = 11.79648 GSPS,

interleave mode, normalized to output power at harmonic

frequency. Dip is due to HD3 falling near DC. |

Figure 6-484 TX

Single Tone HD3 vs Frequency and Digital Level at 3.5 GHz

| Matching at 3.5 GHz, fDAC = 11.79648 GSPS,

interleave mode. |

Figure 6-486 TX

Single Tone (–1 dBFS) Output Spectrum at 3.5 GHz (±300 MHz)

| Matching at 3.5 GHz, fDAC = 11.79648 GSPS,

interleave mode. |

Figure 6-488 TX

Single Tone (–6 dBFS) Output Spectrum at 3.5 GHz (±300 MHz)

| Matching at 3.5 GHz, fDAC = 11.79648 GSPS,

interleave mode. |

|

Figure 6-490 TX

Single Tone (–12 dBFS) Output Spectrum at 3.5 GHz (±300 MHz)

| Matching at 3.5 GHz, 50 MHz tone spacing,

fDAC = 12 GSPS, non-interleave

mode. |

|

Figure 6-492 TX

Dual Tone Output Spectrum at 3.75 GHz, -7 dBFS each (±600 MHz)

| Matching at 3.5 GHz, 50 MHz tone spacing,

fDAC = 12 GSPS, non-interleave

mode. |

|

Figure 6-494 TX

Dual Tone Output Spectrum at 3.75 GHz, -13 dBFS each (±600 MHz)

| Matching at 3.5 GHz, 50 MHz tone spacing,

fDAC = 12 GSPS, non-interleave

mode. |

|

Figure 6-496 TX

Dual Tone Output Spectrum at 3.75 GHz, -30 dBFS each (±600 MHz)

| Aout = -0.5 dFBS, 3.5 GHz Matching,

included PCB and cable losses |

|

|

Figure 6-445 TX

Output Power vs Frequency

| 3.5

GHz Matching, included PCB and cable losses |

| Differential Gain Error = POUT(DSA Setting –

1) – POUT(DSA Setting) + 1 |

Figure 6-447 TX

Calibrated Differential Gain Error vs DSA Setting and Channel at 3.5

GHz

| 3.5

GHz Matching, included PCB and cable losses |

| Integrated Gain Error = POUT(DSA Setting) –

POUT(DSA Setting = 0) + (DSA

Setting) |

Figure 6-449 TX

Calibrated Integrated Gain Error vs DSA Setting and Channel at 3.5

GHz

| 3.5

GHz Matching, included PCB and cable losses |

| Differential Phase Error = PhaseOUT(DSA

Setting – 1) – PhaseOUT(DSA Setting). Phase

DNL spike may occur at any DSA setting. |

Figure 6-451 TX

Calibrated Differential Phase Error vs DSA Setting and Channel at 3.5

GHz

| 3.5

GHz Matching, included PCB and cable losses |

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 6-453 TX

Calibrated Integrated Phase Error vs DSA Setting and Channel at 3.5

GHz

| 3.5

GHz Matching, 1TX, Calibrated at 25°C |

| Differential Phase Error = PhaseOUT(DSA

Setting – 1) – PhaseOUT(DSA Setting) |

Figure 6-455 TX

Calibrated Differential Gain Error vs DSA Setting and Temperature at 3.5

GHz

| 3.5

GHz Matching, 1TX, Calibrated at 25°C |

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 6-457 TX

Calibrated Integrated Gain Error vs DSA Setting and Temperature at 3.5

GHz

| 3.5

GHz Matching, 1TX, Calibrated at 25°C |

| Differential Phase Error = PhaseOUT(DSA

Setting – 1) – PhaseOUT(DSA Setting) |

Figure 6-459 TX

Calibrated Differential Phase Error vs DSA Setting and Temperature at 3.5

GHz

| 3.5

GHz Matching, 1TX, Calibrated at 25°C |

| Integrated Phase Error = Phase(DSA Setting) – Phase(DSA

Setting = 0) |

Figure 6-461 TX

Calibrated Integrated Phase Error vs DSA Setting and Temperature at 3.5

GHz

A.

| fDAC = 12 MSPS, external clock mode,

non-interleave mode |

|

Figure 6-463 TX

NSD vs Digital Amplitude and Temperature at 3.75 GHz

| 20-MHz

tone spacing, 3.5 GHz Matching, –13 dBFS each tone,

included PCB and cable losses |

|

Figure 6-465 TX

IMD3 vs DSA Setting at 3.5 GHz

| 50-MHz

tone spacing, external clock mode, non-interleave

mode |

|

Figure 6-467 TX

IMD3 vs Tone Spacing and Amplitude at 3.75 GHz

| 50-MHz

tone spacing, external clock mode, non-interleave

mode |

|

Figure 6-469 TX

IMD3 vs Digital Amplitude and Temperature at 3.75 GHz

| Inband

= 3.75 GHz ± 600 MHz, fDAC = 9 GSPS, external

clock mode, non-interleave mode. |

|

Figure 6-471 Two

Tone Inband SFDR vs Digital Amplitude at 3.75 GHz

| 3.5

GHz Matching, single carrier 100-MHz BW NR TM1.1 |

Figure 6-473 TX

100-MHz NR Output Spectrum at 3.5 GHz (Band 42)

| 3.5

GHz Matching, single carrier 20-MHz BW TM1.1 LTE |

|

|

|

|

Figure 6-475 TX

20-MHz LTE ACPR vs DSA Setting at 3.5 GHz

| 3.5

GHz Matching, single carrier 100-MHz BW NR TM1.1 |

Figure 6-477 TX

100-MHz NR ACPR vs DSA Setting at 3.5 GHz

| 3.5

GHz Matching, single carrier 20-MHz BW TM1.1 LTE |

|

Figure 6-479 TX

20-MHz LTE ACPR vs Digital Level at 3.5 GHz

| 3.5

GHz Matching, single carrier 100-MHz BW NR TM1.1 |

Figure 6-481 TX

100-MHz NR ACPR vs Digital Level at 3.5 GHz

| Matching at 3.5 GHz, fDAC = 11.79648GSPS,

interleave mode, normalized to output power at harmonic

frequency |

Figure 6-483 TX

Single Tone HD2 vs Frequency and Digital Level at 3.5 GHz

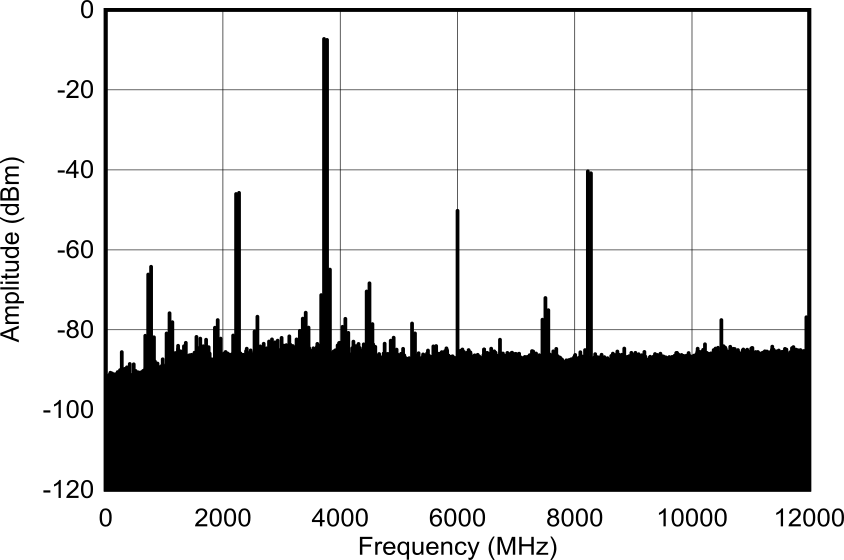

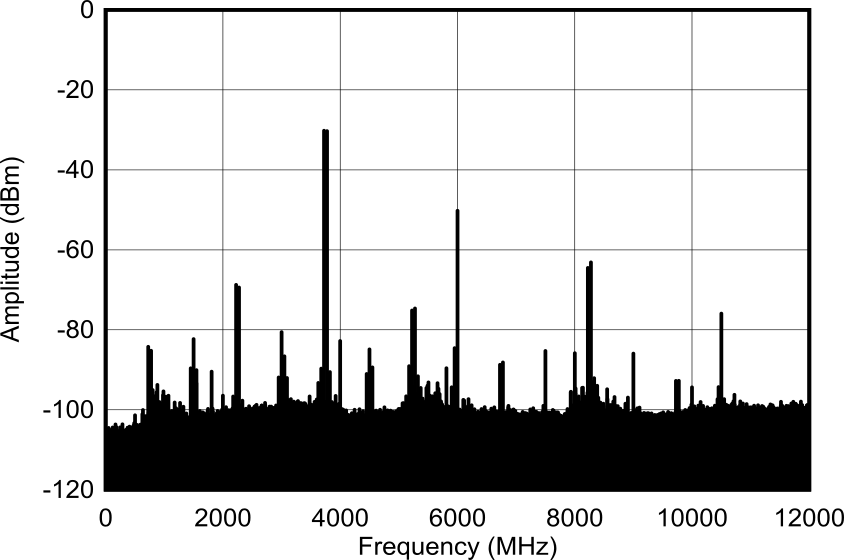

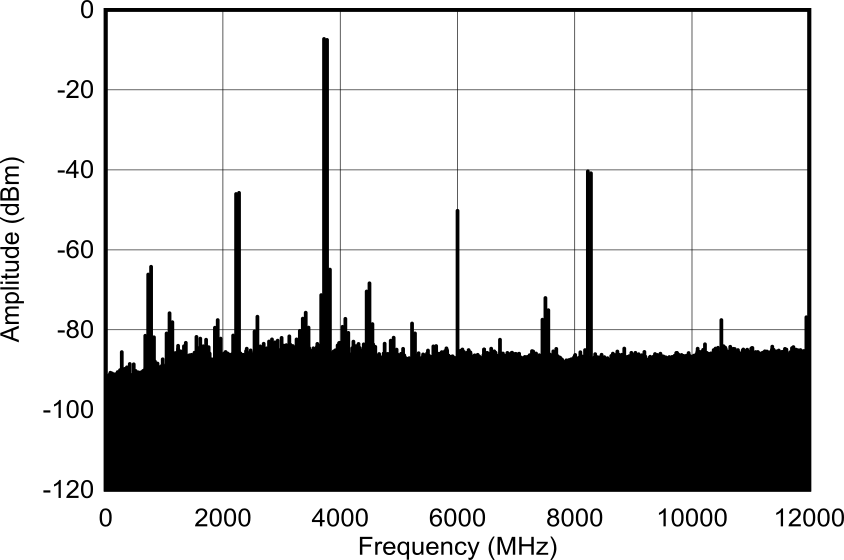

| Matching at 3.5 GHz, fDAC = 11.79648 GSPS,

interleave mode. |

|

Figure 6-485 TX

Single Tone (–1 dBFS) Output Spectrum at 3.5 GHz (0 -

fDAC)

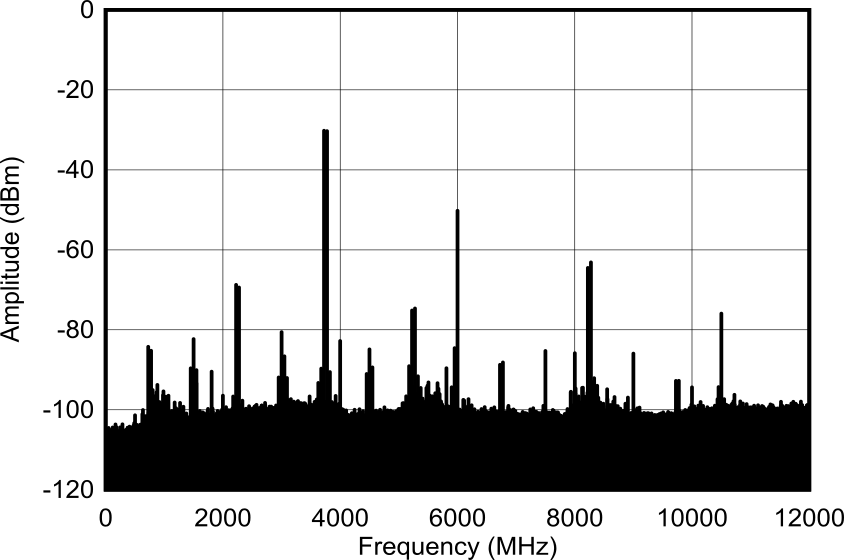

| Matching at 3.5 GHz, fDAC = 11.79648 GSPS,

interleave mode. |

Figure 6-487 TX

Single Tone (–6 dBFS) Output Spectrum at 3.5 GHz (0-fDAC)

| Matching at 3.5 GHz, fDAC = 11.79648 GSPS,

interleave mode. |

Figure 6-489 TX

Single Tone (–12 dBFS) Output Spectrum at 3.5 GHz

(0-fDAC)

| Matching at 3.5 GHz, 50MHz tone spacing,

fDAC = 12GSPS, non-interleave

mode. |

|

Figure 6-491 TX

Dual Tone Output Spectrum at 3.75 GHz, -7 dBFS each (0 -

fDAC)

| Matching at 3.5 GHz, 50 MHz tone spacing,

fDAC = 12 GSPS, non-interleave

mode. |

|

Figure 6-493 TX

Dual Tone Output Spectrum at 3.75 GHz, -13 dBFS each (0 -

fDAC)

| Matching at 3.5 GHz, 50 MHz tone spacing,

fDAC = 12 GSPS, non-interleave

mode. |

|

Figure 6-495 TX

Dual Tone Output Spectrum at 3.75 GHz, -30 dBFS each (0 -

fDAC)

| fDAC = fCLK = 12 GSPS,

non-interleave mode. |

|

Figure 6-497 External Clock Additive Phase Noise at 3.7 GHz