SLUSDO1B june 2019 – august 2023 BQ25155

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Device Key Default Settings

- 7 Pin Configuration and Functions

- 8 Specifications

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Linear Charger and Power Path

- 9.3.2 Protection Mechanisms

- 9.3.3 ADC

- 9.3.4 VDD LDO

- 9.3.5 Load Switch/LDO Output and Control

- 9.3.6 PMID Power Control

- 9.3.7 System Voltage (PMID) Regulation

- 9.3.8 MR Wake and Reset Input

- 9.3.9 14-Second Watchdog for HW Reset

- 9.3.10 Faults Conditions and Interrupts ( INT)

- 9.3.11 Power Good ( PG) Pin

- 9.3.12 External NTC Monitoring (TS)

- 9.3.13 External NTC Monitoring (ADCIN)

- 9.3.14 I2C Interface

- 9.4 Device Functional Modes

- 9.5 Register Map

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- YFP|20

Thermal pad, mechanical data (Package|Pins)

Orderable Information

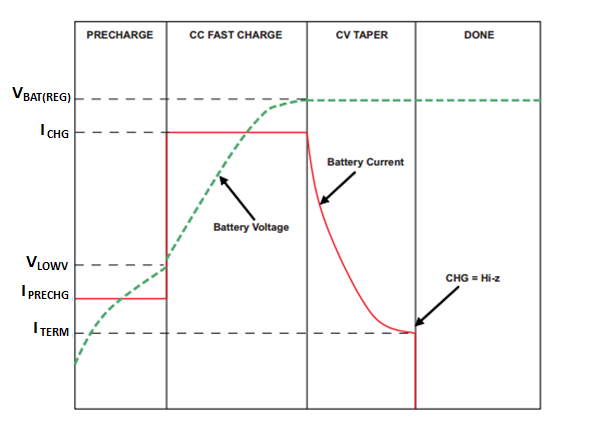

9.3.1.1 Battery Charging Process

The following diagram summarizes the charging process of the BQ25155 charger.

Figure 9-1 BQ25155 Charger Flow Diagram

Figure 9-1 BQ25155 Charger Flow DiagramWhen a valid input source is connected (VIN > VUVLO and VBAT+VSLP < VIN < VOVP), the state of the CE pin determines whether a charge cycle is initiated. When the CE input is high and a valid input source is connected, the battery charge FET is turned off, preventing any kind of charging of the battery. A charge cycle is initiated when the CHARGE_DISABLE bit is written to 0 and CE pin in low. Table 9-1 shows the CE pin and bit priority to enable/disable charging.

Table 9-1 Charge Enable Function Through

CE Pin and

CE Bit

| CE PIN | CHARGE _DISABLE BIT | CHARGING |

|---|---|---|

| 0 | 0 | Enabled |

| 0 | 1 | Disabled |

| 1 | 0 | Disabled |

| 1 | 1 | Disabled |

Figure 9-2 shows a typical charge cycle.

Figure 9-2 BQ25155 Typical Charge Cycle

Figure 9-2 BQ25155 Typical Charge Cycle