SNLS398H January 2012 – February 2018 DS125DF410

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5

Programming

- 7.5.1 SMBus Strap Observation

- 7.5.2 Device Revision and Device ID

- 7.5.3 Control/Shared Register Reset

- 7.5.4 Interrupt Channel Flag Bits

- 7.5.5 SMBus Master Mode Control Bits

- 7.5.6 Resetting Individual Channels of the Retimer

- 7.5.7 Interrupt Status

- 7.5.8 Overriding the CTLE Boost Setting

- 7.5.9 Overriding the VCO Search Values

- 7.5.10 Overriding the Output Multiplexer

- 7.5.11 Overriding the VCO Divider Selection

- 7.5.12 Using the PRBS Generator

- 7.5.13 Using the Internal Eye Opening Monitor

- 7.5.14 Overriding the DFE Tap Weights and Polarities

- 7.5.15 Enabling Slow Rise/Fall Time on the Output Driver

- 7.5.16 Inverting the Output Polarity

- 7.5.17 Overriding the Figure of Merit for Adaptation

- 7.5.18 Setting the Rate and Subrate for Lock Acquisition

- 7.5.19 Setting the Adaptation/Lock Mode

- 7.5.20 Initiating Adaptation

- 7.5.21 Setting the Reference Enable Mode

- 7.5.22 Overriding the CTLE Settings Used for CTLE Adaptation

- 7.5.23 Setting the Output Differential Voltage

- 7.5.24 Setting the Output De-Emphasis Setting

- 7.6 Register Maps

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RHS|48

Thermal pad, mechanical data (Package|Pins)

- RHS|48

Orderable Information

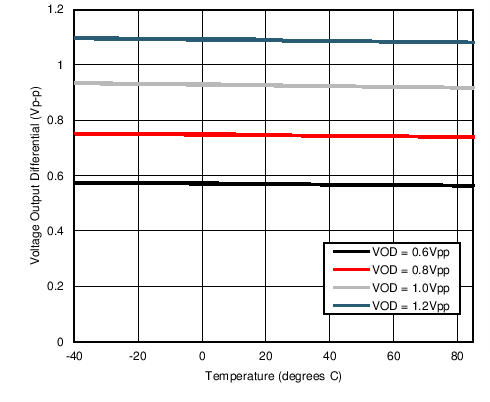

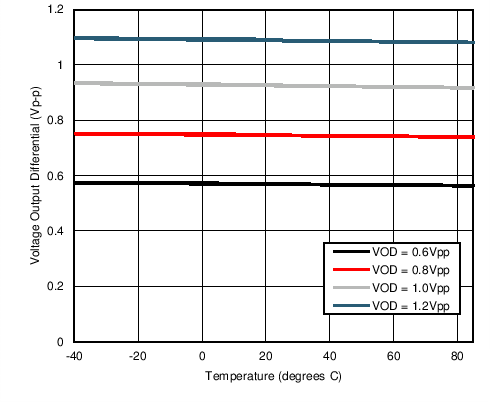

6.6 Typical Characteristics

Figure 1. Typical VOD vs VDD

Figure 1. Typical VOD vs VDD Figure 2. Typical VOD vs Temperature

Figure 2. Typical VOD vs Temperature