SNLS044D May 2000 – July 2016 DS90LV047A

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

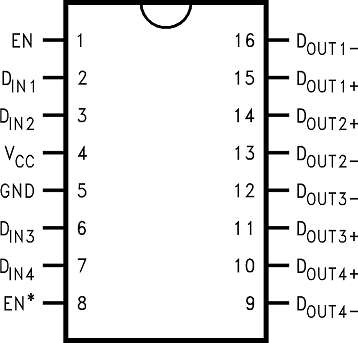

5 Pin Configuration and Functions

D or PW Package

16-Pin SOIC or TSSOP

Top View

Pin Functions

| PIN | I/O | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| DIN | 2, 3, 6, 7 | I | Driver input pin, TTL/CMOS compatible |

| DOUT+ | 10, 11, 14, 15 | O | Non-inverting driver output pin, LVDS levels |

| DOUT− | 9, 12, 13, 16 | O | Inverting driver output pin, LVDS levels |

| EN | 1 | I | Driver enable pin: When EN is low, the driver is disabled. When EN is high and EN* is low or open, the driver is enabled. If both EN and EN* are open circuit, then the driver is disabled. |

| EN* | 8 | I | Driver enable pin: When EN* is high, the driver is disabled. When EN* is low or open and EN is high, the driver is enabled. If both EN and EN* are open circuit, then the driver is disabled. |

| GND | 5 | — | Ground pin |

| VCC | 4 | — | Power supply pin, +3.3 V ± 0.3 V |