SNLS624 September 2018 DSLVDS1048

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PW|16

Thermal pad, mechanical data (Package|Pins)

Orderable Information

9.2.2.2 Threshold

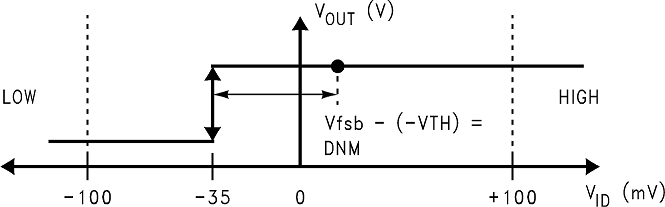

The LVDS Standard (ANSI/TIA/EIA-644) specifies a maximum threshold of ±100 mV for the LVDS receiver. The DSLVDS1048 supports an enhanced threshold region of −100 mV to 0 V. This is useful for fail-safe biasing. The threshold region is shown in the Voltage Transfer Curve (VTC) in Figure 20. The typical DSLVDS1048 LVDS receiver switches at about −35 mV.

NOTE

With VID = 0 V, the output is in a HIGH state. With an external fail-safe bias of +25 mV applied, the typical differential noise margin is now the difference from the switch point to the bias point.

In the following example, this would be 60 mV of Differential Noise Margin (+25 mV − (−35 mV)). With the enhanced threshold region of −100 mV to 0 V, this small external fail-safe biasing of +25 mV (with respect to

0 V) gives a DNM of a comfortable 60 mV. With the standard threshold region of ±100 mV, the external fail-safe biasing would need to be +25 mV with respect to +100 mV or +125 mV, giving a DNM of 160 mV which is stronger fail-safe biasing than is necessary for the DSLVDS1048. If more DNM is required, then a stronger fail-safe bias point can be set by changing resistor values.

Figure 20. VTC of the DSLVDS1048 LVDS Receiver

Figure 20. VTC of the DSLVDS1048 LVDS Receiver