SNVS709G March 2011 – December 2015 LMZ13610

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 Design Steps

- 8.2.2.2 Enable Divider, RENT, RENB and RENH Selection

- 8.2.2.3 Output Voltage Selection

- 8.2.2.4 Soft-Start Capacitor Selection

- 8.2.2.5 Tracking Supply Divider Option

- 8.2.2.6 COUT Selection

- 8.2.2.7 CIN Selection

- 8.2.2.8 Discontinuous Conduction and Continuous Conduction Modes Selection

- 8.2.3 Application Curves

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- NDY|11

Thermal pad, mechanical data (Package|Pins)

Orderable Information

10 Layout

10.1 Layout Guidelines

PCB layout is an important part of DC-DC converter design. Poor board layout can disrupt the performance of a DC-DC converter and surrounding circuitry by contributing to EMI, ground bounce and resistive voltage drop in the traces. These can send erroneous signals to the DC-DC converter resulting in poor regulation or instability. Good layout can be implemented by following a few simple design rules. A good layout example is shown in Figure 56.

- Minimize area of switched current loops.

- Have a single point ground.

- Minimize trace length to the FB pin.

- Make input and output bus connections as wide as possible.

- Provide adequate device heat-sinking.

From an EMI reduction standpoint, it is imperative to minimize the high di/dt paths during PCB layout as shown in Figure 53. The high current loops that do not overlap have high di/dt content that will cause observable high frequency noise on the output pin if the input capacitor (CIN) is placed at a distance away from the LMZ13610. Therefore place CIN as close as possible to the LMZ13610 VIN and PGND exposed pad. This will minimize the high di/dt area and reduce radiated EMI. Additionally, grounding for both the input and output capacitor must consist of a localized top side plane that connects to the PGND exposed pad (EP).

The ground connections for the feedback, soft-start, and enable components must be routed to the AGND pin of the device. This prevents any switched or load currents from flowing in the analog ground traces. If not properly handled, poor grounding can result in degraded load regulation or erratic output voltage ripple behavior. Additionally provide a single point ground connection from pin 4 (AGND) to EP/PGND.

Both feedback resistors, RFBT and RFBB must be located close to the FB pin. Because the FB node is high impedance, maintain the copper area as small as possible. The traces from RFBT, RFBB must be routed away from the body of the LMZ13610 to minimize possible noise pickup.

This reduces any voltage drops on the input or output of the converter and maximizes efficiency. To optimize voltage accuracy at the load, ensure that a separate feedback voltage sense trace is made to the load. Doing so will correct for voltage drops and provide optimum output accuracy.

Use an array of heat-sinking vias to connect the exposed pad to the ground plane on the bottom PCB layer. If the PCB has multiple copper layers, these thermal vias can also be connected to inner layer heat-spreading ground planes. For best results use a 10 × 10 via array or larger with a minimum via diameter of 8 mil thermal vias spaced 46.8 mil (1.5 mm). Ensure enough copper area is used for heat-sinking to keep the junction temperature below 125°C.

10.2 Layout Examples

Figure 53. Critical Current Loops to Minimize

Figure 53. Critical Current Loops to Minimize

Figure 54. PCB Layout Guide

Figure 54. PCB Layout Guide

Figure 55. Top View of Evaluation PCB

Figure 55. Top View of Evaluation PCB

Figure 56. Bottom View of Evaluation PCB

Figure 56. Bottom View of Evaluation PCB

10.3 Power Dissipation and Thermal Considerations

When calculating module dissipation use the maximum input voltage and the average output current for the application. Many common operating conditions are provided in the characteristic curves such that less common applications can be derived through interpolation. In all designs, the junction temperature must be kept below the rated maximum of 125°C.

For the design case of VIN = 12 V, VOUT = 3.3 V, IOUT = 10 A, and TA-MAX = 50°C, the module must see a thermal resistance from case to ambient (θCA) of less than:

Given the typical thermal resistance from junction to case (θJC) to be 1.0°C/W. Use the 85°C power dissipation curves in the Typical Characteristics section to estimate the PIC-LOSS for the application being designed. In this application it is 5.3 W.

To reach θCA = 13.15, the PCB is required to dissipate heat effectively. With no airflow and no external heat-sink, a good estimate of the required board area covered by 2-oz. copper on both the top and bottom metal layers is:

As a result, approximately 38.02 square cm of 2-oz copper on top and bottom layers is the minimum required area for the example PCB design. This is 6.16 × 6.16 cm (2.42 × 2.42 in) square. The PCB copper heat sink must be connected to the exposed pad. For best performance, use approximately 100, 8 mil thermal vias spaced 59 mil (1.5 mm) apart connect the top copper to the bottom copper.

10.4 Power Module SMT Guidelines

The recommendations below are for a standard module surface mount assembly

- Land Pattern — Follow the PCB land pattern with either soldermask defined or non-soldermask defined pads

- Stencil Aperture

- For the exposed die attach pad (DAP), adjust the stencil for approximately 80% coverage of the PCB land pattern

- For all other I/O pads use a 1:1 ratio between the aperture and the land pattern recommendation

- Solder Paste — Use a standard SAC Alloy such as SAC 305, type 3 or higher

- Stencil Thickness — 0.125 to 0.15 mm

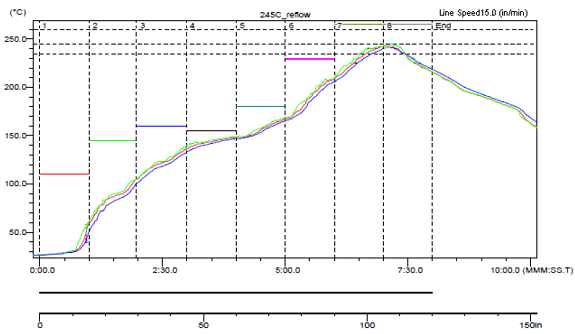

- Reflow — Refer to solder paste supplier recommendation and optimized per board size and density

- Refer AN Design Summary LMZ1xxx and LMZ2xxx Power Modules Family (SNAA214) for reflow information

- Maximum number of reflows allowed is one

Figure 57. Sample Reflow Profile

Figure 57. Sample Reflow Profile

Table 2. Sample Reflow Profile Table

| PROBE | MAX TEMP (°C) | REACHED MAX TEMP | TIME ABOVE 235°C | REACHED 235°C | TIME ABOVE 245°C | REACHED 245°C | TIME ABOVE 260°C | REACHED 260°C |

|---|---|---|---|---|---|---|---|---|

| 1 | 242.5 | 6.58 | 0.49 | 6.39 | 0.00 | – | 0.00 | – |

| 2 | 242.5 | 7.10 | 0.55 | 6.31 | 0.00 | 7.10 | 0.00 | – |

| 3 | 241.0 | 7.09 | 0.42 | 6.44 | 0.00 | – | 0.00 | – |