SLVSF18B March 2021 – November 2021 MCT8316Z

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Output Stage

- 8.3.2 PWM Control Mode (1x PWM Mode)

- 8.3.3 Device Interface Modes

- 8.3.4 Step-Down Mixed-Mode Buck Regulator

- 8.3.5 AVDD Linear Voltage Regulator

- 8.3.6 Charge Pump

- 8.3.7 Slew Rate Control

- 8.3.8 Cross Conduction (Dead Time)

- 8.3.9 Propagation Delay

- 8.3.10 Pin Diagrams

- 8.3.11 Active Demagnetization

- 8.3.12 Cycle-by-Cycle Current Limit

- 8.3.13 Hall Comparators (Analog Hall Inputs)

- 8.3.14 Advance Angle

- 8.3.15 FGOUT Signal

- 8.3.16

Protections

- 8.3.16.1 VM Supply Undervoltage Lockout (NPOR)

- 8.3.16.2 AVDD Undervoltage Lockout (AVDD_UV)

- 8.3.16.3 BUCK Undervoltage Lockout (BUCK_UV)

- 8.3.16.4 VCP Charge Pump Undervoltage Lockout (CPUV)

- 8.3.16.5 Overvoltage Protections (OV)

- 8.3.16.6 Overcurrent Protection (OCP)

- 8.3.16.7 Buck Overcurrent Protection

- 8.3.16.8 Motor Lock (MTR_LOCK)

- 8.3.16.9 Thermal Warning (OTW)

- 8.3.16.10 Thermal Shutdown (OTS)

- 8.4 Device Functional Modes

- 8.5 SPI Communication

- 8.6 Register Map

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

Package Options

Mechanical Data (Package|Pins)

- RGF|40

Thermal pad, mechanical data (Package|Pins)

- RGF|40

Orderable Information

9.3.1.1.2 Using Active Demagnetization

Active demagnetization reduces power losses in the device by turning on the MOSFETs automatically when the body diode starts conducting to reduce diode conduction losses. It is used in trapezoidal commutation when switching commutation states (turning a high-side MOSFET off and another high-side MOSFET on while keeping a low-side MOSFET on). Active demagnetization is enabled when EN_ASR and EN_AAR bits are set in the SPI variant or MODE pin is set to Mode 5, Mode 6, or Mode 7 in the H/W variant.

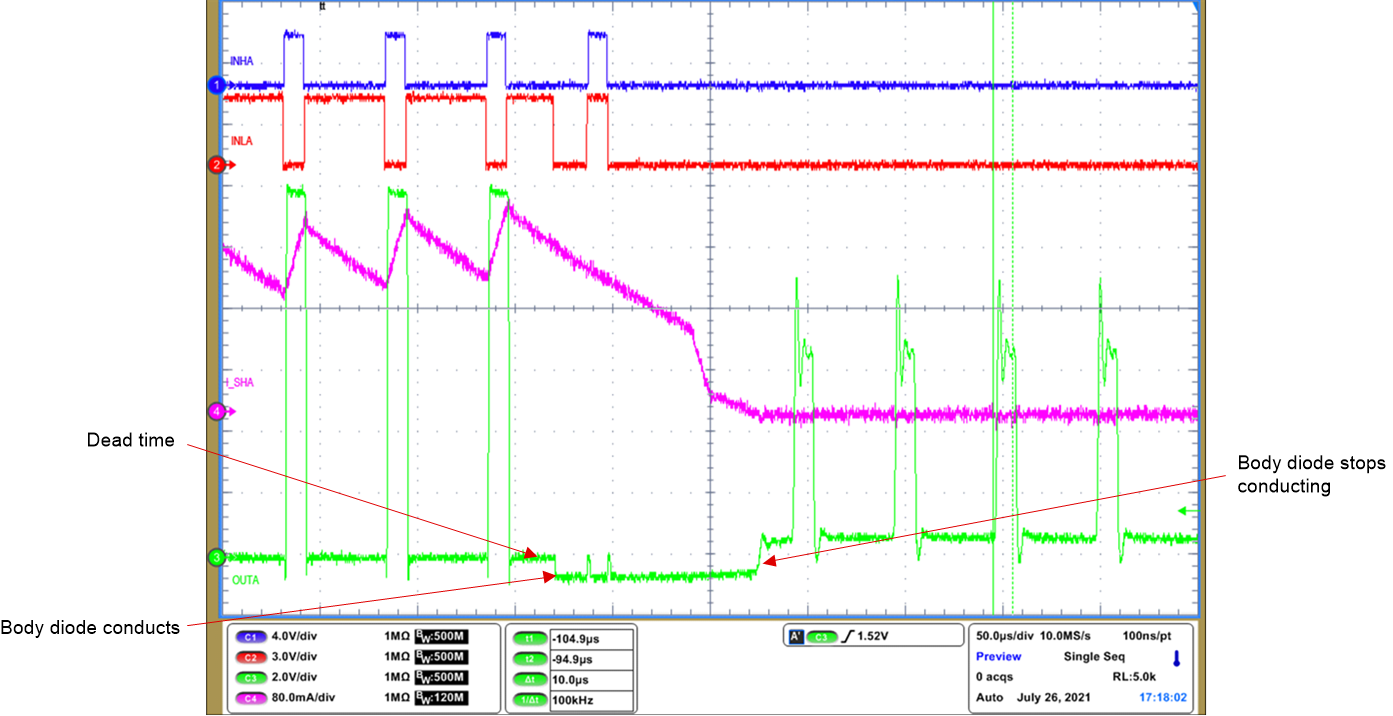

When switching commutation states with active demagnetization disabled, dead time is inserted and the low-side MOSFET’s body diode conducts while turning another high-side MOSFET on to continue sourcing current through the motor. This conduction period causes higher power losses due to the forward-bias voltage of the diode and slower dissipation of current. Figure 9-7 shows the body diode conducting when switching commutation states.

Figure 9-7 Active demagnetization disabled in MCT8316Z

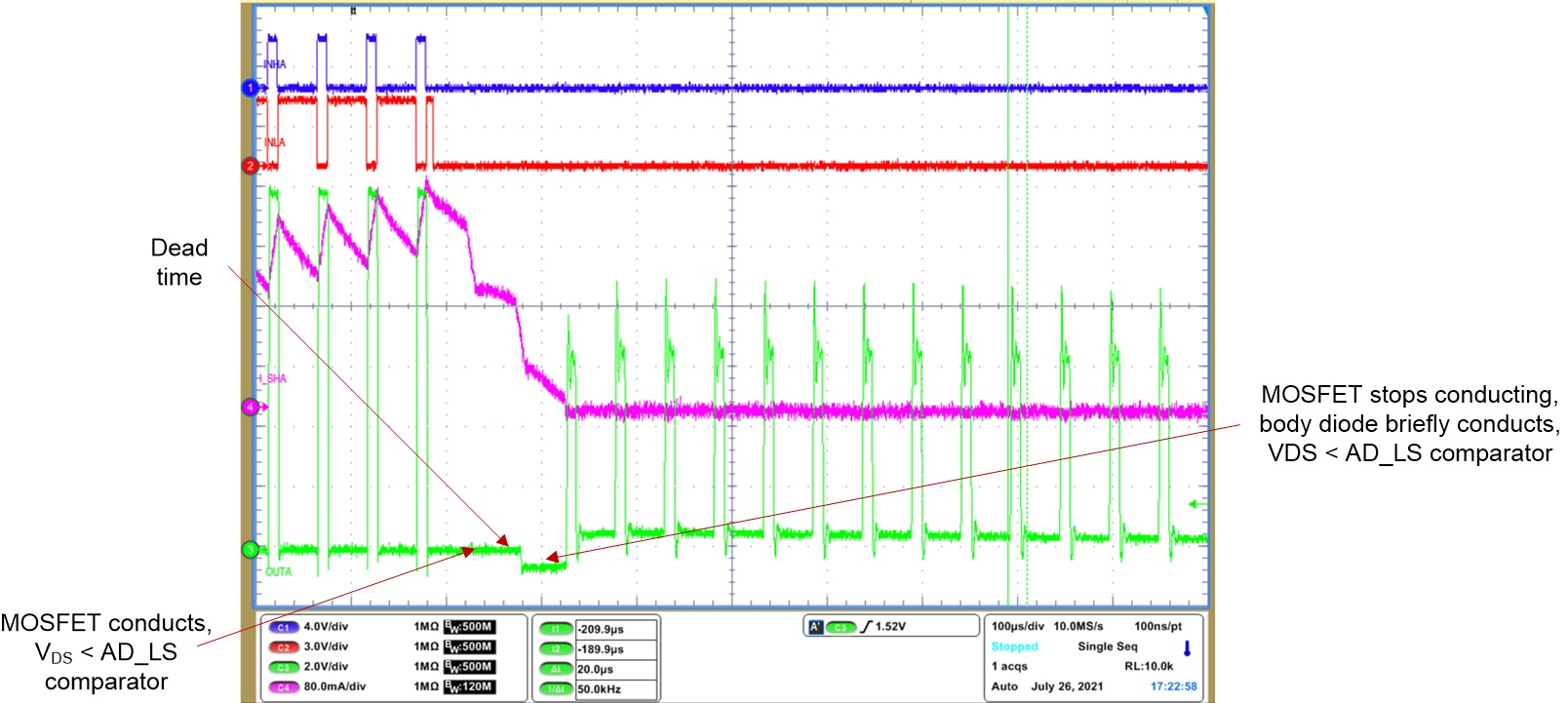

Figure 9-7 Active demagnetization disabled in MCT8316ZWhen active demagnetization is enabled, the AD_HS and AD_LS comparators detect when the sense FET voltage is higher or lower than the programmed threshold. After the dead time period, if the threshold is exceeded for a fixed amount of time, the body diode is conducting and the logic core turns the low-side FET on to provide a conduction path with smaller power losses. Once the VDS voltage is below the comparator threshold, the MOSFET turns off and current briefly conducts through the body diode until the current completely decays to zero. This is shown in Figure 9-8.

Figure 9-8 Active demagnetization enabled in MCT8316Z

Figure 9-8 Active demagnetization enabled in MCT8316Z