SPNS175C April 2012 – June 2015 RM48L540 , RM48L740 , RM48L940

PRODUCTION DATA.

- 1Device Overview

- 2Revision History

- 3Device Comparison

-

4Terminal Configuration and Functions

- 4.1 PGE QFP Package Pinout (144-Pin)

- 4.2 ZWT BGA Package Ball-Map (337-Ball Grid Array)

- 4.3

Terminal Functions

- 4.3.1

PGE Package

- 4.3.1.1 Multibuffered Analog-to-Digital Converters (MibADCs)

- 4.3.1.2 Enhanced Next Generation High-End Timer (N2HET) Modules

- 4.3.1.3 General-Purpose Input/Output (GPIO)

- 4.3.1.4 Controller Area Network Controllers (DCANs)

- 4.3.1.5 Local Interconnect Network Interface Module (LIN)

- 4.3.1.6 Standard Serial Communication Interface (SCI)

- 4.3.1.7 Inter-Integrated Circuit Interface Module (I2C)

- 4.3.1.8 Standard Serial Peripheral Interface (SPI)

- 4.3.1.9 Multibuffered Serial Peripheral Interface Modules (MibSPI)

- 4.3.1.10 Ethernet Controller

- 4.3.1.11 System Module Interface

- 4.3.1.12 Clock Inputs and Outputs

- 4.3.1.13 Test and Debug Modules Interface

- 4.3.1.14 Flash Supply and Test Pads

- 4.3.1.15 Supply for Core Logic: 1.2-V Nominal

- 4.3.1.16 Supply for I/O Cells: 3.3-V Nominal

- 4.3.1.17 Ground Reference for All Supplies Except VCCAD

- 4.3.2

ZWT Package

- 4.3.2.1 Multibuffered Analog-to-Digital Converters (MibADCs)

- 4.3.2.2 Enhanced Next Generation High-End Timer (N2HET) Modules

- 4.3.2.3 General-Purpose Input/Output (GPIO)

- 4.3.2.4 Controller Area Network Controllers (DCANs)

- 4.3.2.5 Local Interconnect Network Interface Module (LIN)

- 4.3.2.6 Standard Serial Communication Interface (SCI)

- 4.3.2.7 Inter-Integrated Circuit Interface Module (I2C)

- 4.3.2.8 Standard Serial Peripheral Interface (SPI)

- 4.3.2.9 Multibuffered Serial Peripheral Interface Modules (MibSPI)

- 4.3.2.10 Ethernet Controller

- 4.3.2.11 External Memory Interface (EMIF)

- 4.3.2.12 Embedded Trace Macrocell for Cortex-R4F CPU (ETM-R4F)

- 4.3.2.13 RAM Trace Port (RTP)

- 4.3.2.14 Data Modification Module (DMM)

- 4.3.2.15 System Module Interface

- 4.3.2.16 Clock Inputs and Outputs

- 4.3.2.17 Test and Debug Modules Interface

- 4.3.2.18 Flash Supply and Test Pads

- 4.3.2.19 Reserved

- 4.3.2.20 No Connects

- 4.3.2.21 Supply for Core Logic: 1.2-V Nominal

- 4.3.2.22 Supply for I/O Cells: 3.3-V Nominal

- 4.3.2.23 Ground Reference for All Supplies Except VCCAD

- 4.3.1

PGE Package

-

5Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Power-On Hours (POH)

- 5.4 Recommended Operating Conditions

- 5.5 Switching Characteristics for Clock Domains

- 5.6 Wait States Required

- 5.7 Power Consumption

- 5.8 Input/Output Electrical Characteristics

- 5.9 Thermal Resistance Characteristics

- 5.10 Output Buffer Drive Strengths

- 5.11 Input Timings

- 5.12 Output Timings

- 5.13 Low-EMI Output Buffers

-

6System Information and Electrical Specifications

- 6.1 Device Power Domains

- 6.2 Voltage Monitor Characteristics

- 6.3 Power Sequencing and Power On Reset

- 6.4 Warm Reset (nRST)

- 6.5 ARM Cortex-R4F CPU Information

- 6.6 Clocks

- 6.7 Clock Monitoring

- 6.8 Glitch Filters

- 6.9 Device Memory Map

- 6.10 Flash Memory

- 6.11 Tightly Coupled RAM (TCRAM) Interface Module

- 6.12 Parity Protection for Peripheral RAMs

- 6.13 On-Chip SRAM Initialization and Testing

- 6.14 External Memory Interface (EMIF)

- 6.15 Vectored Interrupt Manager

- 6.16 DMA Controller

- 6.17 Real Time Interrupt Module

- 6.18 Error Signaling Module

- 6.19 Reset / Abort / Error Sources

- 6.20 Digital Windowed Watchdog

- 6.21

Debug Subsystem

- 6.21.1 Block Diagram

- 6.21.2 Debug Components Memory Map

- 6.21.3 JTAG Identification Code

- 6.21.4 Debug ROM

- 6.21.5 JTAG Scan Interface Timings

- 6.21.6 Advanced JTAG Security Module

- 6.21.7 Embedded Trace Macrocell (ETM-R4)

- 6.21.8 RAM Trace Port (RTP)

- 6.21.9 Data Modification Module (DMM)

- 6.21.10 Boundary Scan Chain

-

7Peripheral Information and Electrical Specifications

- 7.1 Peripheral Legend

- 7.2 Multibuffered 12-Bit Analog-to-Digital Converter

- 7.3 General-Purpose Input/Output

- 7.4 Enhanced Next Generation High-End Timer (N2HET)

- 7.5 Controller Area Network (DCAN)

- 7.6 Local Interconnect Network Interface (LIN)

- 7.7 Serial Communication Interface (SCI)

- 7.8 Inter-Integrated Circuit (I2C)

- 7.9 Multibuffered / Standard Serial Peripheral Interface

- 7.10 Ethernet Media Access Controller

- 8Device and Documentation Support

- 9Mechanical Packaging and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- ZWT|337

Thermal pad, mechanical data (Package|Pins)

Orderable Information

8 Device and Documentation Support

8.1 Device Support

8.1.1 Development Support

Texas Instruments (TI) offers an extensive line of development tools for the TMS570LSxRM48Lx family of MCUs, including tools to evaluate the performance of the processors, generate code, develop algorithm implementations, and fully integrate and debug software and hardware modules.

The following products support development:

Software Development Tools

- Code Composer Studio™ (CCS) Integrated Development Environment (IDE)–

- C/C++ Compiler

- Code generation tools

- Assembler/Linker

- FPU Optimized Libraries

- Application algorithms

- Sample applications code

Hardware Development Tools

- Development and evaluation boards

- JTAG-based emulators - XDS510™ class, XDS560™ emulator, XDS100v2, XDS110, XDS200

- Flash programming tools

For a complete listing of development-support tools, visit the Texas Instruments website at www.ti.com.

8.1.2 Device Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all MCU devices. Each MCU commercial family member has one of three prefixes: X, P, or NULL [blank] (for example, xRM48L952). These prefixes represent evolutionary stages of product development from engineering prototypes (X) through fully qualified production devices (NULL[blank]).

Device development evolutionary flow:

-

X Experimental device that is not necessarily representative of the final device's electrical specifications.

-

P Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification.

-

NULL Fully-qualified production device.

X and P devices are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Production devices have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

Figure 8-1 shows the numbering and symbol nomenclature for the RM48Lx40.

For additional information on the device nomenclature markings, see the device-specific silicon errata document listed in Section 8.2.1, Related Documentation from Texas Instruments.

8.2 Documentation Support

8.2.1 Related Documentation from Texas Instruments

The following documents describe the RM48Lx40 microcontroller.

-

SPNU503RM48x 16/32-Bit RISC Flash Microcontroller Technical Reference Manualdetails the integration, the environment, the functional description, and the programming models for each peripheral and subsystem in the device.

-

SPNZ196RM48x Microcontroller, Silicon Revision C, Silicon Errata describes the usage notes and known exceptions to the functional specifications for the device silicon revision C.

-

SPNZ223RM48x Microcontroller, Silicon Revision D, Silicon Errata describes the usage notes and known exceptions to the functional specifications for the device silicon revision D.

-

SPNA207Calculating Equivalent Power-on-Hours for Hercules™ Safety MCUs details how to use the spreadsheet to calculate the aging effect of temperature on Texas Instruments Hercules Safety MCUs.

8.3 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

Table 8-1 Related Links

| PARTS | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL DOCUMENTS | TOOLS & SOFTWARE | SUPPORT & COMMUNITY |

|---|---|---|---|---|---|

| RM48L940 | Click here | Click here | Click here | Click here | Click here |

| RM48L740 | Click here | Click here | Click here | Click here | Click here |

| RM48L540 | Click here | Click here | Click here | Click here | Click here |

8.4 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

-

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

-

TI Embedded Processors Wiki Texas Instruments Embedded Processors Wiki. Established to help developers get started with Embedded Processors from Texas Instruments and to foster innovation and growth of general knowledge about the hardware and software surrounding these devices.

8.5 Trademarks

Code Composer Studio, XDS510, XDS560, E2E are trademarks of Texas Instruments.

ARM, Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and.

CoreSight is a trademark of ARM Limited.

All other trademarks are the property of their respective owners.

8.6 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

8.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

8.8 Device Identification Code Register

The device identification code register identifies several aspects of the device including the silicon version. The details of the device identification code register are shown in Table 8-2. The device identification code register value for this device is:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| CP-15 | UNIQUE ID | TECH | |||||||||||||

| R-1 | R-00000000010101 | R-0 | |||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TECH | I/O VOLTAGE | PERIPH PARITY | FLASH ECC | RAM ECC | VERSION | 1 | 0 | 1 | |||||||

| R-101 | R-0 | R-1 | R-10 | R-1 | R-00000 | R-1 | R-0 | R-1 | |||||||

| LEGEND: R/W = Read/Write; R = Read only; -n = value after reset |

Table 8-2 Device ID Bit Allocation Register Field Descriptions

| BIT | FIELD | VALUE | DESCRIPTION |

|---|---|---|---|

| 31 | CP15 | Indicates the presence of coprocessor 15 | |

| 1 | CP15 present | ||

| 30-17 | UNIQUE ID | 10101 |

Silicon version (revision) bits. This bit field holds a unique number for a dedicated device configuration (die). |

| 16-13 | TECH | Process technology on which the device is manufactured. | |

| 0101 | F021 | ||

| 12 | I/O VOLTAGE | I/O voltage of the device. | |

| 0 | I/O are 3.3 V | ||

| 11 | PERIPHERAL PARITY | Peripheral Parity | |

| 1 | Parity on peripheral memories | ||

| 10-9 | FLASH ECC | Flash ECC | |

| 10 | Program memory with ECC | ||

| 8 | RAM ECC | Indicates if RAM memory ECC is present. | |

| 1 | ECC implemented | ||

| 7-3 | REVISION | Revision of the device. | |

| 2-0 | 101 | The platform family ID is always 0b101 |

8.9 Die Identification Registers

The two die ID registers at addresses 0xFFFFFF7C and 0xFFFFFF80 form a 64-bit die ID with the information as shown in Table 8-3.

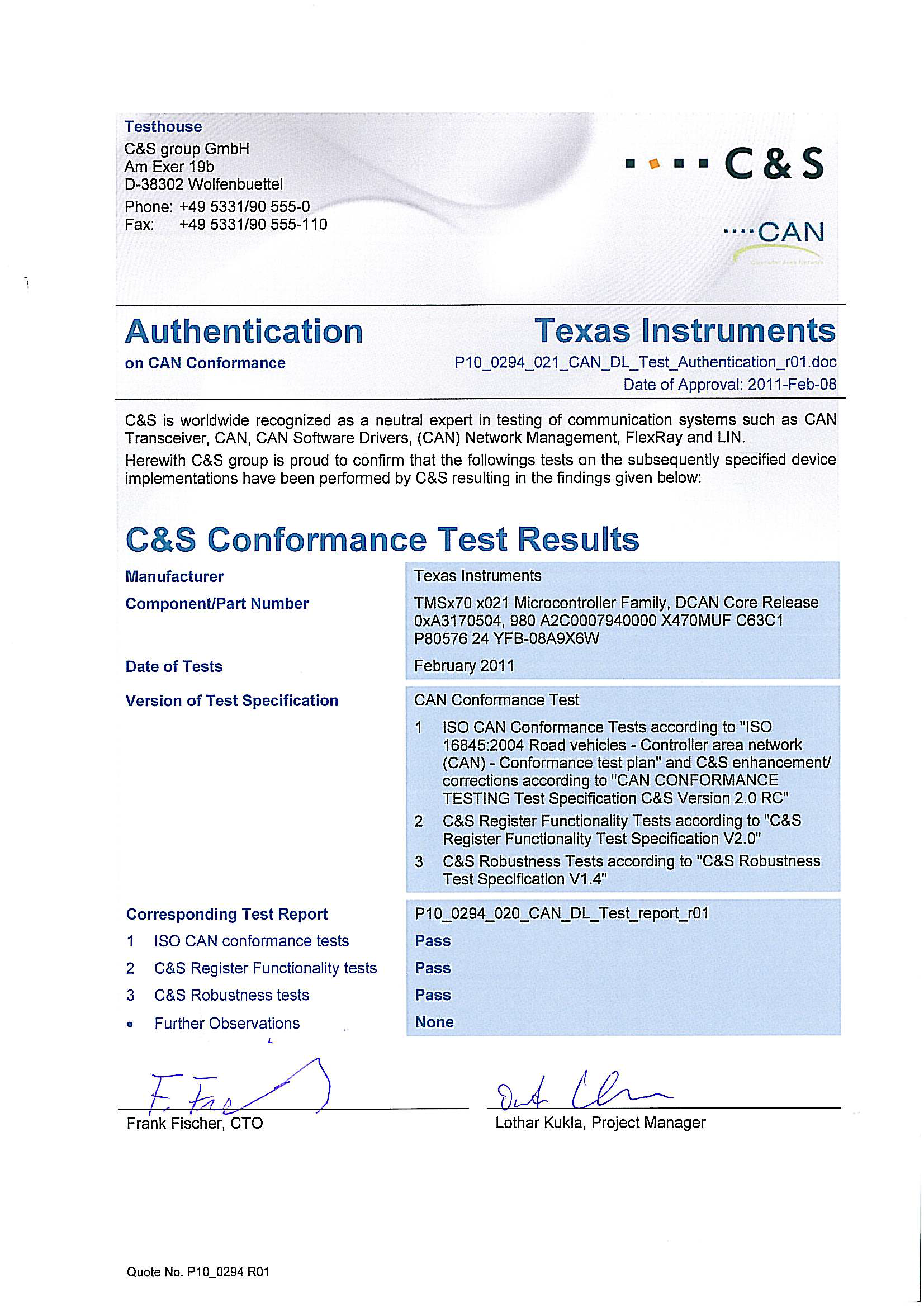

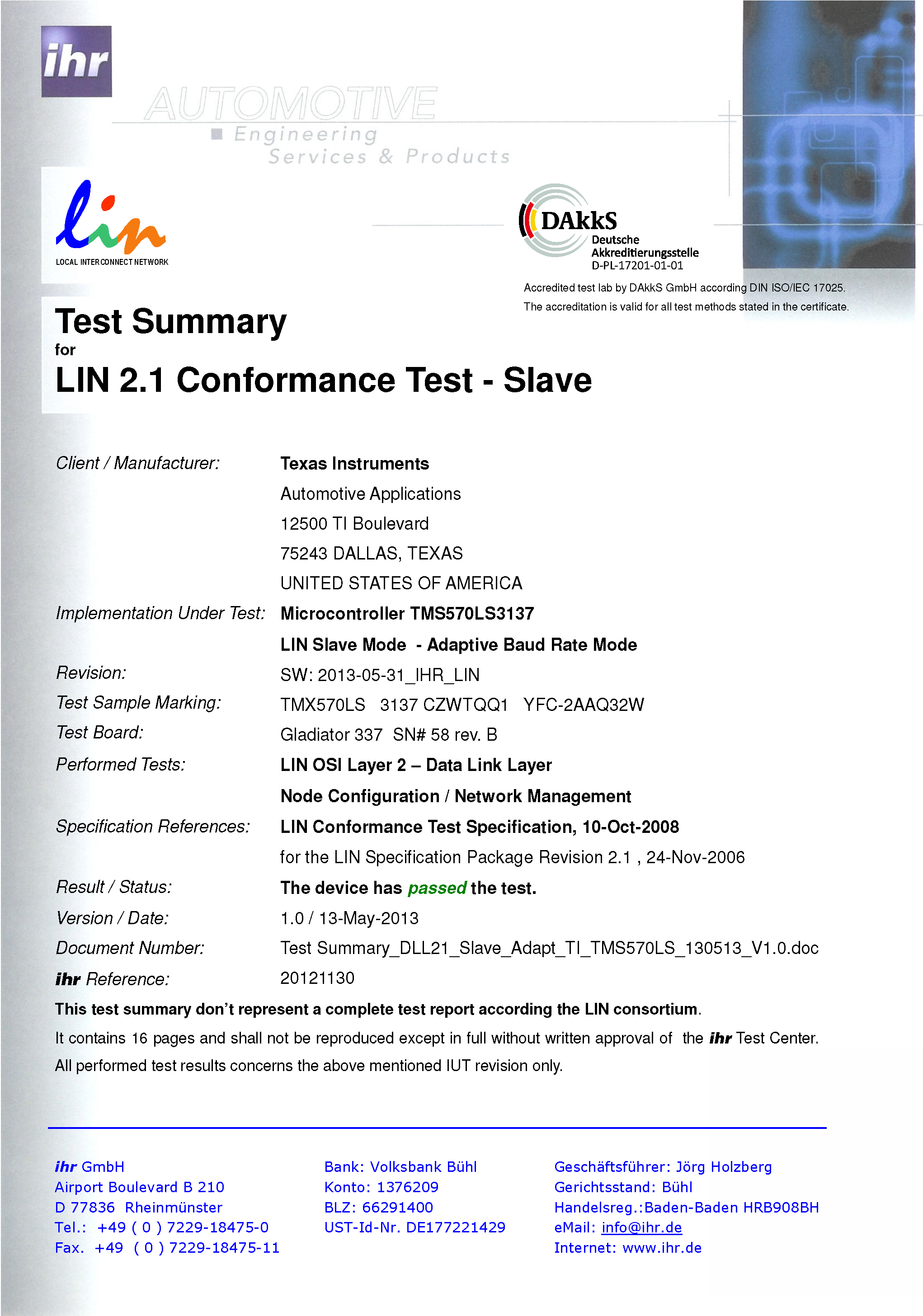

8.10 Module Certifications

The following communications modules have received certification of adherence to a standard.

8.10.1 DCAN Certification

Figure 8-3 DCAN Certification

Figure 8-3 DCAN Certification

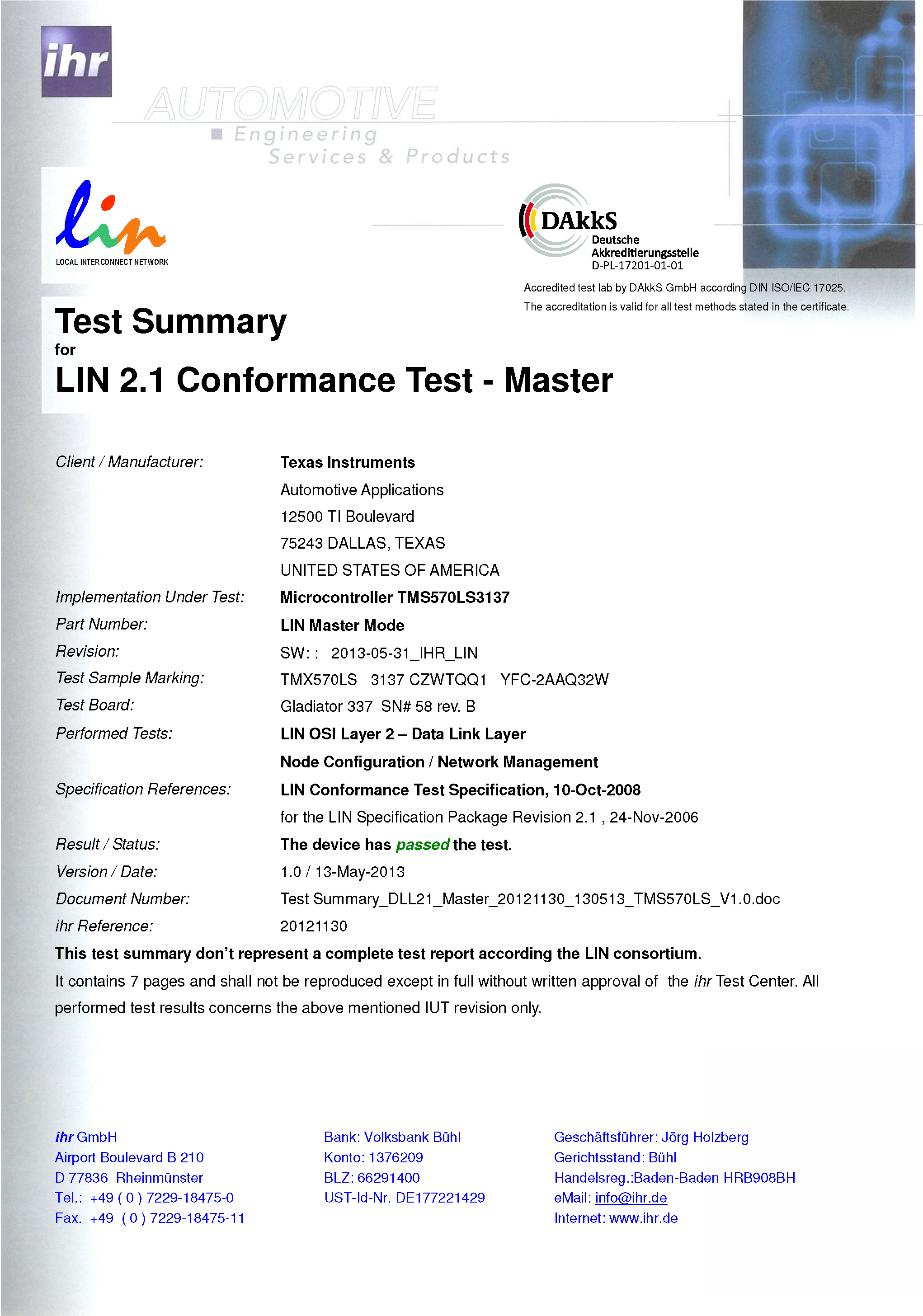

8.10.2 LIN Certification

8.10.2.1 LIN Master Mode

Figure 8-4 LIN Certification - Master Mode

Figure 8-4 LIN Certification - Master Mode

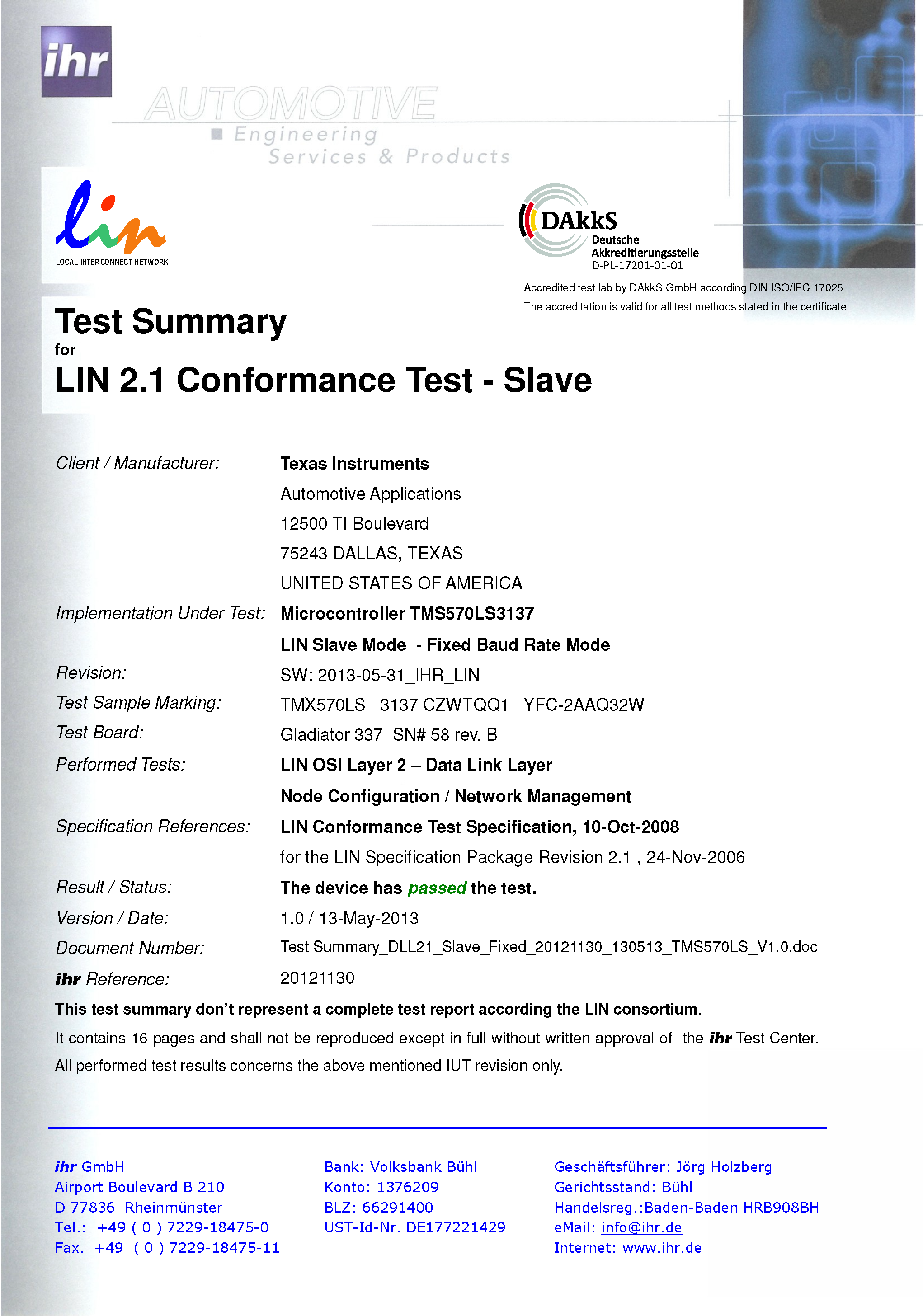

8.10.2.2 LIN Slave Mode - Fixed Baud Rate

Figure 8-5 LIN Certification - Slave Mode - Fixed Baud Rate

Figure 8-5 LIN Certification - Slave Mode - Fixed Baud Rate

8.10.2.3 LIN Slave Mode - Adaptive Baud Rate

Figure 8-6 LIN Certification - Slave Mode - Adaptive Baud Rate

Figure 8-6 LIN Certification - Slave Mode - Adaptive Baud Rate