SLVSCB6E November 2013 – December 2017 TPS56520 , TPS56720 , TPS56920 , TPS56C20

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (Continued)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Applications and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- PWP|20

Thermal pad, mechanical data (Package|Pins)

- PWP|20

Orderable Information

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

(1) These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions.

(2) All voltages are with respect to IC GND terminal.

7.2 ESD Ratings

| VALUE | UNIT | ||||

|---|---|---|---|---|---|

| Electrostatic discharge(1) | Human Body Model (HBM)(2) | ±2000 | V | ||

| Charged Device Model (CDM)(3) | ±500 | ||||

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

(2) Level listed above is the passing level per ANSI/ESDA/JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(3) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| VIN | Operating input voltage | 4.5 | 17 | V | ||

| VOUT | Output voltage | 0.6 | 1.87 | V | ||

| IOUT | Output current | TPS56520 | 0 | 5 | A | |

| TPS56720 | 0 | 7 | ||||

| TPS56920 | 0 | 9 | ||||

| TPS56C20 | 0 | 12 | ||||

| TJ | Operating junction temperature range | –40 | 125 | °C | ||

7.4 Thermal Information

| THERMAL METRIC(1) | TPS56520/720/920 | TPS56C20 | UNIT | |

|---|---|---|---|---|

| PWP (20) | PWP (24) | |||

| θJA | Junction-to-ambient thermal resistance | 36.8 | 32.8 | °C/W |

| θJCtop | Junction-to-case (top) thermal resistance | 22.5 | 16 | |

| θJB | Junction-to-board thermal resistance | 19.5 | 14.2 | |

| ψJT | Junction-to-top characterization parameter | 0.6 | 0.4 | |

| ψJB | Junction-to-board characterization parameter | 19.2 | 14 | |

| θJCbot | Junction-to-case (bottom) thermal resistance | 1.4 | 0.8 | |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

7.5 Electrical Characteristics

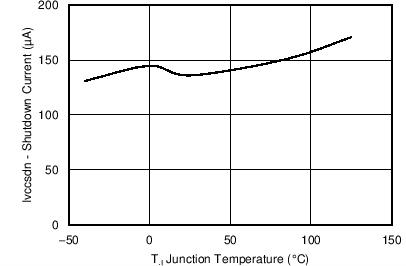

TJ = –40°C to 125°C, VIN=4.5V to 17V, PVIN=4.5V to 17V (Unless otherwise noted)| PARAMETER | CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| SUPPLY VOLTAGE | ||||||

| VIN | Operating input voltage | VIN, PVIN | 4.5 | 17 | V | |

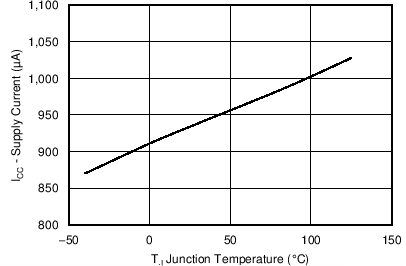

| IIN | VIN supply current | 25°C, EN=5V, VFB=0.8V (non switching), VIN=12V | 920 | 1150 | µA | |

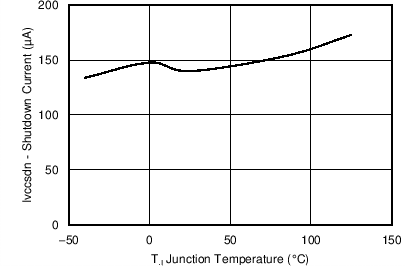

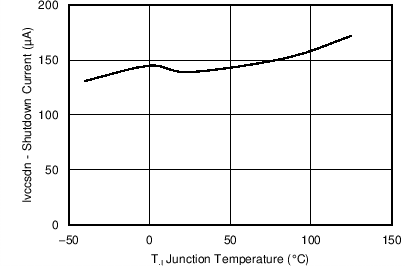

| IVINSDN | VIN shutdown current | 25°C, EN=0V, VIN=12V | 140 | 200 | µA | |

| FEEDBACK VOLTAGE | ||||||

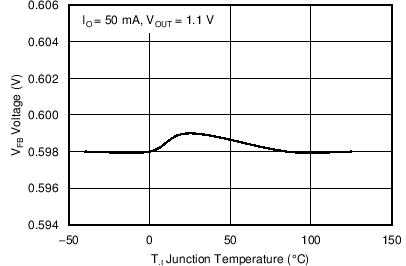

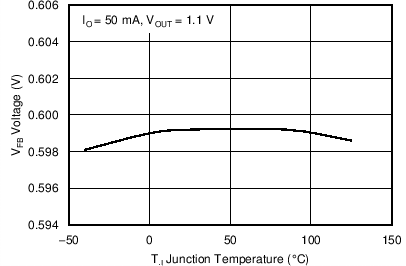

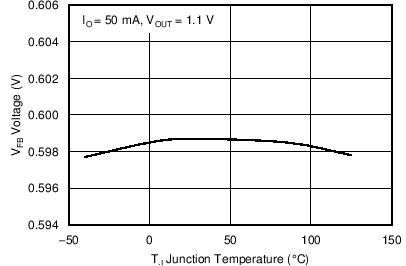

| VVFB | VFB voltage | 25°C, external regulation mode, PVIN=12V, VOUT=1.1V, IOUT=50mA, pulse skipping | 0.594 | 0.6 | 0.606 | V |

| 25°C, external regulation mode, VOUT=1.1V, continuous current mode | 0.594 | 0.6 | 0.606 | V | ||

| External regulation mode, VOUT=1.1V, continuous current mode | 0.591 | 0.6 | 0.609 | V | ||

| VOUT VOLTAGE (INTERNAL VID CONTROL) | ||||||

| VVOUT | VOUT voltage | 25°C, relative to target VOUT, PVIN=12V, VOUT=0.6V~1.87V, LOUT=1.5µH | –1% | 0% | 1% | Target VOUT |

| Relative to target VOUT, PVIN=12V, LOUT=1.5µH | –1.5% | 0% | 1.5% | |||

| Relative to target VOUT, LOUT=1.5µH | –2% | 0% | 2% | |||

| VREG5 OUTPUT | ||||||

| VVREG5 | VREG5 Output Voltage | 25°C , 6V< VIN <17V, IVREG5 = 5mA, VFB=1V | 5.2 | 5.5 | 5.7 | V |

| MOSFET | ||||||

| rDS(on)H | High side switch resistance TPS56520 | VBST-SW=5.5V | 44 | mΩ | ||

| rDS(on)L | Low side switch resistance TPS56520 | VIN=12V | 32 | mΩ | ||

| rDS(on)H | High side switch resistance TPS56720 | VBST-SW=5.5V | 30 | mΩ | ||

| rDS(on)L | Low side switch resistance TPS56720 | VIN=12V | 24 | mΩ | ||

| rDS(on)H | High side switch resistance TPS56920 | VBST-SW=5.5V | 26 | mΩ | ||

| rDS(on)L | Low side switch resistance TPS56920 | VIN=12V | 19 | mΩ | ||

| rDS(on)H | High side switch resistance TPS56C20 | VBST-SW=5.5V | 13 | mΩ | ||

| rDS(on)L | Low side switch resistanceTPS56C20 | VIN=12V | 9 | mΩ | ||

| POWER GOOD | ||||||

| VPGOODTH | PGOOD threshold | VOUT or VFB falling (fault) VO=1.1V | 80% | |||

| VOUT or VFB rising (good) VO=1.1V | 85% | |||||

| VOUT or VFB rising (fault) VO=1.1V | 115% | |||||

| VOUT or VFB falling (good) VO=1.1V | 110% | |||||

| IPGOODDLY | PGOOD sink current | VPGOOD=0.5V | 3.15 | 5.2 | mA | |

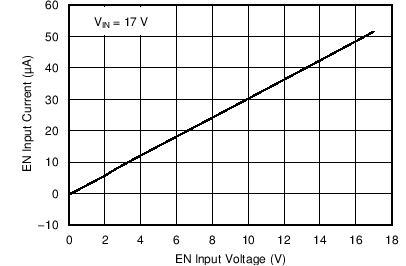

| LOGIC THRESHOLD | ||||||

| VENH | EN H-level threshold voltage | 1.85 | V | |||

| VENL | EN L-level threshold voltage | 0.6 | V | |||

| CURRENT LIMIT(1) | ||||||

| IOCL | Current Limit TPS56520 | LOUT= 1.5µH | 5.6 | 9 | A | |

| Current Limit TPS56720 | LOUT= 1.5µH | 7.8 | 12 | A | ||

| Current Limit TPS56920 | LOUT= 1.5µH | 10 | 15 | A | ||

| Current Limit TPS56C20 | LOUT= 1.5µH | 13.2 | 20 | A | ||

| IOCLR | Reverse Current Limit TPS56520 | LOUT= 1.5µH | 1.25 | 5.3 | A | |

| Reverse Current Limit TPS56720 | LOUT= 1.5µH | 1.75 | 6.5 | A | ||

| Reverse Current Limit TPS56920 | LOUT= 1.5µH | 2.25 | 6.2 | A | ||

| Reverse Current Limit TPS56C20 | LOUT= 1.5µH | 3 | 8.2 | A | ||

| OUTPUT UNDERVOLTAGE PROTECTION (UVP) | ||||||

| VOVP | Output OVP trip threshold | OVP detect (L>H) | 125% | VOUT | ||

| VUVP | Output UVP trip threshold | UVP detect (H>L) | 60% | VOUT | ||

| THERMAL SHUTDOWN | ||||||

| TSDN | Thermal shutdown Threshold | Shutdown temperature(1) | 160 | °C | ||

| Hysteresis(1) | 23 | °C | ||||

| Pre-thermal warning threshold | 130 | °C | ||||

| UVLO | ||||||

| UVLO | UVLO Threshold | Wake up to VREG5 voltage | 3.45 | 3.9 | 4.2 | V |

| Hysteresis VREG5 voltage | 0.45 | 0.56 | 0.61 | V | ||

(1) Ensured by design. Not production tested.

7.6 Timing Requirements

| MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|

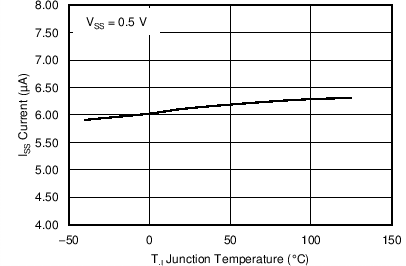

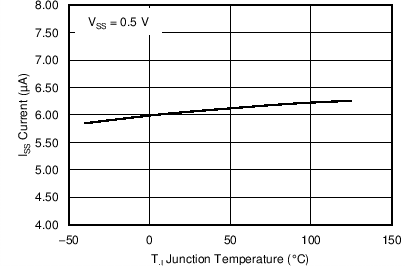

| SOFT START | ||||||

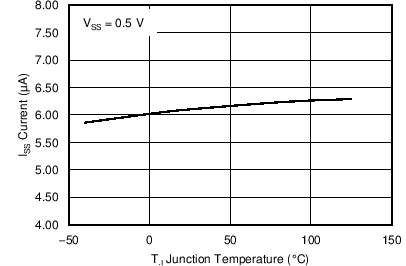

| Issc | SS charge current | VSS=0.5V , 25 °C | –6.4 | –6 | –5.6 | µA |

| IssD | SS discharge current | VSS=0.5V | 0.14 | 0.2 | 0.26 | mA |

| SERIAL INTERFACE(1) (2) (3) | ||||||

| VIL | LOW level input voltage | 0.6 | V | |||

| VIH | HIGH level input voltage | 1.8 | V | |||

| Vhys | Hysteresis of Schmitt trigger inputs | 0.11 | V | |||

| VOL | LOW level output voltage (Open drain, 3mA sink current) | 0.4 | V | |||

| tSP | Pulse width of spikes suppressed by input filter | 32 | ns | |||

| fscl | SCL clock frequency | 400 | kHz | |||

| tHD;STA | Hold time (repeated) START condition. | 0.6 | us | |||

| tLOW | LOW period of SCL clock | 1.3 | us | |||

| tHIGH | HIGH period of SCL clock | 0.6 | us | |||

| tSU;STA | Set-up time for a repeated START condition | 0.6 | us | |||

| tHD;DAT | Data Hold time | 50 | 900 | ns | ||

| tSU;DAT | Data set-up time | 100 | ns | |||

| tr | Rise time (SDA or SCL) | 20+0.1Cb(4) | 300 | ns | ||

| tf | Fall time (SDA or SCL) | 20+0.1Cb(4) | 300 | ns | ||

| tSU;STO | Set-up time for STOP condition | 0.6 | us | |||

| tBUF | Bus free time between STOP and START condition | 1.3 | us | |||

| Cb | Capacitive load for each bus line | 400 | pF | |||

(1) Ensured by design. Not production tested.

(2) Refer to Figure 1 below for I2C Timing Definitions

(3) Cb = capacitance of bus line in pF

Figure 1. I2C Timing Definitions (reproduced from Phillips I2C spec Version 1.1)

Figure 1. I2C Timing Definitions (reproduced from Phillips I2C spec Version 1.1)

7.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| ON-TIME TIMER CONTROL | ||||||

| TON | SW On Time | SW=12V, VOUT=1.1V | 180 | ns | ||

| TOFF(1) | SW Minimum off time | 25°C, VFB= 0.5V | 285 | ns | ||

(1) Ensured by design. Not production tested.

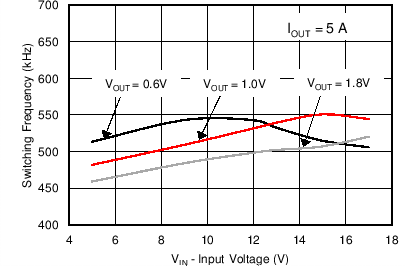

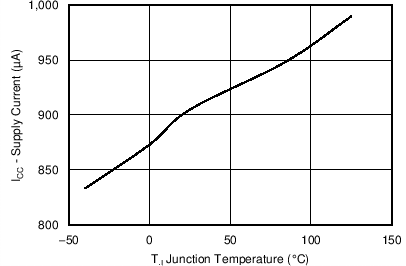

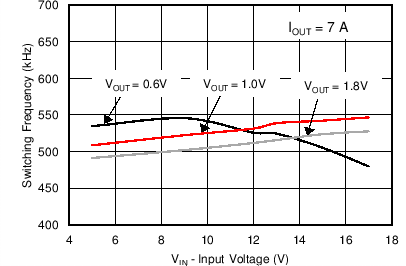

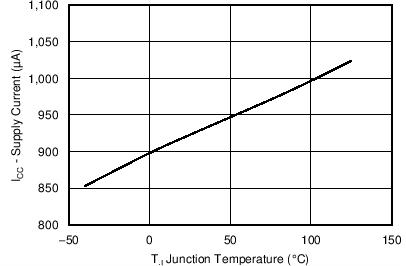

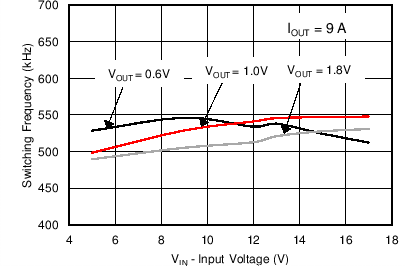

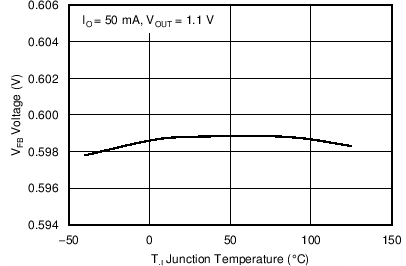

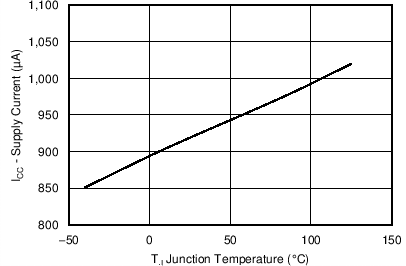

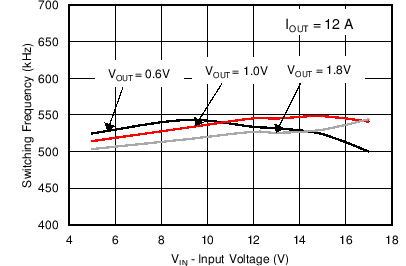

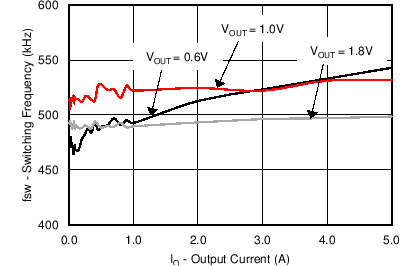

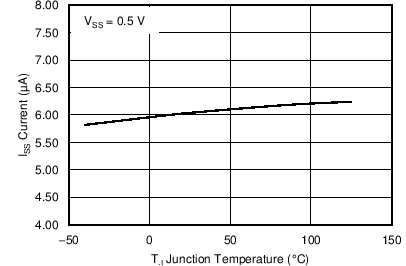

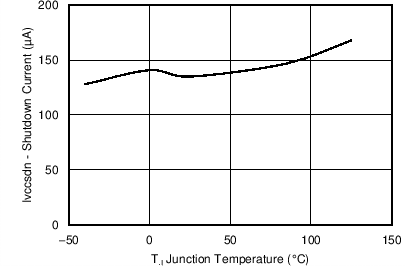

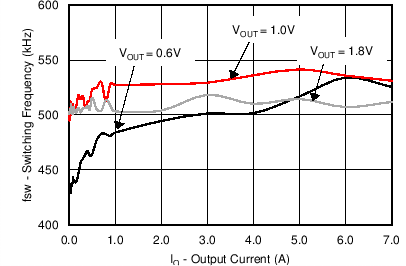

7.8 Typical Characteristics

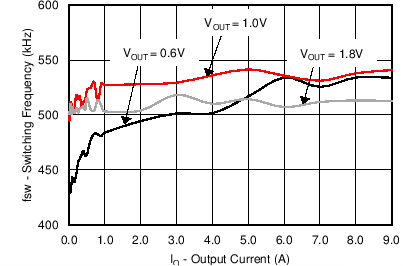

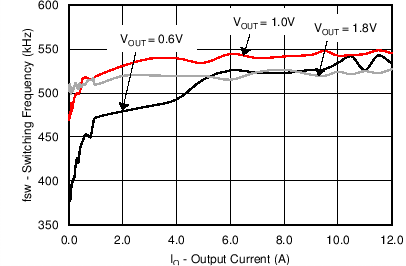

VIN = 12 V, VOUT = 1.0 V, Ta = 25 °C, unless otherwise specified.

Eco-mode™ = OFF

Eco-mode™ = OFF

Eco-mode™ = OFF

Eco-mode™ = OFF