SLVSAT8E November 2011 – May 2017 TPS62170 , TPS62171 , TPS62172 , TPS62173

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Voltage Options

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Application

- 9.2.1 Design Requirements

- 9.2.2 Detailed Design Procedure

- 9.2.3 Application Curves

- 9.3 System Examples

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DSG|8

Thermal pad, mechanical data (Package|Pins)

- DSG|8

Orderable Information

7 Specifications

7.1 Absolute Maximum Ratings(1)

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Pin voltage range(2) | VIN | –0.3 | 20 | V |

| EN, SW (DC) | –0.3 | VIN+ 0.3 | V | |

| SW (AC), less than 10ns(3) | –2 | 24.5 | ||

| FB, PG, VOS | –0.3 | 7 | V | |

| Power good sink current | PG | 10 | mA | |

| Operating junction temperature, TJ | –40 | 150 | °C | |

| Storage temperature, Tstg | –65 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to network ground terminal.

(3) While switching.

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

| MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|

| Supply Voltage, VIN | 3 | 17 | V | |

| Output Voltage, VOUT | 0.9 | 6 | V | |

| Operating junction temperature, TJ | –40 | 125 | °C |

7.4 Thermal Information

| THERMAL METRIC(1) | TPS6217x | UNIT | |

|---|---|---|---|

| DSG (WSON) | |||

| 8 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 61.8 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 61.3 | °C/W |

| RθJB | Junction-to-board thermal resistance | 15.5 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.4 | °C/W |

| ψJB | Junction-to-board characterization parameter | 15.4 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 8.6 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

7.5 Electrical Characteristics

Over junction temperature range (TJ = –40°C to +125°C), typical values at VIN = 12 V and TJ = 25°C (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|---|---|

| SUPPLY | |||||||

| VIN | Input voltage range(1) | 3 | 17 | V | |||

| IQ | Operating quiescent current | EN = High, IOUT = 0 mA, device not switching | 17 | 30 | µA | ||

| TJ = -40°C to +85°C | 17 | 25 | |||||

| ISD | Shutdown current(2) | EN = Low | 1.5 | 25 | µA | ||

| TJ = -40°C to +85°C | 1.5 | 4 | |||||

| VUVLO | Undervoltage lockout threshold | Falling input voltage | 2.6 | 2.7 | 2.82 | V | |

| Hysteresis | 180 | mV | |||||

| TSD | Thermal shutdown temperature | rising temperature | 160 | °C | |||

| Thermal shutdown hysteresis | falling temperature | 20 | |||||

| CONTROL (EN, PG) | |||||||

| VEN_H | High level input threshold voltage (EN) | 0.9 | 0.6 | V | |||

| VEN_L | Low level input threshold voltage (EN) | 0.56 | 0.3 | V | |||

| ILKG_EN | Input leakage current (EN) | EN = VIN or GND | 0.01 | 1 | µA | ||

| VTH_PG | Power good threshold voltage | Rising (%VOUT) | 92% | 95% | 98% | ||

| Falling (%VOUT) | 87% | 90% | 93% | ||||

| VOL_PG | Power good output low voltage | IPG = –2 mA | 0.07 | 0.3 | V | ||

| ILKG_PG | Input leakage current (PG) | VPG = 1.8 V | 1 | 400 | nA | ||

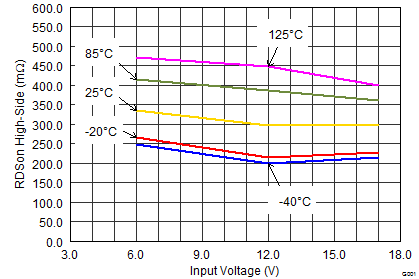

| POWER SWITCH | |||||||

| RDS(ON) | High-side MOSFET ON-resistance | VIN ≥ 6 V | 300 | 600 | mΩ | ||

| VIN= 3 V | 430 | ||||||

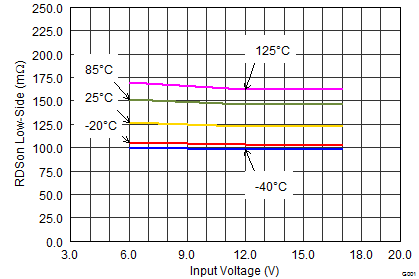

| Low-side MOSFET ON-resistance | VIN≥ 6 V | 120 | 200 | mΩ | |||

| VIN = 3 V | 165 | ||||||

| ILIMF | High-side MOSFET forward current limit(3) | VIN = 12 V, TJ= 25°C | 0.85 | 1.05 | 1.35 | A | |

| OUTPUT | |||||||

| VREF | Internal reference voltage(4) | 0.8 | V | ||||

| ILKG_FB | Pin leakage current (FB) | TPS62170, VFB= 1.2 V | 5 | 400 | nA | ||

| VOUT | Output voltage range (TPS62170) | VIN ≥ VOUT | 0.9 | 6.0 | V | ||

| Initial output voltage accuracy(5) | PWM mode operation, VIN ≥ VOUT + 1 V | –3% | 3% | ||||

| Power save mode operation, COUT= 22 µF | -3.5% | 4% | |||||

| DC output voltage load regulation | VIN = 12 V, VOUT = 3.3 V, PWM mode operation | 0.05 | %/A | ||||

| DC output voltage line regulation | 3 V ≤ VIN ≤ 17 V, VOUT = 3.3 V, IOUT = 0.5 A, PWM mode operation | 0.02 | %/V | ||||

(1) The device is still functional down to under voltage lockout (see parameter VUVLO).

(2) Current into VIN pin.

(3) This is the static current limit. It can be temporarily higher in applications due to internal propagation delay (see Current Limit and Short Circuit Protection).

(4) This is the voltage regulated at the FB pin.

(5) This is the accuracy provided by the device itself (line and load regulation effects are not included). For fixed voltage versions, the (internal) resistive feedback divider is included.