SLUSDQ8D december 2019 – may 2023 TPS652353

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Boost Converter

- 7.3.2 Linear Regulator and Current Limit

- 7.3.3 Boost Converter Current Limit

- 7.3.4 Charge Pump

- 7.3.5 Slew Rate Control

- 7.3.6 Short Circuit Protection, Hiccup and Overtemperature Protection

- 7.3.7 Tone Generation

- 7.3.8 Tone Detection

- 7.3.9 Audio Noise Rejection

- 7.3.10 Disable and Enable

- 7.3.11 Component Selection

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6 Register Maps

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RUK|20

Thermal pad, mechanical data (Package|Pins)

- RUK|20

Orderable Information

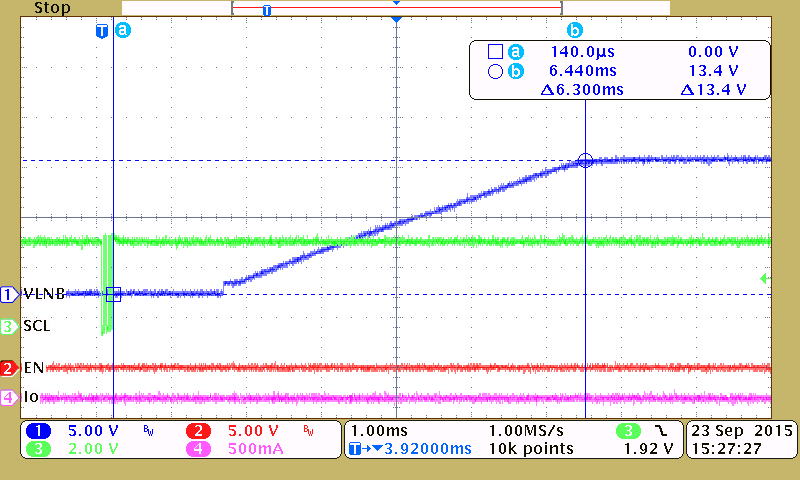

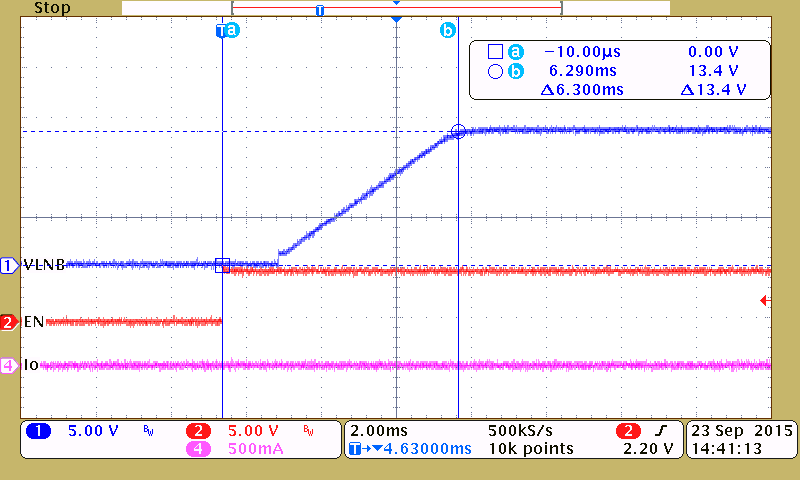

7.3.10 Disable and Enable

The TPS652353 device has a dedicated EN pin to disable and enable the LNB output. In a non-I2C application, when the EN pin is pulled high, the LNB output is enabled. When the EN pin is pulled low, the LNB output is disabled. In an I2C application, when the EN pin is either low or high, the I2C registers can be accessed, which allows users to change the default LNB output at system power-up. When the I2C_CON bit in the Control Register 1 is set to 1b, the LNB output enable or disable is controlled by the EN bit in the Control Register 2. By default, the I2C_CON bit of the control register is set to 0b, which makes the LNB output is controlled by the EN pin. Figure 7-3 and Figure 7-4 shows the detailed control behavior.

| V(EN) = 0 V | I2C_CON = 1b |

| I2C_CON = 0b |