SLVSCA0C October 2013 – September 2016 TPS7B4250-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DBV|5

Thermal pad, mechanical data (Package|Pins)

Orderable Information

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| Input voltage, unregulated input, VIN(2)(3) | –20 | 45 | V | ||

| Output voltage, regulated output, VOUT | –1 | 22 | V | ||

| Adjust input and enable input voltage, ADJ/EN(2)(3) | –0.3 | 22 | V | ||

| ADJ Voltage minus input voltage (ADJ–VIN), VIN > 0 V | 7 | V | |||

| Operating junction temperature, TJ | –40 | 150 | °C | ||

| Storage temperature, Tstg | –65 | 150 | °C | ||

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to ground, GND.

(3) Absolute maximum voltage.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002(1) | ±4000 | V |

| Charged-device model (CDM), per AEC Q100-011 | ±1000 | |||

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(2)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VIN | Unregulated input | 4 | 40 | V |

| VOUT | regulated output | 1.5 | 18 | V |

| ADJ/EN | Adjust input and enable input voltage | 1.5 | 18 | V |

| ADJ–VIN | ADJ voltage minus input voltage | 5 | V | |

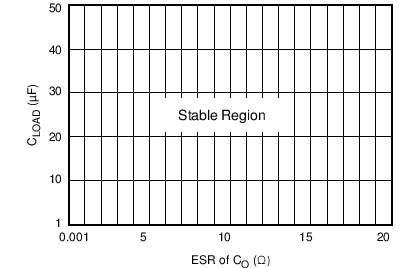

| COUT | Output capacitor requirements(1) | 1 | 50 | µF |

| ESRCOUT | Output ESR requirements | 0.001 | 20 | Ω |

| TJ | Operating junction temperature | –40 | 150 | °C |

(1) The minimum output capacitance requirement is applicable for a worst-case capacitance tolerance of 30%.

(2) Within the functional range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

6.4 Thermal Information

| THERMAL METRIC(2)(1) | TPS7B4250-Q1 | UNIT | |

|---|---|---|---|

| DBV (SOT-23) | |||

| 5 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 171.7 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 81.1 | °C/W |

| RθJB | Junction-to-board thermal resistance | 31.7 | °C/W |

| ψJT | Junction-to-top characterization parameter | 4.5 | °C/W |

| ψJB | Junction-to-board characterization parameter | 31.2 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | N/A | °C/W |

(1) The thermal data is based on the JEDEC standard high K profile, JESD 51-7. Two-signal, two-plane, four-layer board with 2-oz. copper. The copper pad is soldered to the thermal land pattern. Also, correct attachment procedure must be incorporated.

(2) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

6.5 Electrical Characteristics

VI = 13.5 V, 18 V ≥ VADJ/EN ≥ 1.5 V, TJ = –40ºC to 150ºC unless otherwise stated| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

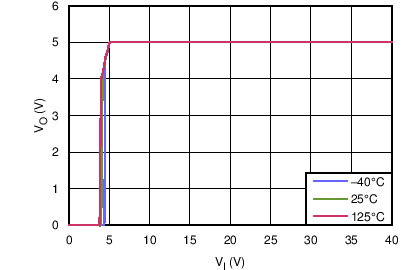

| VUVLO | VIN undervoltage detection | Ramp up VI until the output turns on, VADJ = 1.5 V | 3.65 | V | ||

| Ramp down VI until the output turns off, VADJ = 1.5 V | 3 | |||||

| ΔVO | Output-voltage tracking accuracy | IO = 100 µA to 1 mA, VI = 4 V to 40 V, 1.5 V < VADJ < VI – 0.3 V | –4 | 4 | mV | |

| IO = 1 mA to 50 mA, VI = 4 V to 40 V, 1.5 V < VADJ < VI – 1.5 V | –5 | 5 | ||||

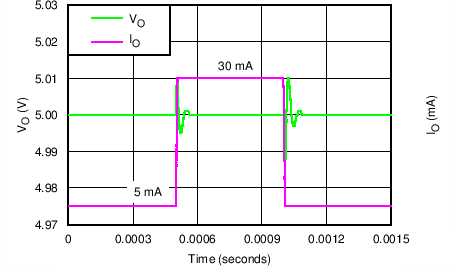

| ΔVO(ΔIL) | Load regulation steady-state | IO = 1 mA to 30 mA | 4 | mV | ||

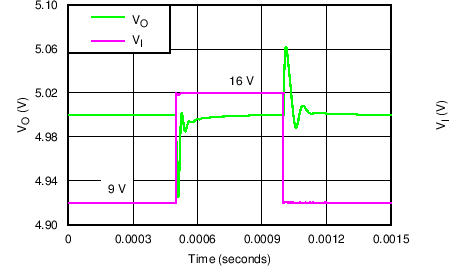

| ΔVO(ΔVI) | Line regulation steady-state | IO = 10 mA, VI = 6 V to 40 V | 3 | mV | ||

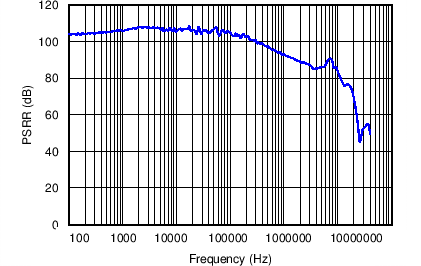

| PSRR | Power-supply ripple rejection | Frequency = 100 Hz, Vrip = 0.5 VPP, IO = 5 mA, CO = 2.2 µF | 60 | dB | ||

| Vdropout | Dropout voltage, Vdropout = VI – VQ | IO = 10 mA, VI ≥ 4 V(1) | 150 | 265 | mV | |

| IO = 50 mA, VI ≥ 4 V(1) | 550 | 1000 | ||||

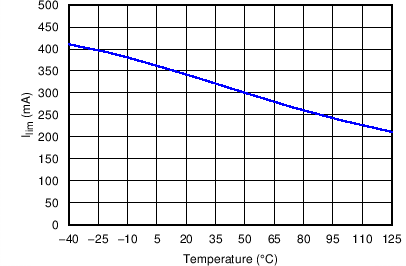

| IL | Output-current limitation | VO short to GND | 100 | 500 | mA | |

| IR | Reverse current at VIN | VI = 0 V, VO = 20 V, VADJ = 5 V | –5 | 0 | µA | |

| IRN1 | Reverse current at negative input voltage | VI = –20 V, VO = 0 V, VADJ = 5 V | –5 | 0 | µA | |

| IRN2 | VI = –20 V, VO = 20 V, VADJ = 5 V | –5 | 0 | |||

| TSD | Thermal shutdown temperature | TJ increasing because of power dissipation generated by the IC | 175 | °C | ||

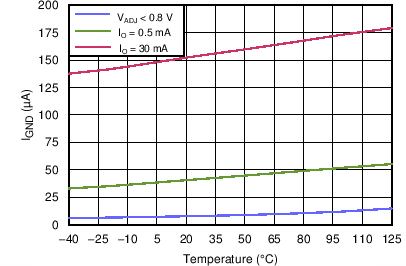

| IQ | Current consumption | VADJ < 0.8 V, TA ≤ 85°C(2) | 7.5 | 15 | µA | |

| VADJ < 0.8 V, TA ≤ 125°C | 20 | |||||

| IO = 0.5 mA, VADJ = 5 V | 40 | 90 | ||||

| IO = 30 mA, VADJ = 5 V | 150 | 350 | ||||

| IADJ | Adjust-input and enable-input current | VADJ = 5 V | 1 | µA | ||

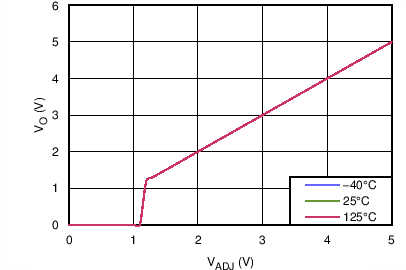

| VADJ,low | Adjust and enable low signal valid | VO = 0 V | 0.8 | V | ||

| VADJ,high | Adjust and enable high signal valid | |VO – VADJ| < 5 mV | 1.5 | 18 | V | |

(1) Measured when the output voltage VQ has dropped 10 mV from the typical value.

(2) Ensured by design.

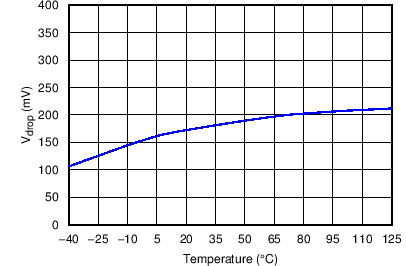

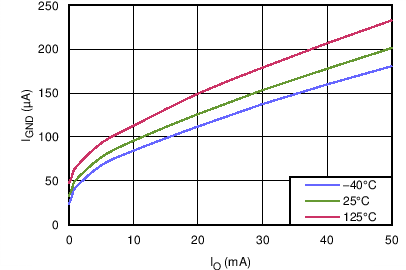

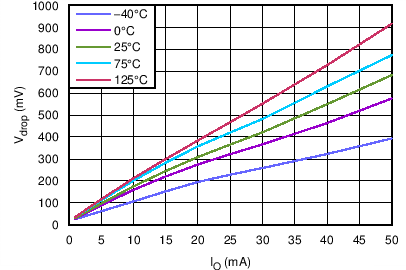

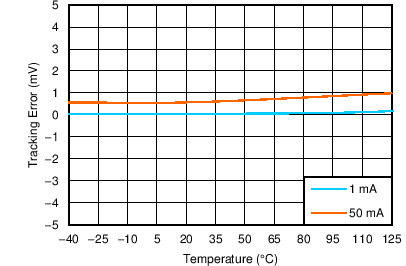

6.6 Typical Characteristics

| VI = VADJ = 4 V | IO = 10 mA | |

| VI = 13.5 V | VADJ = 5 V | |

| VI = VADJ = 4 V | ||

| VI = 13.5 V | VADJ = 5 V | IO = 1 mA, 50 mA |