JAJSDA9 June 2017 ADC081S101-MIL

PRODUCTION DATA.

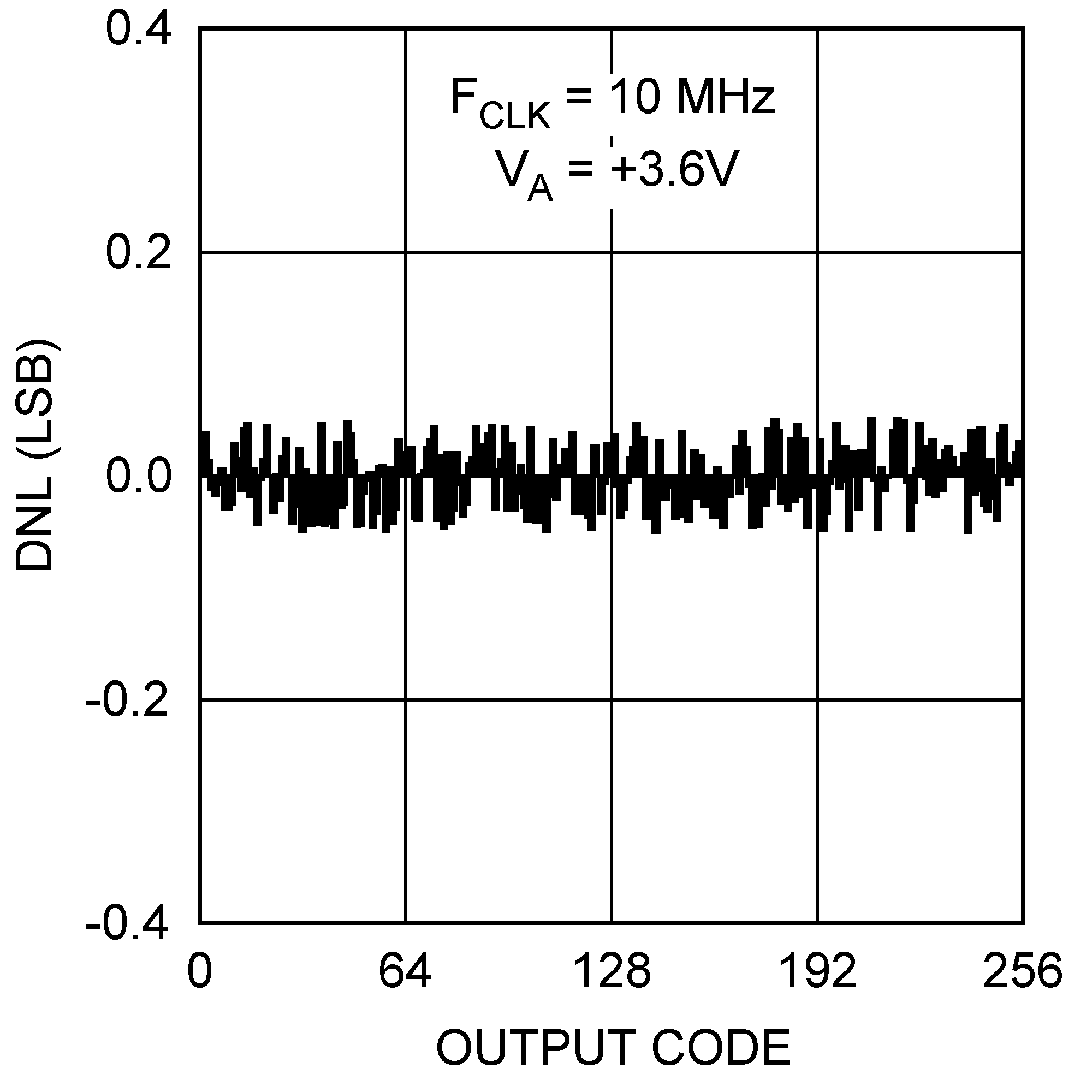

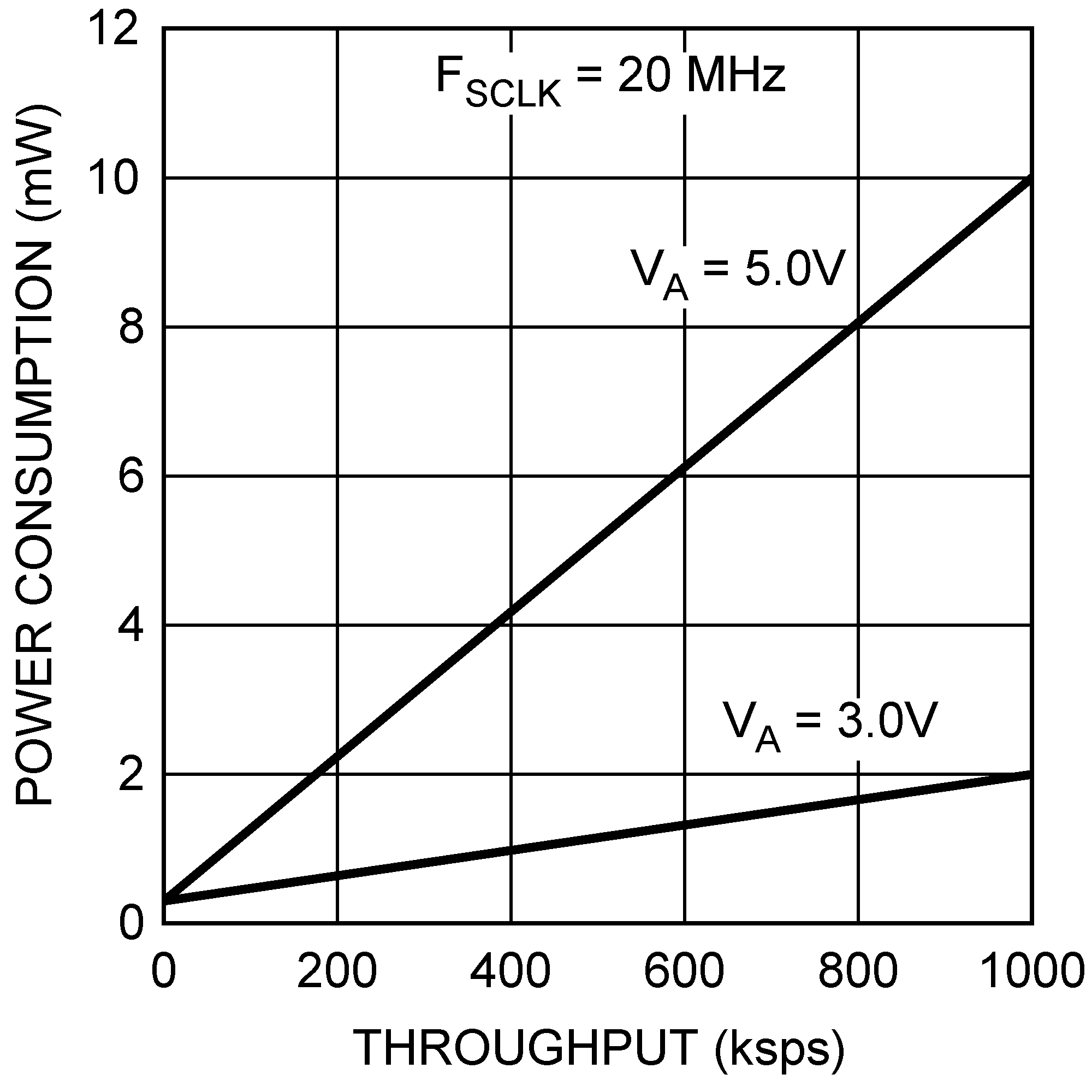

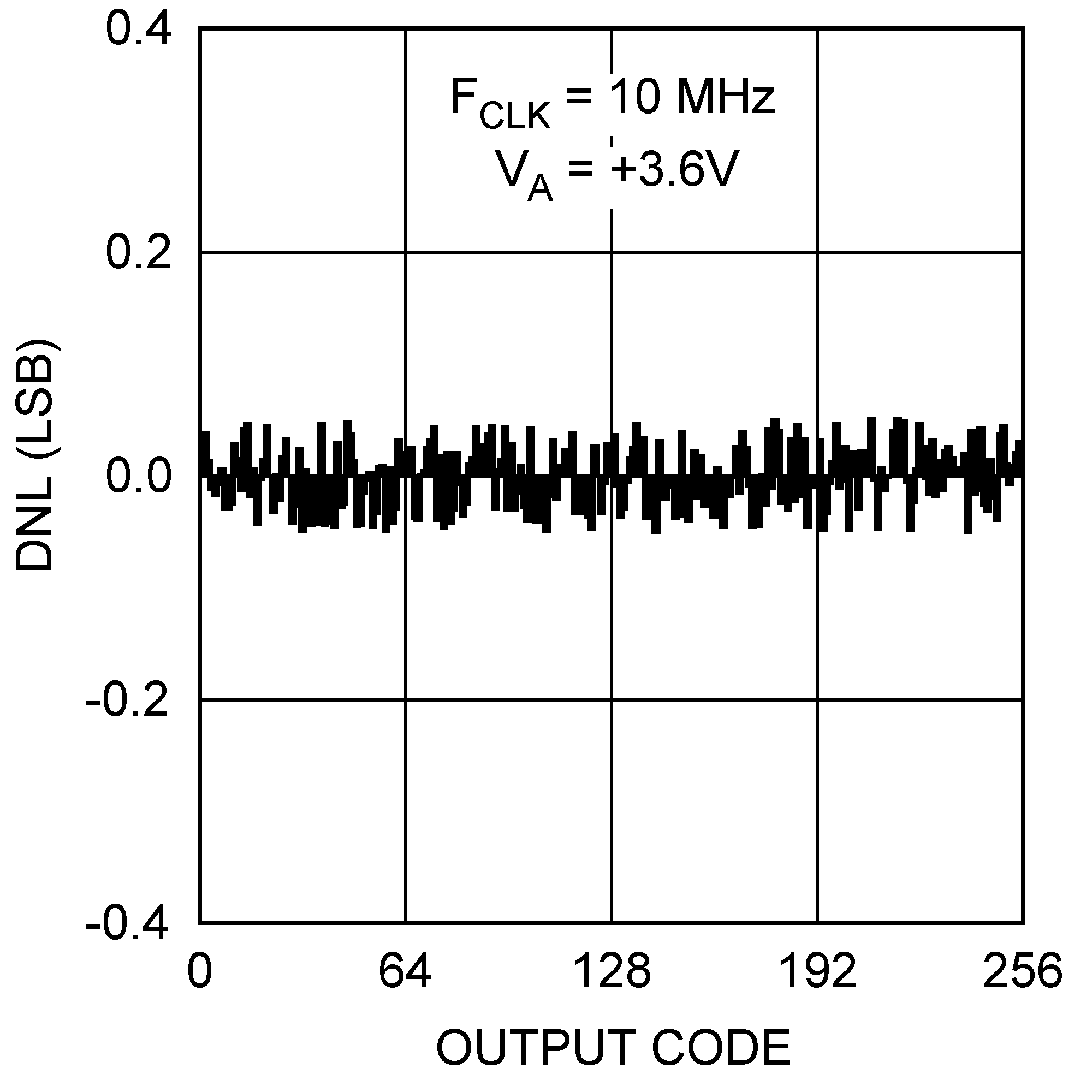

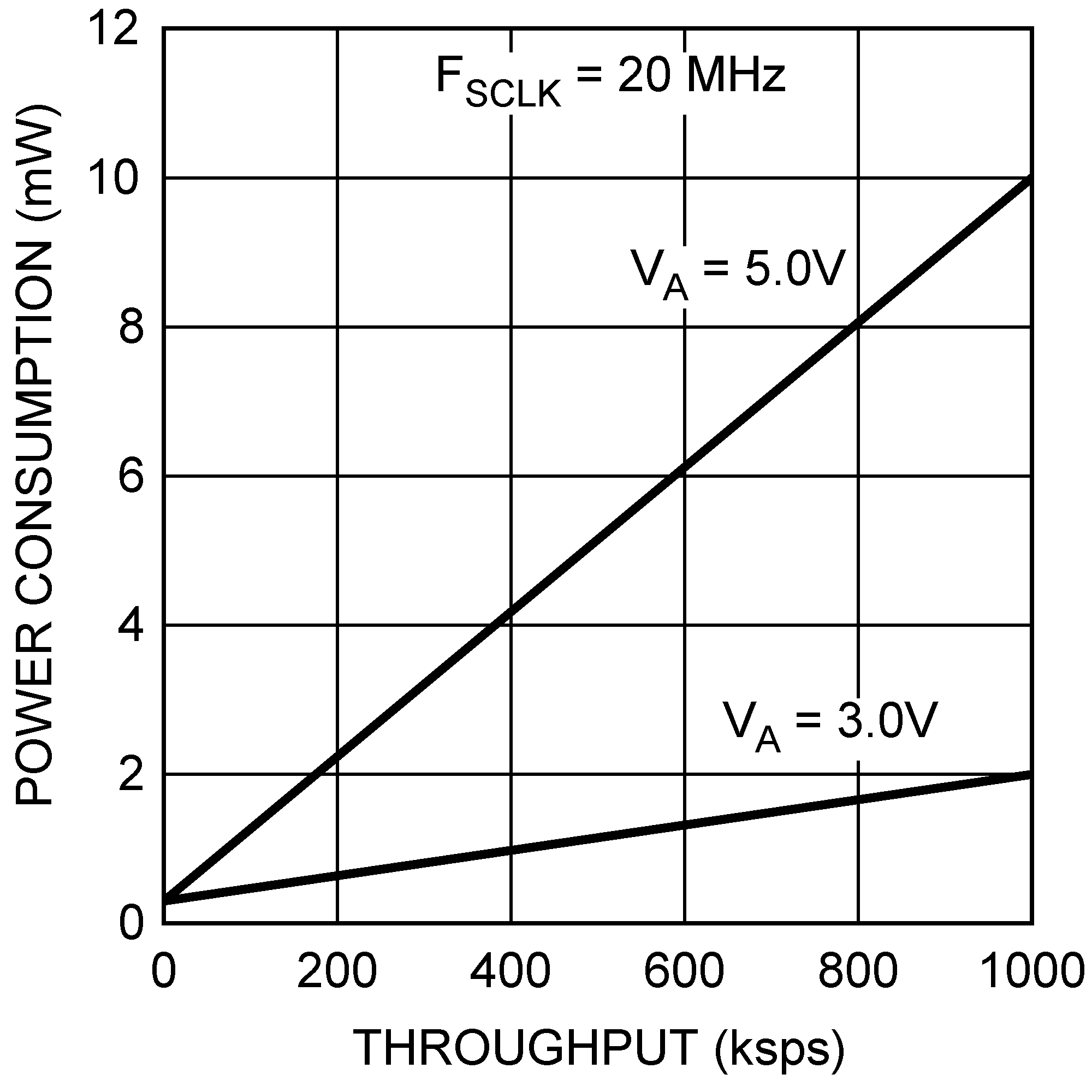

7 Typical Characteristics

TA = +25°C, fSAMPLE = 500 ksps to 1 Msps, fSCLK = 10 MHz to 20 MHz, fIN = 100 kHz unless otherwise stated.

JAJSDA9 June 2017 ADC081S101-MIL

PRODUCTION DATA.