SLUSBG7A December 2014 – November 2017

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (Continued)

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Device Power Up

- 8.3.2 Power Path Management

- 8.3.3 Battery Charging Management

- 8.3.4 Status Outputs (PG, STAT, and INT)

- 8.3.5 Protections

- 8.3.6 Serial Interface

- 8.4 Device Functional Modes

- 8.5

Register Map

- 8.5.1

I2C Registers

- 8.5.1.1 Input Source Control Register REG00 (reset = 00110000, or 30)

- 8.5.1.2 Power-On Configuration Register REG01 (reset = 00011011, or 1B)

- 8.5.1.3 Charge Current Control Register REG02 (reset = 01100000, or 60)

- 8.5.1.4 Pre-Charge/Termination Current Control Register REG03 (reset = 00010001, or 11)

- 8.5.1.5 Charge Voltage Control Register REG04 (reset = 10110010, or B2)

- 8.5.1.6 Charge Termination/Timer Control Register REG05 (reset = 10011010, or 9A)

- 8.5.1.7 IR Compensation / Thermal Regulation Control Register REG06 (reset = 00000011, or 03)

- 8.5.1.8 Misc Operation Control Register REG07 (reset = 01001011, or 4B)

- 8.5.1.9 System Status Register REG08

- 8.5.1.10 Fault Register REG09

- 8.5.1.11 Vender / Part / Revision Status Register REG0A (reset = 00101111, or 2F)

- 8.5.1

I2C Registers

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RGE|24

サーマルパッド・メカニカル・データ

- RGE|24

発注情報

7 Specifications

7.1 Absolute Maximum Ratings(1)

over operating free-air temperature range (unless otherwise noted)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Voltage range (with respect to GND) | VBUS | –2 | 22 | V |

| PMID | –0.3 | 22 | V | |

| STAT, PG | –0.3 | 20 | V | |

| BTST | –0.3 | 26 | V | |

| SW | –2 | 20 | V | |

| BAT, SYS (converter not switching) | –0.3 | 6 | V | |

| SDA, SCL, INT, OTG, ILIM, REGN, TS1, TS2, CE, PSEL | –0.3 | 7 | V | |

| BTST TO SW | –0.3 | –7 | V | |

| PGND to GND | –0.3 | –0.3 | V | |

| Output sink current | INT, STAT, PG | 6 | mA | |

| Junction temperature | –40°C | 150 | °C | |

| Storage temperature, Tstg | –65 | 150 | °C | |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | 1000 | V |

| Charged device model (CDM), per JEDEC specification JESD22-C101(2) | 250 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VIN | Input voltage | 3.9 | 17(1) | V |

| IIN | Input current | 3 | A | |

| ISYS | Output current (SYS) | 4.5 | A | |

| VBAT | Battery voltage | 4.4 | V | |

| IBAT | Fast charging current | 4.5 | A | |

| Discharging current with internal MOSFET | 6 (continuous) 9 (peak) (up to 1 sec duration) |

A | ||

| TA | Operating free-air temperature range | –40 | 85 | °C |

(1) The inherent switching noise voltage spikes should not exceed the absolute maximum rating on either the BTST or SW pins. A tight layout minimizes switching noise.

7.4 Thermal Information

| THERMAL METRIC(1) | bq24193 | UNIT | |

|---|---|---|---|

| RGE (24 PIN) | |||

| RθJA | Junction-to-ambient thermal resistance | 32.2 | °C/W |

| RθJCtop | Junction-to-case (top) thermal resistance | 29.8 | |

| RθJB | Junction-to-board thermal resistance | 9.1 | |

| ψJT | Junction-to-top characterization parameter | 0.3 | |

| ψJB | Junction-to-board characterization parameter | 9.1 | |

| RθJCbot | Junction-to-case (bottom) thermal resistance | 2.2 | |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

7.5 Electrical Characteristics

VVBUS_UVLOZ < VVBUS < VACOV and VVBUS > VBAT + VSLEEP, TJ = –40°C to 125°C and TJ = 25°C for typical values unless other noted.| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| QUIESCENT CURRENTS | ||||||

| IBAT | Battery discharge current (BAT, SW, SYS) | VVBUS < VUVLO, VBAT = 4.2 V, leakage between BAT and VBUS | 5 | µA | ||

| High-Z Mode, or no VBUS, BATFET disabled (REG07[5] = 1), | 12 | 20 | µA | |||

| High-Z Mode, or no VBUS, REG07[5] = 0, –40°C to 85°C | 32 | 55 | µA | |||

| IVBUS | Input supply current (VBUS) | VVBUS = 5 V, High-Z mode | 15 | 30 | µA | |

| VVBUS = 17 V, High-Z mode | 30 | 50 | µA | |||

| VVBUS > VUVLO, VVBUS > VBAT, converter not switching | 1.5 | 3 | mA | |||

| VVBUS > VUVLO, VVBUS > VBAT, converter switching, VBAT = 3.2 V, ISYS = 0 A | 4 | mA | ||||

| VVBUS > VUVLO, VVBUS > VBAT, converter switching, VBAT = 3.8 V, ISYS = 0 A | 15 | mA | ||||

| IOTGBOOST | Battery discharge current in boost mode | VBAT = 4.2 V, Boost mode, IVBUS = 0 A, converter switching | 4 | mA | ||

| VBUS/BAT POWER UP | ||||||

| VVBUS_OP | VBUS operating range | 3.9 | 17 | V | ||

| VVBUS_UVLOZ | VBUS for active I2C, no battery | VVBUS rising | 3.6 | V | ||

| VSLEEP | Sleep mode falling threshold | VVBUS falling, VVBUS-VBAT | 35 | 80 | 120 | mV |

| VSLEEPZ | Sleep mode rising threshold | VVBUS rising, VVBUS-VBAT | 170 | 250 | 350 | mV |

| VACOV | VBUS over-voltage rising threshold | VVBUS rising | 17.4 | 18 | V | |

| VACOV_HYST | VBUS over-voltage falling hysteresis | VVBUS falling | 700 | mV | ||

| VBAT_UVLOZ | Battery for active I2C, no VBUS | VBAT rising | 2.3 | V | ||

| VBAT_DPL | Battery depletion threshold | VBAT falling | 2.4 | 2.6 | V | |

| VBAT_DPL_HY | Battery depletion rising hysteresis | VBAT rising | 170 | 260 | mV | |

| VVBUSMIN | Bad adapter detection threshold | VVBUS falling | 3.8 | V | ||

| IBADSRC | Bad adapter detection current source | 30 | mA | |||

| tBADSRC | Bad source detection duration | 30 | ms | |||

| POWER PATH MANAGEMENT | ||||||

| VSYS_RANGE | Typical system regulation voltage | Isys = 0 A, Q4 off, VBAT up to 4.2 V, REG01[3:1] = 101, VSYSMIN = 3.5 V |

3.5 | 4.35 | V | |

| VSYS_MIN | System voltage output | REG01[3:1] = 101, VSYSMIN = 3.5 V | 3.55 | 3.65 | V | |

| RON(RBFET) | Internal top reverse blocking MOSFET on-resistance | Measured between VBUS and PMID | 23 | 38 | mΩ | |

| RON(HSFET) | Internal top switching MOSFET on-resistance between PMID and SW | TJ = –40°C to 85°C | 27 | 35 | mΩ | |

| TJ = -40°C to 125°C | 27 | 45 | ||||

| RON(LSFET) | Internal bottom switching MOSFET on-resistance between SW and PGND | TJ = –40°C to 85°C | 32 | 45 | mΩ | |

| TJ = -40°C to 125°C | 32 | 48 | ||||

| VFWD | BATFET forward voltage in supplement mode | BAT discharge current 10 mA | 30 | mV | ||

| VSYS_BAT | SYS/BAT Comparator | VSYS falling | 90 | mV | ||

| VBATGD | Battery good comparator rising threshold | VBAT rising | 3.4 | 3.55 | 3.7 | V |

| VBATGD_HYST | Battery good comparator falling threshold | VBAT falling | 100 | mV | ||

| BATTERY CHARGER | ||||||

| VBAT_REG_ACC | Charge voltage regulation accuracy | VBAT = 4.112 V and 4.208 V | –0.5% | 0.5% | ||

| IICHG_REG_ACC | Fast charge current regulation accuracy | VBAT = 3.8 V, ICHG = 1792 mA, TJ = 25°C | –4% | 4% | ||

| VBAT = 3.8 V, ICHG = 1792 mA, TJ = –20°C to 125°C | –7% | 7% | ||||

| ICHG_20pct | Charge current with 20% option on | VBAT = 3.1 V, ICHG = 104 mA, REG02 = 03 | 75 | 100 | 135 | mA |

| ICHG_20pct | Charge current with 20% option on | VBAT = 3.1 V, ICHG = 104 mA, REG02 = 03, at room temperature | 130 | mA | ||

| VBATLOWV | Battery LOWV falling threshold | Fast charge to precharge, REG04[1] = 1 | 2.6 | 2.8 | 2.9 | V |

| VBATLOWV_HYST | Battery LOWV rising threshold | Precharge to fast charge, REG04[1] = 1 | 2.8 | 3.0 | 3.1 | V |

| IPRECHG_ACC | Precharge current regulation accuracy | VBAT = 2.6 V, ICHG = 256 mA | –20% | 20% | ||

| ITERM_ACC | Termination current accuracy | ITERM = 256 mA, ICHG = 960 mA | –20% | 20% | ||

| VSHORT | Battery Short Voltage | VBAT falling | 2.0 | V | ||

| VSHORT_HYST | Battery Short Voltage hysteresis | VBAT rising | 200 | mV | ||

| ISHORT | Battery short current | VBAT < 2.2V | 100 | mA | ||

| VRECHG | Recharge threshold below VBAT_REG | VBAT falling, REG04[0] = 0 | 100 | mV | ||

| tRECHG | Recharge deglitch time | VBAT falling, REG04[0] = 0 | 20 | ms | ||

| RON_BATFET | SYS-BAT MOSFET on-resistance | TJ = 25°C | 12 | 15 | mΩ | |

| TJ = –40°C to 125°C | 12 | 20 | ||||

| INPUT VOLTAGE/CURRENT REGULATION | ||||||

| VINDPM_REG_ACC | Input voltage regulation accuracy | –2% | 2% | |||

| IUSB_DPM | USB Input current regulation limit, VBUS = 5 V, current pulled from SW | USB100 | 85 | 100 | mA | |

| USB150 | 125 | 150 | mA | |||

| USB500 | 440 | 500 | mA | |||

| USB900 | 750 | 900 | mA | |||

| IADPT_DPM | Input current regulation accuracy | Input current limit 1.5 A | 1.35 | 1.5 | 1.65 | A |

| IIN_START | Input current limit during system start up | VSYS < 2.2 V | 100 | mA | ||

| KILIM | IIN = KILIM/RILIM | IINDPM = 1.5 A | 435 | 485 | 530 | A x Ω |

| BAT OVER-VOLTAGE PROTECTION | ||||||

| VBATOVP | Battery over-voltage threshold | VBAT rising, as percentage of VBAT_REG | 104% | |||

| VBATOVP_HYST | Battery over-voltage hysteresis | VBAT falling, as percentage of VBAT_REG | 2% | |||

| tBATOVP | Battery over-voltage deglitch time to disable charge | 1 | µs | |||

| THERMAL REGULATION AND THERMAL SHUTDOWN | ||||||

| TJunction_REG | Junction temperature regulation accuracy | REG06[1:0] = 11 | 115(1) | 120 | 125(1) | °C |

| TSHUT | Thermal shutdown rising temperature | Temperature increasing | 160 | °C | ||

| TSHUT_HYS | Thermal shutdown hysteresis | 30 | °C | |||

| Thermal shutdown rising deglitch | Temperature increasing delay | 1 | ms | |||

| Thermal shutdown falling deglitch | Temperature decreasing delay | 1 | ms | |||

| JEITA THERMISTER COMPARATOR (bq24193) | ||||||

| VT1 | T1 (0°C) threshold, Charge suspended T1 below this temperature. | VTS rising, As percentage to VREGN | 70.2% | 70.8% | 71.4% | |

| VT1_HYS | Charge back to ICHG/2 and 4.2 V above this temperature | Hysteresis, VTS falling | 0.6% | |||

| VT2 | T2 (10°C) threshold, Charge back to ICHG/2 and 4.2 V below this temperature | VTS rising, as percentage of VREGN | 68.0% | 68.6% | 69.2% | |

| VT2_HYS | Charge back to ICHG and 4.2 V above this temperature | Hysteresis, VTS falling | 0.8% | |||

| VT3 | T3 (45°C) threshold, Charge back to ICHG and 4.05 V above this temperature | VTS falling, as percentage of VREGN | 55.5% | 56.1% | 56.7% | |

| VT3_HYS | Charge back to ICHG and 4.2 V below this temperature | Hysteresis, VTS rising | 0.8% | |||

| VT5 | T5 (60°C) threshold, charge suspended above this temperature | VTS falling, as percentage of VREGN | 47.6% | 48.1% | 48.6% | |

| VT5_HYS | Charge back to ICHG and 4.05 V below this temperature | Hysteresis, VTS rising | 1.2% | |||

| CHARGE OVER-CURRENT COMPARATOR | ||||||

| IHSFET_OCP | HSFET over-current threshold | 5.3 | 7 | A | ||

| IBATFET_OCP | System over load threshold | 9 | A | |||

| CHARGE UNDER-CURRENT COMPARATOR (CYCLE-BY-CYCLE) | ||||||

| VLSFET_UCP | LSFET charge under-current falling threshold | From sync mode to non-sync mode | 100 | mA | ||

| PWM OPERATION | ||||||

| FSW | PWM Switching frequency, and digital clock | 1300 | 1500 | 1700 | kHz | |

| DMAX | Maximum PWM duty cycle | 97% | ||||

| VBTST_REFRESH | Bootstrap refresh comparator threshold | VBTST-VSW when LSFET refresh pulse is requested, VBUS = 5 V | 3.6 | V | ||

| VBTST-VSW when LSFET refresh pulse is requested, VBUS > 6 V | 4.5 | |||||

| BOOST MODE OPERATION | ||||||

| VOTG_REG | OTG output voltage | I(VBUS) = 0 | 5.00 | V | ||

| VOTG_REG_ACC | OTG output voltage accuracy | I(VBUS) = 0 | –2% | 2% | ||

| IOTG | OTG mode output current | REG01[0] = 0 | 0.5 | A | ||

| REG01[0] = 1 | 1.3 | A | ||||

| IOTG_HSZCP | HSFET under current falling threshold | 100 | mA | |||

| IRBFET_OCP | RBFET over-current threshold | REG01[0] = 1 | 1.4 | 1.8 | 2.7 | A |

| REG01[0] = 0 | 0.6 | 1.1 | 1.8 | |||

| REGN LDO | ||||||

| VREGN | REGN LDO output voltage | VVBUS = 10 V, IREGN = 40 mA | 5.6 | 6 | 6.4 | V |

| VVBUS = 5 V, IREGN = 20 mA | 4.75 | 4.8 | 5 | V | ||

| IREGN | REGN LDO current limit | VVBUS = 10 V, VREGN = 3.8 V | 50 | mA | ||

| LOGIC I/O PIN CHARACTERISTICS (OTG, CE, PSEL, STAT, PG) | ||||||

| VILO | Input low threshold | 0.4 | V | |||

| VIH | Input high threshold | 1.3 | V | |||

| VOUT_LO | Output low saturation voltage | Sink current = 5 mA | 0.4 | V | ||

| IBIAS | High level leakage current | Pull up rail 1.8 V | 1 | µA | ||

| I2C INTERFACE (SDA, SCL, INT) | ||||||

| VIH | Input high threshold level | VPULL-UP = 1.8 V, SDA and SCL | 1.3 | V | ||

| VIL | Input low threshold level | VPULL-UP = 1.8 V, SDA and SCL | 0.4 | V | ||

| VOL | Output low threshold level | Sink current = 5 mA | 0.4 | V | ||

| IBIAS | High-level leakage current | VPULL-UP = 1.8 V, SDA and SCL | 1 | µA | ||

| fSCL | SCL clock frequency | 400 | kHz | |||

| DIGITAL CLOCK AND WATCHDOG TIMER | ||||||

| fHIZ | Digital crude clock | REGN LDO disabled | 15 | 35 | 50 | kHz |

| fDIG | Digital clock | REGN LDO enabled | 1300 | 1500 | 1700 | kHz |

| tWDT | REG05[5:4] = 11 | REGN LDO enabled | 136 | 160 | sec | |

(1) Not production tested

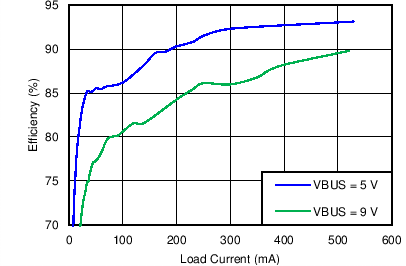

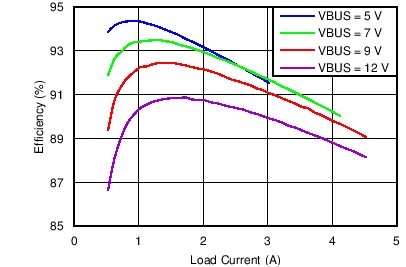

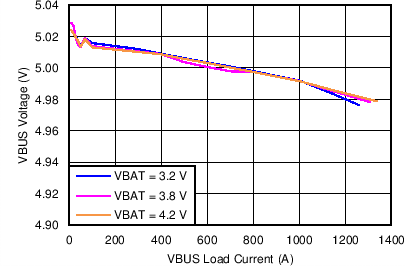

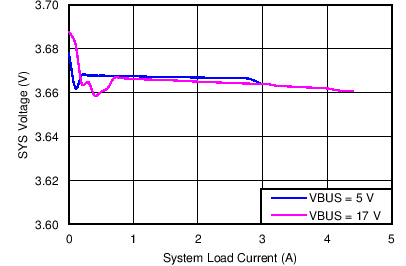

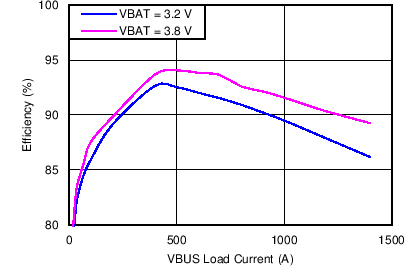

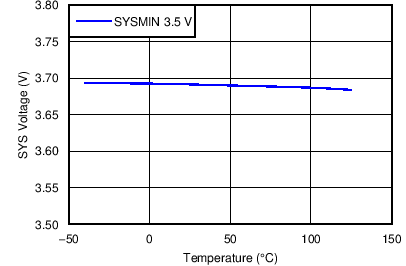

7.6 Typical Characteristics

Table 1. Table of Figures

| FIGURE NUMBER | |

|---|---|

| System Light Load Efficiency vs System Load Current | Figure 1 |

| SYS Voltage Regulation vs System Load | Figure 2 |

| Charging Efficiency vs Charging Current | Figure 3 |

| Boost Mode Efficiency vs VBUS Load Current | Figure 4 |

| Boost Mode VBUS Voltage Regulation vs VBUS Load Current | Figure 5 |

| SYS Voltage vs Temperature | Figure 6 |

| BAT Voltage vs Temperature | Figure 7 |

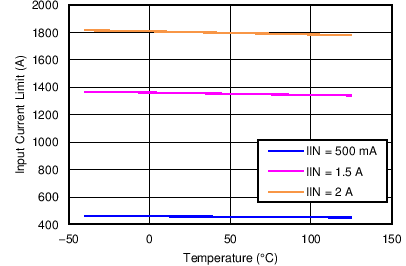

| Input Current Limit vs temperature | Figure 8 |

| Charge Current vs temperature | Figure 9 |