SLUSA91C October 2010 – October 2015

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics: Supply Current

- 6.6 Power-On Reset (POR)

- 6.7 Wake From Sleep

- 6.8 RBI RAM Backup

- 6.9 3.3-V Regulator

- 6.10 2.5-V Regulator

- 6.11 PRES, SMBD, SMBC

- 6.12 CHG, DSG FET Drive

- 6.13 PCHG FET Drive

- 6.14 FUSE

- 6.15 Coulomb Counter

- 6.16 VC1, VC2, VC3, VC4

- 6.17 TS1, TS2

- 6.18 Internal Temperature Sensor

- 6.19 Internal Thermal Shutdown

- 6.20 High-Frequency Oscillator

- 6.21 Low-Frequency Oscillator

- 6.22 Internal Voltage Reference

- 6.23 Flash

- 6.24 OCD Current Protection

- 6.25 SCD1 Current Protection

- 6.26 SCD2 Current Protection

- 6.27 SCC Current Protection

- 6.28 SBS Timing Requirements

- 6.29 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

11 Layout

11.1 Layout Guidelines

The predominant layout concern for the bq3055 is related to the coulomb counter measurement. The external components and PCB layout surrounding the SRP and SRN pins should be carefully considered.

11.2 Layout Example

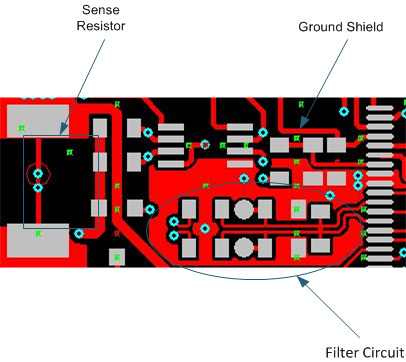

As shown in Figure 24, a differential filter must precede the current sense inputs of the gas gauge. This filter eliminates the effect of unwanted digital noise, which can cause offset in the measured current. Even the best differential amplifier has less common-mode rejection at high frequencies. Without a filter, the amplifier input stage may rectify a strong RF signal, which then may appear as a DC-offset error.

Five percent tolerance of the components is adequate, because capacitor C15 shunts C12 and C13 and reduces AC common mode arising from a component mismatch. It is important to locate C15 as close as possible to the gas gauge pins. The other components also must be relatively close to the IC. The ground connection of C12 and C13 must be close to the IC. It is also proven to reduce offset and noise error by maintaining a symmetrical placement pattern and adding ground shielding for the differential filter network.

Figure 24. PCB Layout Example

Figure 24. PCB Layout Example