JAJSNV5G February 1998 – October 2022 CD54HC73 , CD74HC73 , CD74HCT73

PRODUCTION DATA

- 1 特長

- 2 概要

- 3 Revision History

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Power Supply Recommendations

- 9 Layout

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- J|14

サーマルパッド・メカニカル・データ

発注情報

2 概要

’HC73 および CD74HCT73 は、LSTTL 製品に匹敵する動作速度を達成するためにシリコン・ゲート CMOS 技術を採用しています。これらのデバイスは、標準 CMOS IC の低消費電力と、10 個の LSTTL 負荷に耐える駆動能力とを合わせ持っています。

パッケージ情報

| 部品番号 | パッケージ (1) | 本体サイズ (公称) |

|---|---|---|

| CD74HC73M | SOIC (14) | 8.65mm × 3.90mm |

| CD74HCT73M | SOIC (14) | 8.65mm × 3.90mm |

| CD74HC73E | PDIP (14) | 19.31mm × 6.35mm |

| CD74HCT73E | PDIP (14) | 19.31mm × 6.35mm |

| CD54HC73F | CDIP (14) | 19.55mm × 6.71mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

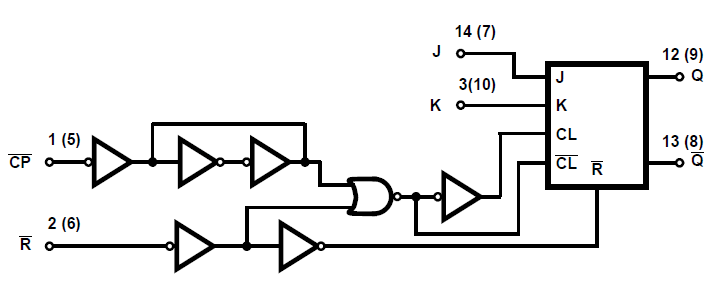

機能ブロック図

機能ブロック図