JAJSE83D April 2016 – December 2017 DAC60004 , DAC70004 , DAC80004

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

11 Layout

11.1 Layout Guidelines

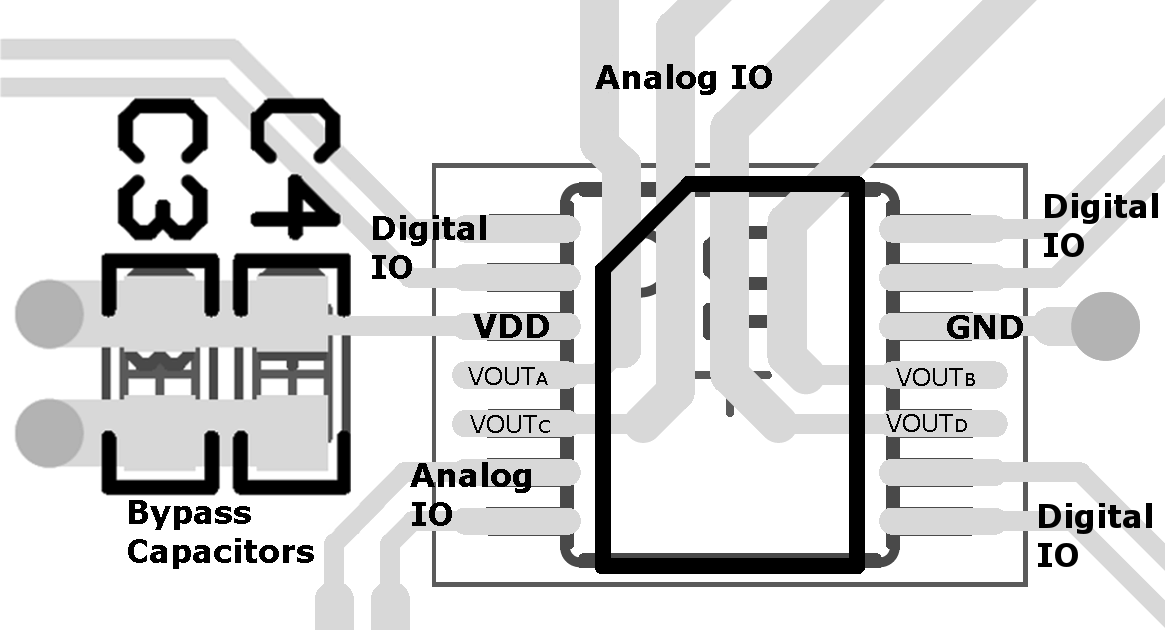

A precision analog component requires careful layout, adequate bypassing, and clean, well-regulated power supplies. As a general rule it is important to keep digital traces as far away from analog traces when possible.

The DACx0004 is often used in close proximity with digital logic, microcontrollers, microprocessors, and digital signal processors. The more digital logic present in the design and the higher the switching speed, the more difficult it is to keep digital noise from appearing at the output.

Due to the single ground pin of the DACx0004, all return currents, including digital and analog return currents for the DAC, must flow through a single point. Ideally, GND must be connected directly to an analog ground plane. This plane must be separate from the ground connection for the digital components until they were connected at the power-entry point of the system.

As with the GND connection, VDD should be connected to a 5 V power-supply plane or trace that is separate from the connection for digital logic until they are connected at the power-entry point. It is recommended to have an additional 1 μF to 10 μF capacitor and 0.1 μF bypass capacitor. In some situations, additional bypassing may be required, such as a 100 μF electrolytic capacitor or even a Pi filter made up of inductors and capacitors—all designed to essentially low-pass filter the 5 V supply, removing the high-frequency noise. In general it is always a good idea to maintain the digital signals away from analog signals.

11.2 Layout Example

Figure 60. Layout Diagram

Figure 60. Layout Diagram