JAJSEF2D June 2013 – December 2021 DAC7760 , DAC8760

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

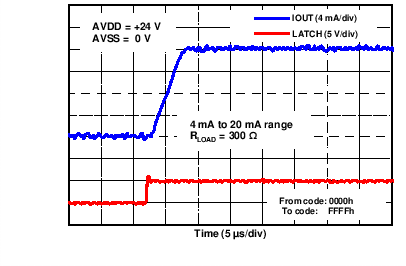

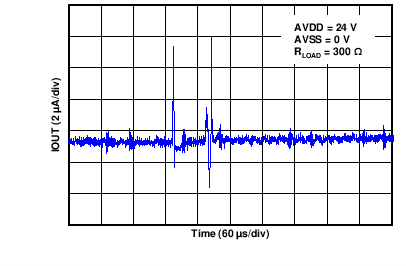

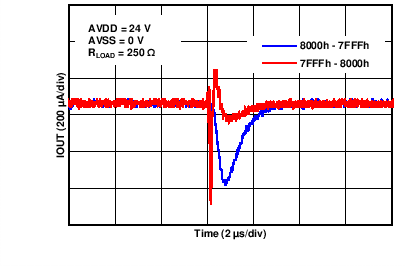

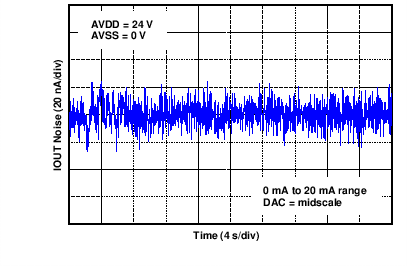

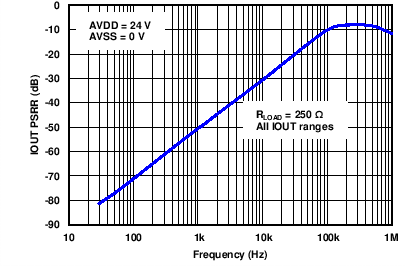

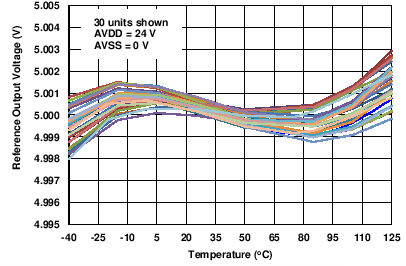

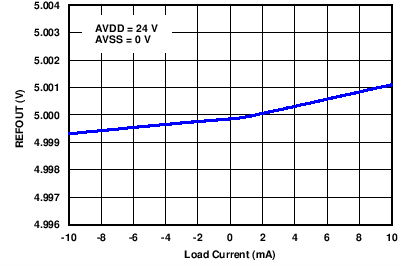

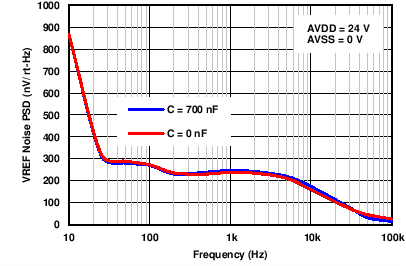

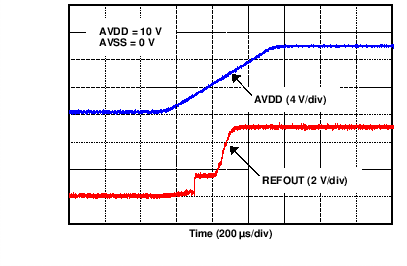

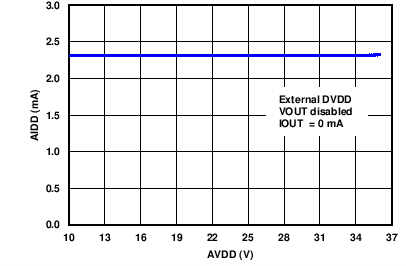

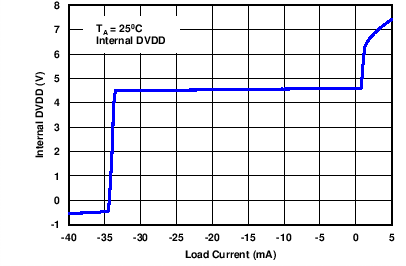

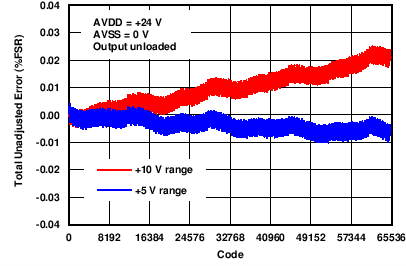

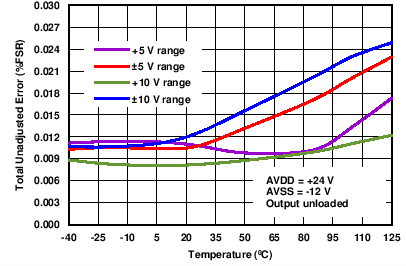

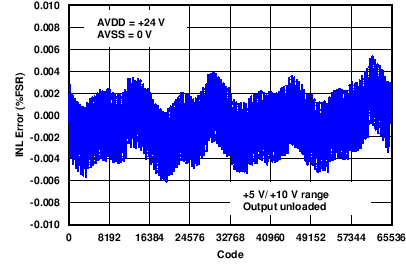

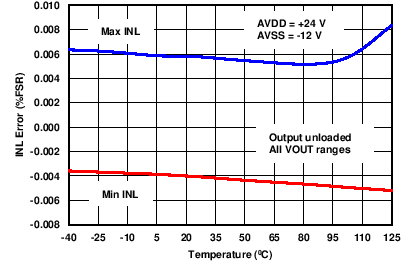

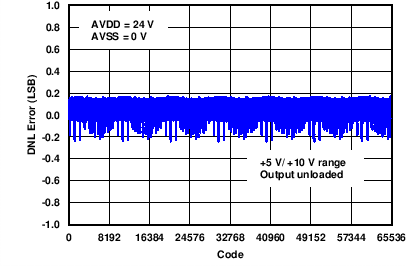

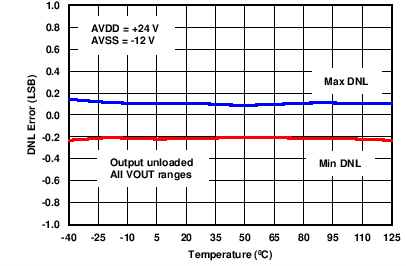

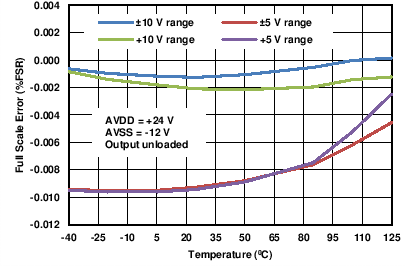

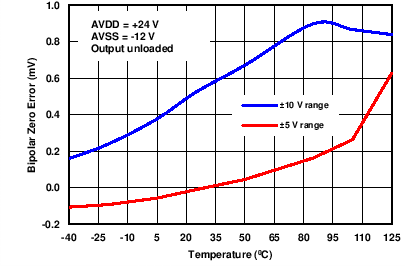

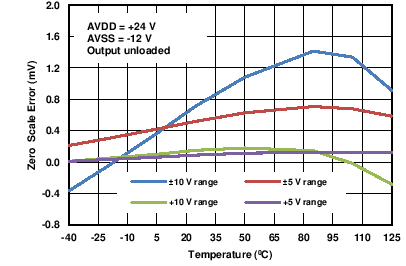

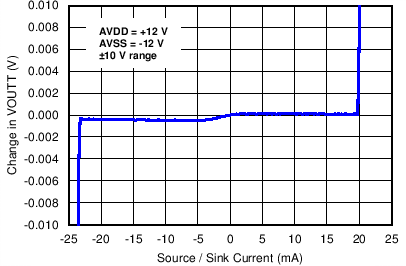

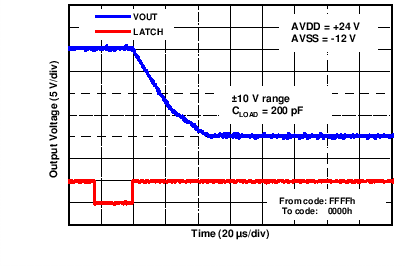

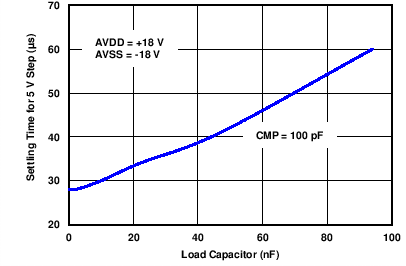

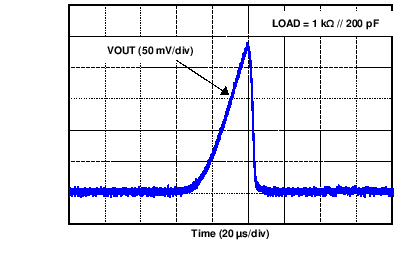

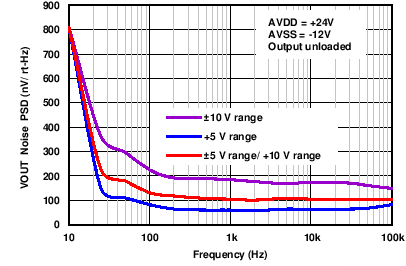

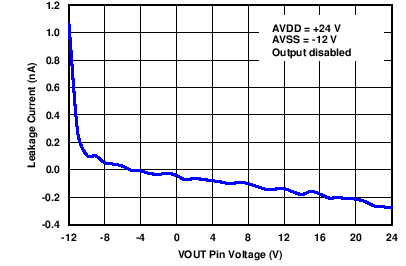

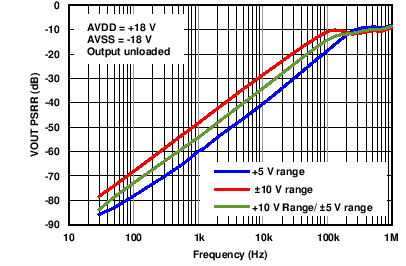

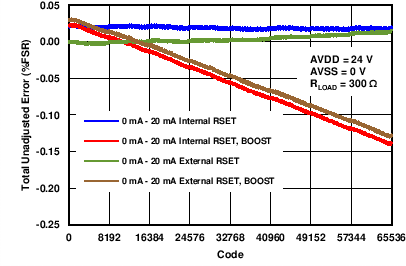

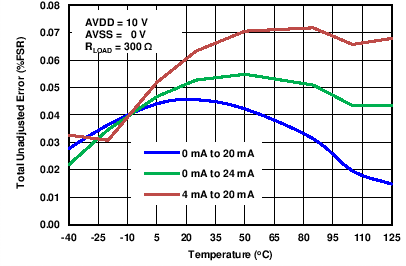

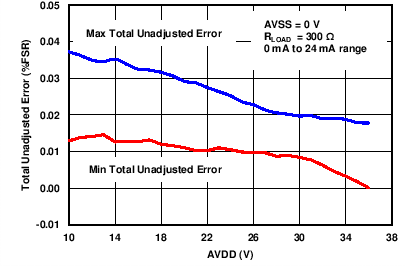

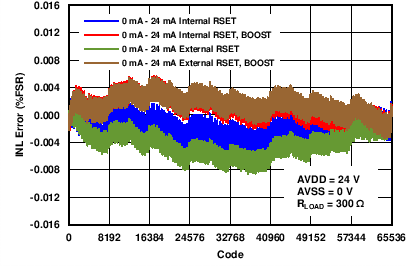

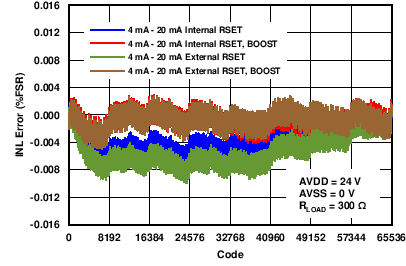

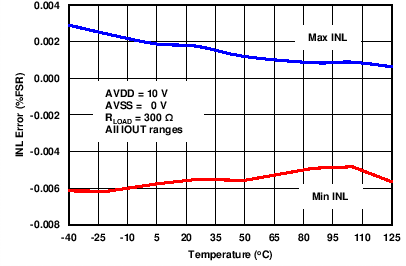

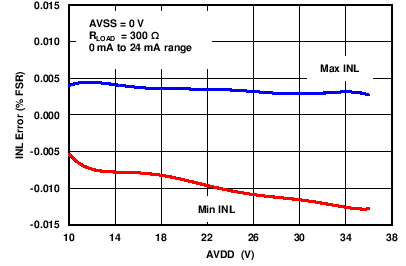

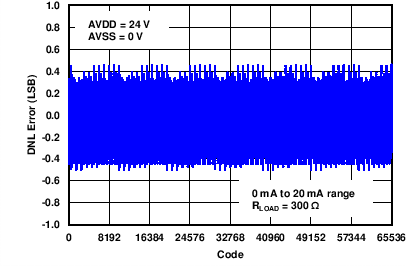

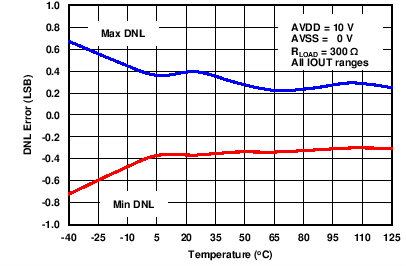

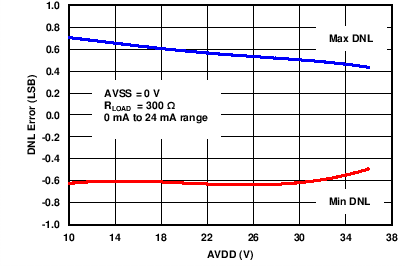

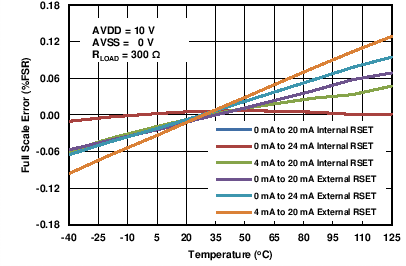

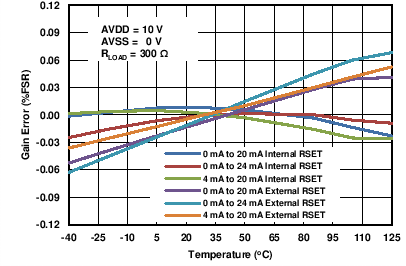

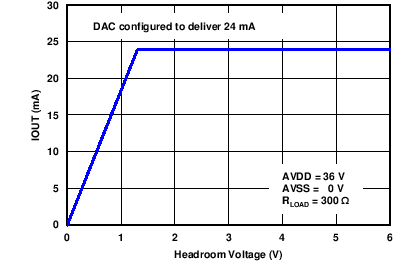

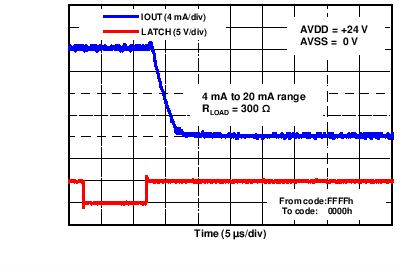

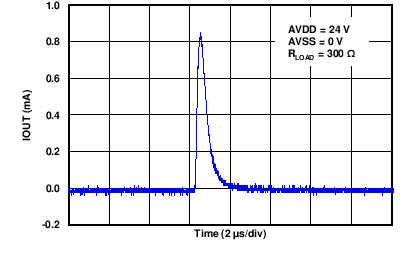

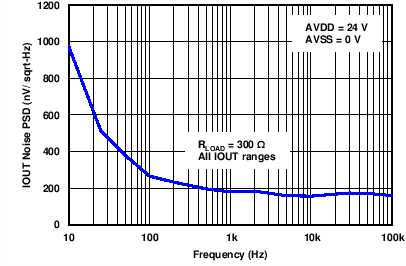

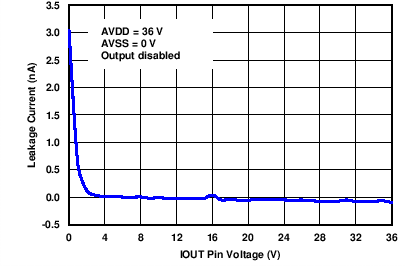

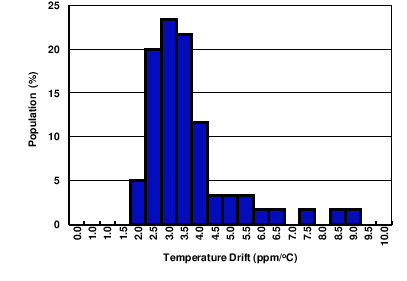

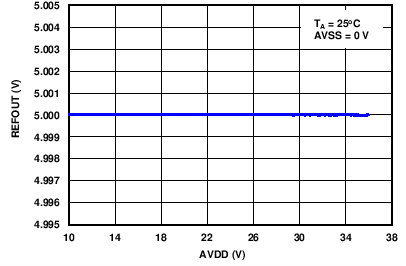

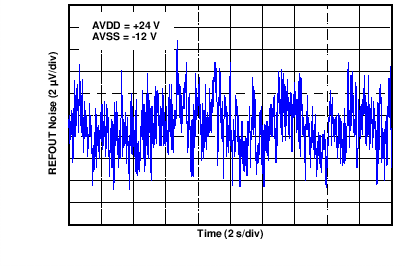

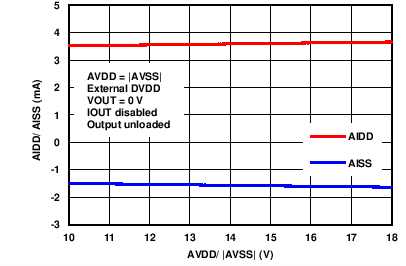

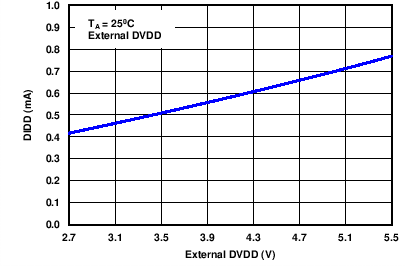

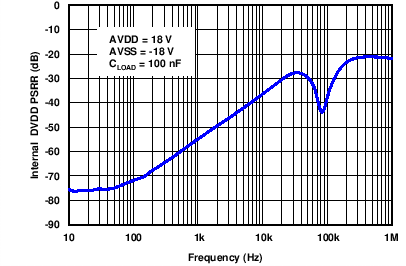

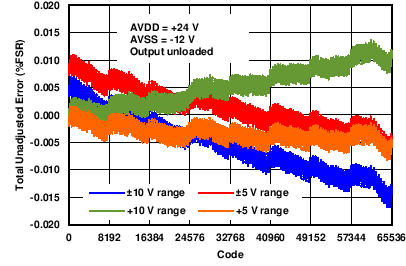

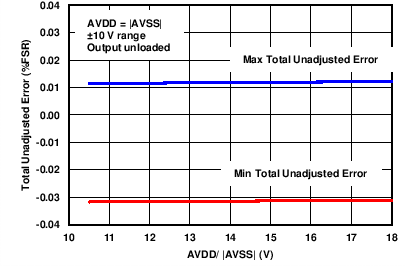

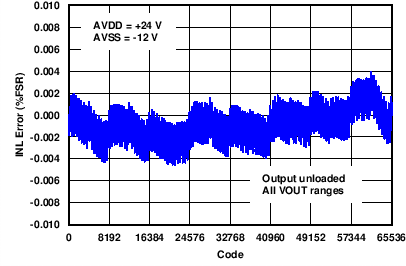

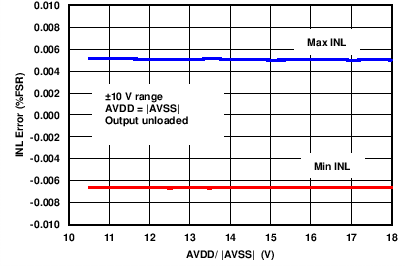

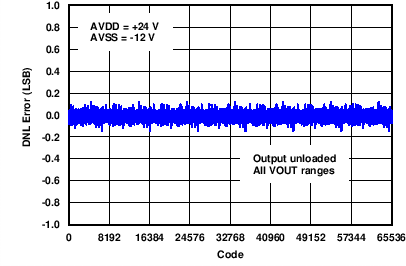

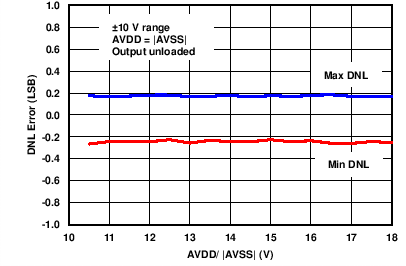

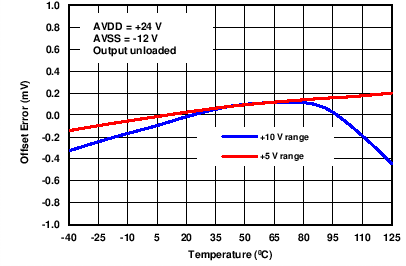

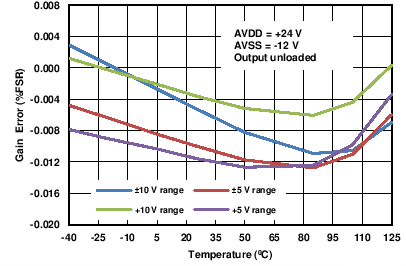

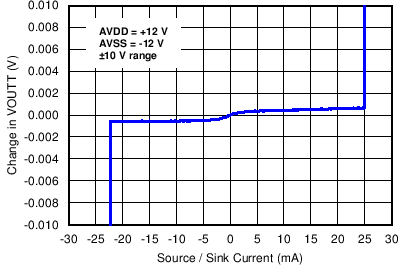

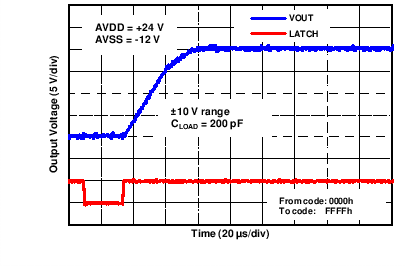

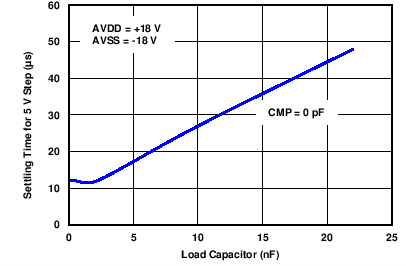

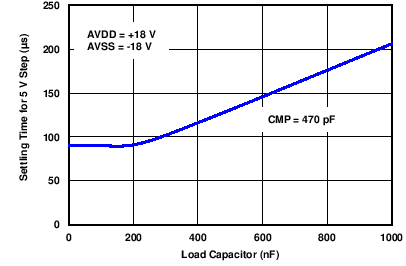

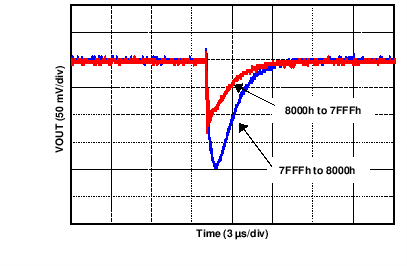

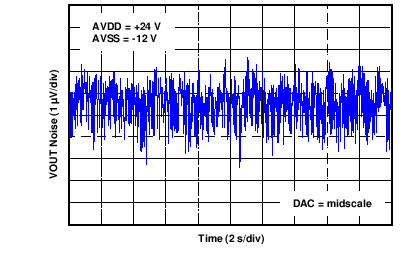

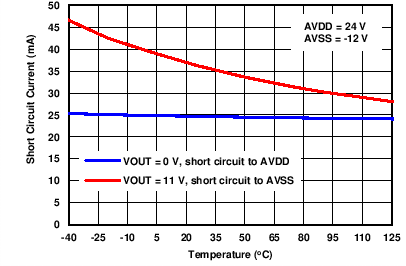

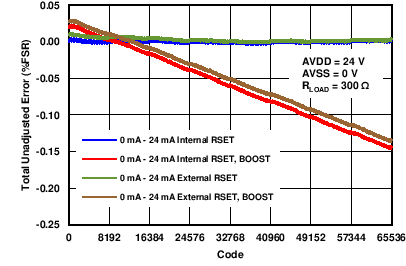

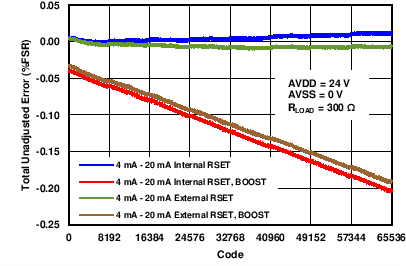

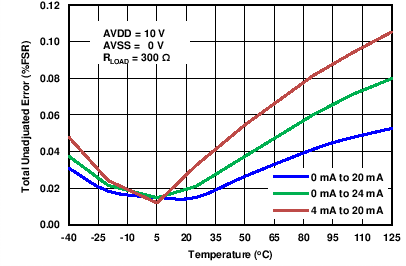

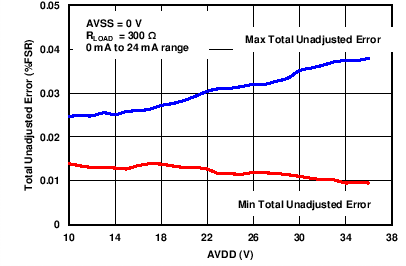

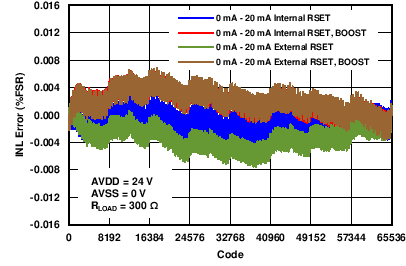

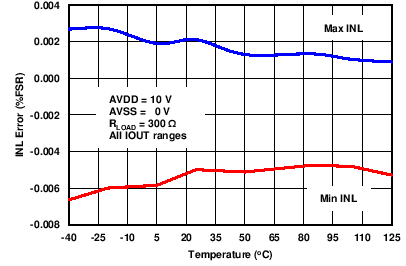

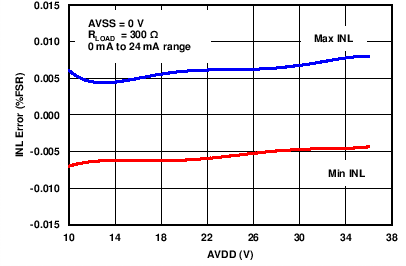

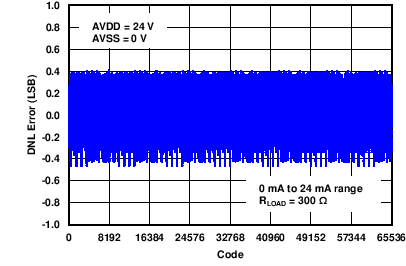

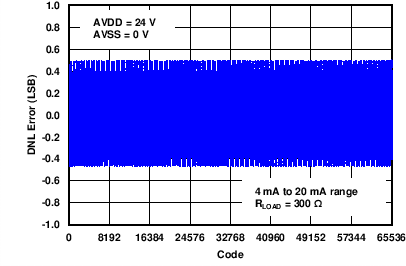

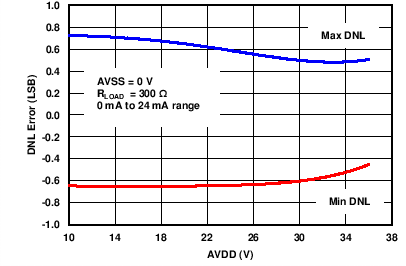

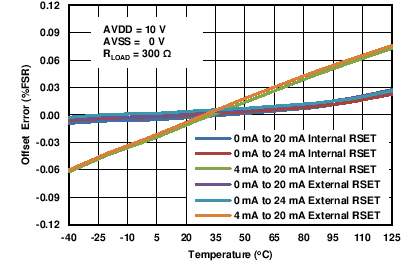

7.10 Typical Characteristics

at TA = 25°C (unless otherwise noted)

(Source or Sink)

(100 pF Between VOUT and CMP Pins)

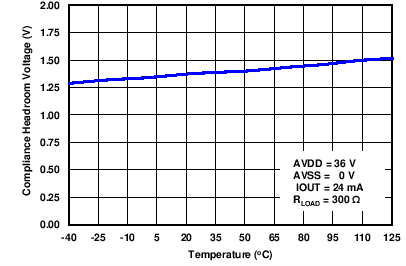

| Compliance voltage headroom is defined as the drop from AVDD pin to the IOUT pin. |

(0.1 Hz to 10 Hz)

(No Compensation Capacitor)

(470 pF Between VOUT and CMP Pins)

| Compliance voltage headroom is defined as the drop from AVDD pin to the IOUT pin. |