DLPS082 February 2017 DLPA100

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- DLP|48

サーマルパッド・メカニカル・データ

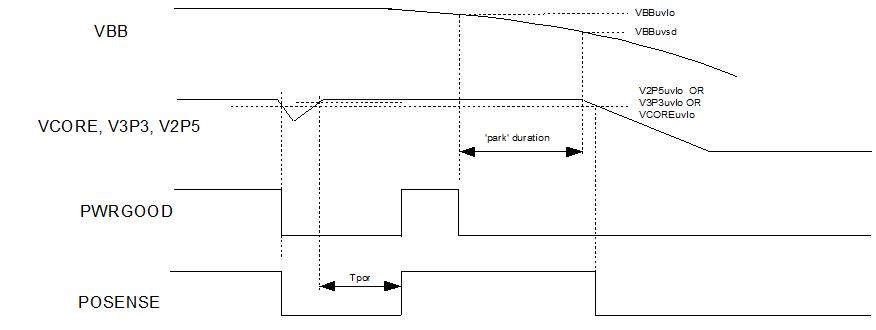

7.3.2 Power Down Sequencing

If VBB drops below the undervoltage level (VBBuvlo), the PWRGOOD will flag. If VBB drops below the undervoltage level (VBBuvsd), all the switcher and linear channels will turn off and the output rails will be supplied by the output filter capacitors. The duration between VBBuvlo and VBBuvsd allows sufficient ‘hold up’ time to ‘park’ the DMD mirrors. Although the regulators can supply rated current down to VBBuvsd, they can only provide this power for a maximum of 0.5 ms.

If either of the rails: VCORE or V3P3 or V2P5 drop below their respective undervoltage levels, the POSENSE and PWRGOOD will flag immediately.

Figure 2. Power Down Sequencing Timing Diagram

Figure 2. Power Down Sequencing Timing Diagram