JAJSM06A December 2021 – February 2023 DLPC4430

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 System Oscillators Timing Requirements

- 6.7 Test and Reset Timing Requirements

- 6.8 JTAG Interface: I/O Boundary Scan Application Timing Requirements

- 6.9 Port 1 Input Pixel Timing Requirements

- 6.10 Port 3 Input Pixel Interface (via GPIO) Timing Requirements

- 6.11 DMD LVDS Interface Timing Requirements

- 6.12 Synchronous Serial Port (SSP) Interface Timing Requirements

- 6.13 Programmable Output Clocks Switching Characteristics

- 6.14 Synchronous Serial Port Interface (SSP) Switching Characteristics

- 6.15 JTAG Interface: I/O Boundary Scan Application Switching Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

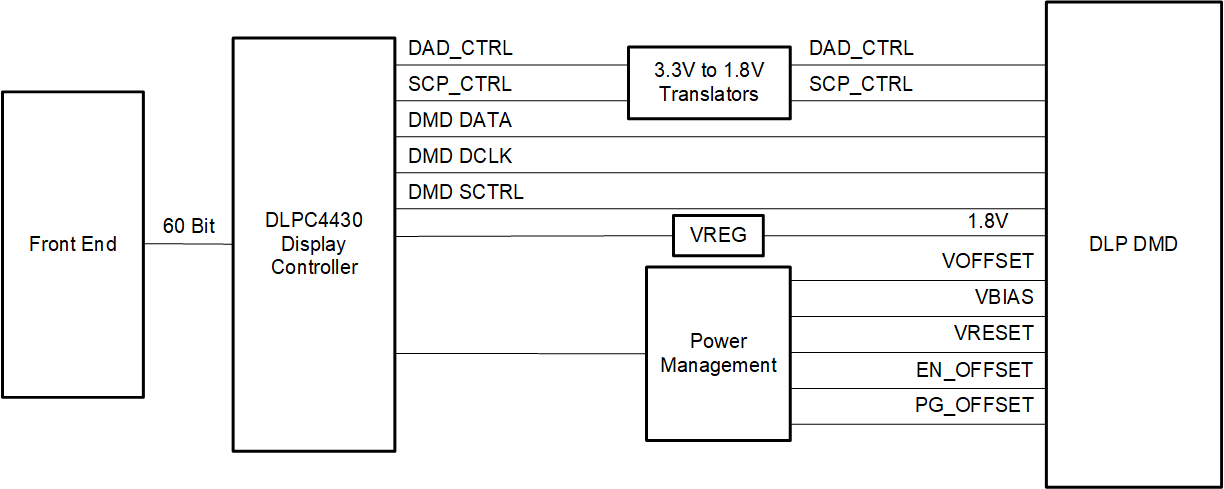

3 概要

DLPC4430 は、DLP® ディスプレイ・チップセット用のデジタル・ディスプレイ・コントローラです。このチップセットは、DLPC4430 ディスプレイ・コントローラ、DLP デジタル・マイクロミラー・デバイス (DMD)、DLPA100 コントローラ・パワー・マネージメント・デバイス、DLPA300 DMD マイクロミラー・ドライバで構成されます (DMD データシートを参照)。このソリューションは、簡素なシステムで高解像度と高輝度を必要とするディスプレイ・システムに最適です。信頼性の高い動作を保証するため、DLPC4430 ディスプレイ・コントローラは、DLP DMD および対応する DLP パワー・マネージメント・デバイスと常に一緒に使う必要があります。

デバイス情報

| 部品番号(1) | パッケージ | 本体サイズ (公称) |

|---|---|---|

| DLPC4430 | ZPC (516) | 27.00mm × 27.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

簡略回路図

簡略回路図