JAJSCS8B December 2016 – November 2018 INA1650 , INA1651

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Applications

- 8.2.1 Line Receiver for Differential Audio Signals in a Split-Supply System

- 8.2.2 Differential Line Receiver for Single-Supply Applications

- 8.2.3 Floating Single-Ended Input Line Receiver for Ground Loop Noise Reduction

- 8.2.4 Floating Single-Ended Input Line Receiver With Differential Outputs

- 8.2.5 TRS Audio Interface in Single-Supply Applications

- 8.2.6 Differential Line Driver With Single-Ended Input

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

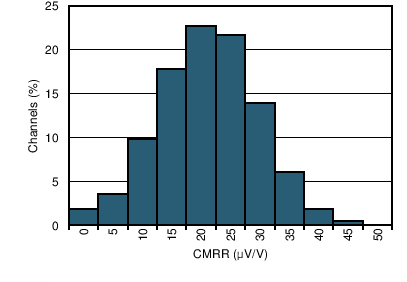

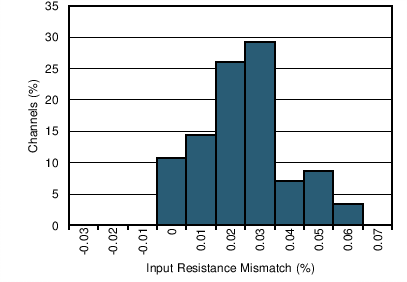

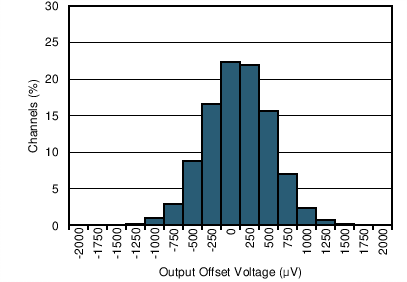

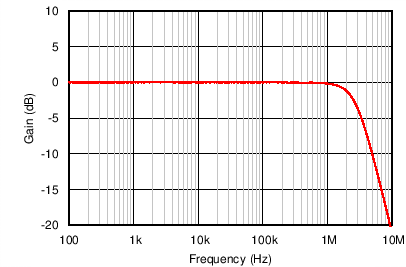

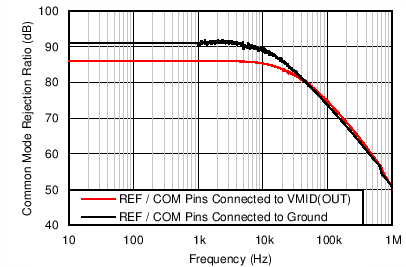

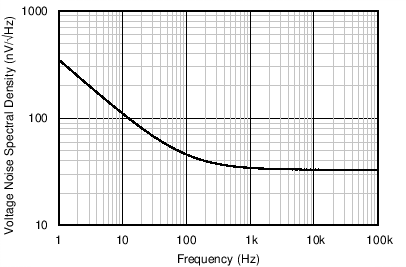

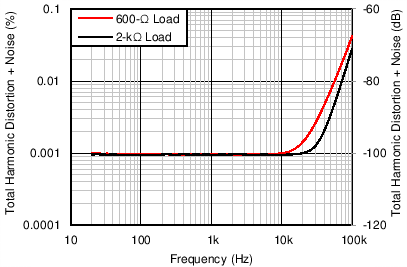

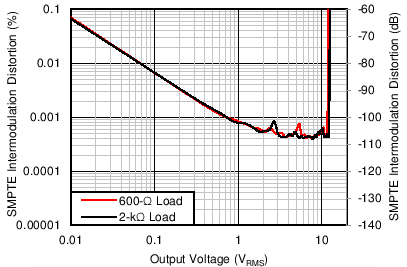

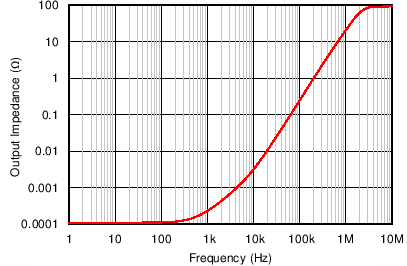

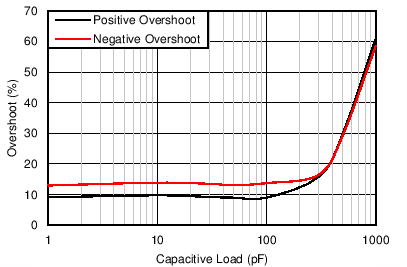

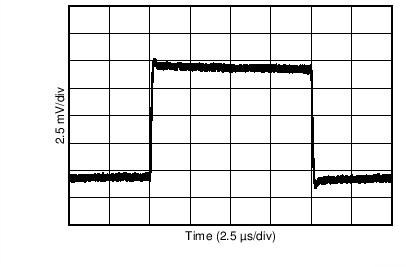

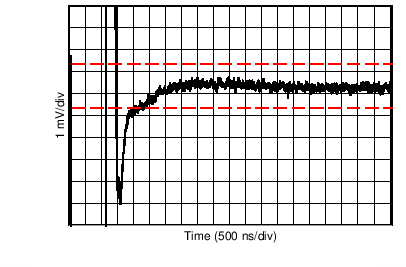

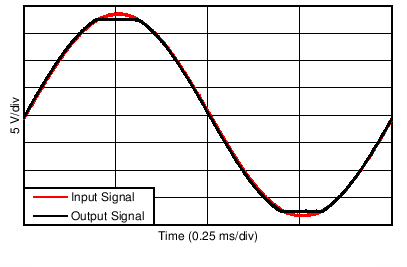

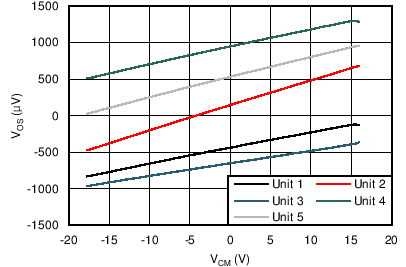

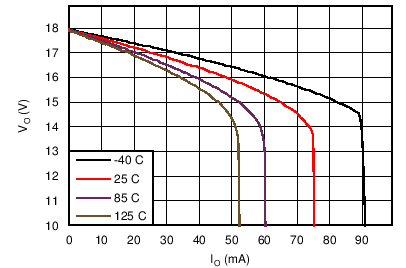

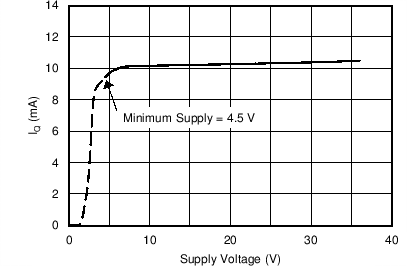

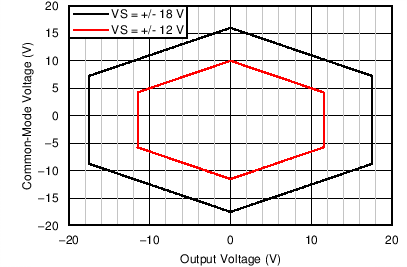

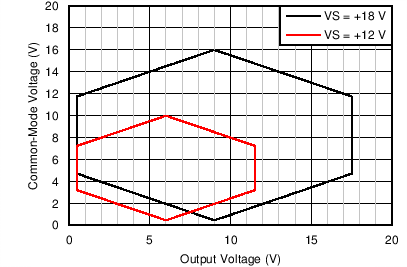

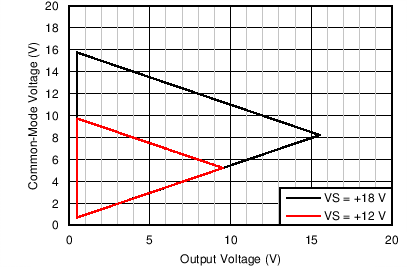

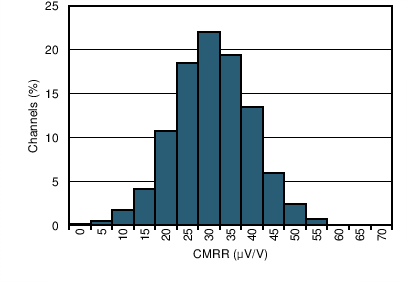

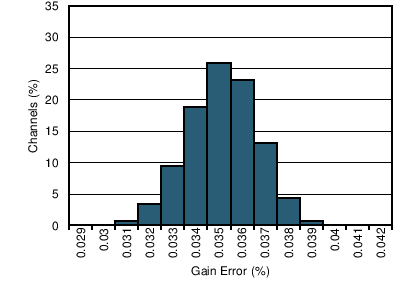

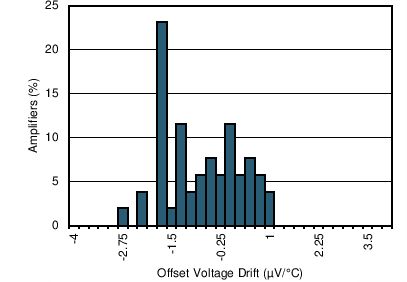

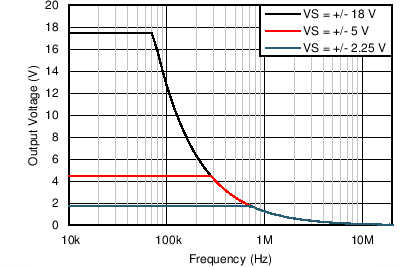

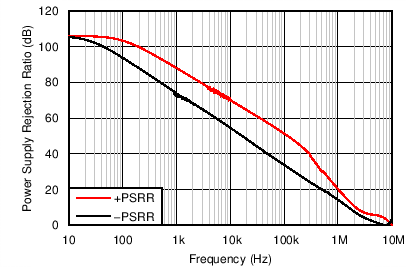

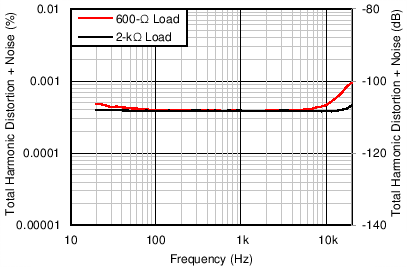

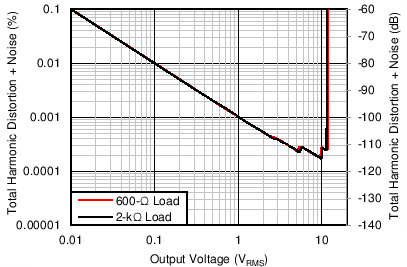

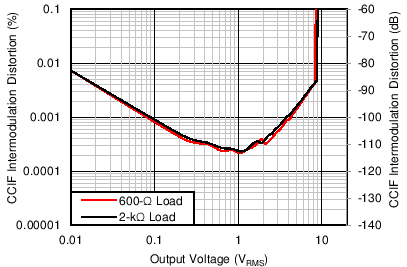

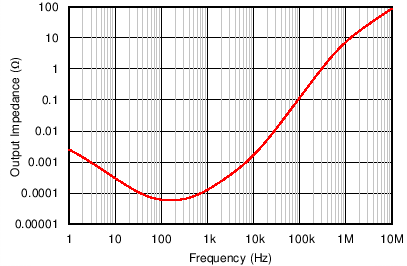

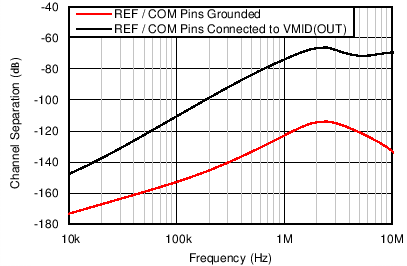

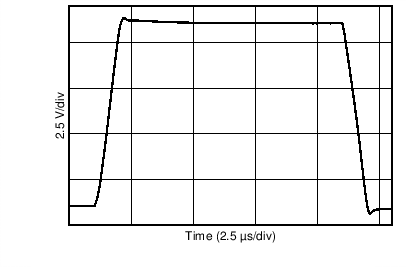

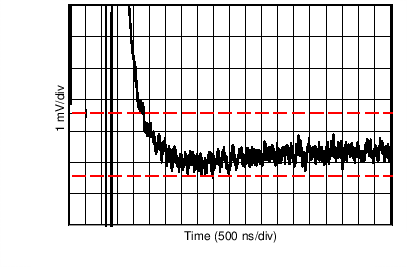

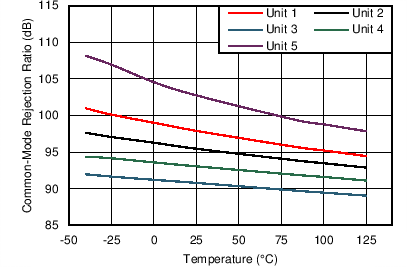

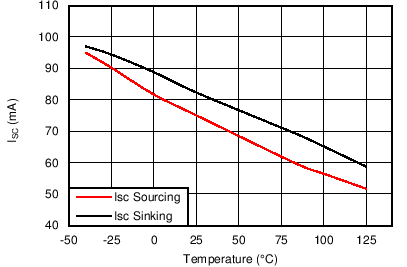

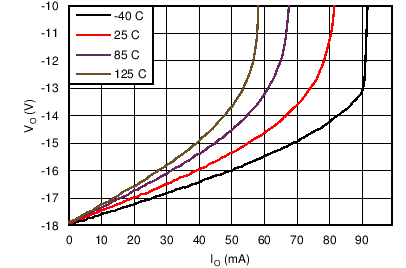

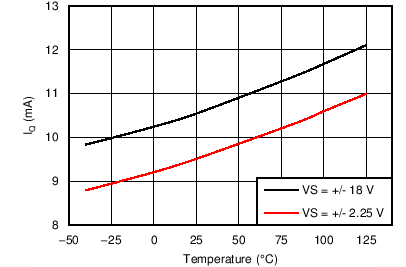

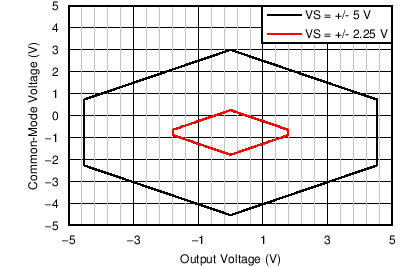

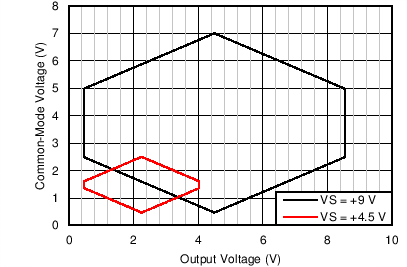

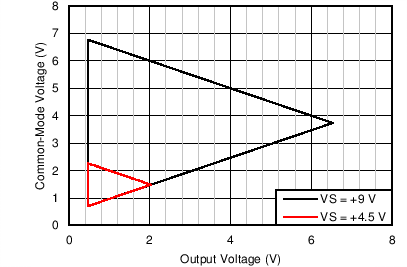

6.6 Typical Characteristics

at TA = 25°C, VS = ±18 V, VCM = VOUT = midsupply, and RL = 2 kΩ (unless otherwise noted)

| 5746 Channels |

| VREF Pins Connected to Ground |

| 5746 Channels |

| 5746 Channels |

| 3 VRMS, 500-kHz Measurement Bandwidth |

| SMPTE 4:1 60 Hz and 7 kHz, 90-kHz Measurement Bandwidth |

| 100-mV Input Step |

| 10-mV Input Step |

| 10-V Input Step, 0.01% Settling = ± 1 mV |

| 5 Typical Units |

| REF A/B connected to 0 V |

| REF A/B connected to VMID(OUT) |

| REF A/B connected to 0 V |

| 5746 Channels |

| VREF Pins Connected to VMID(OUT) |

| 5746 Channels |

| 52 Channels |

| 3 VRMS, 90-kHz Measurement Bandwidth |

| 1 kHz, 90-kHz Measurement Bandwidth |

| CCIF 19 kHz and 20 kHz, 90-kHz Measurement Bandwidth |

| CF = 1 µF |

| 10-V Input Step |

| 10-V Input Step, 0.01% Settling = ± 1 mV |

| 5 Typical Units |

| REF A/B connected to 0 V |

| REF A/B connected to VMID(OUT) |

| REF A/B connected to 0 V |