JAJSL65 February 2023 LM5148-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 概要 (続き)

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Input Voltage Range (VIN)

- 8.3.2 High-Voltage Bias Supply Regulator (VCC, VCCX, VDDA)

- 8.3.3 Precision Enable (EN)

- 8.3.4 Power-Good Monitor (PG)

- 8.3.5 Switching Frequency (RT)

- 8.3.6 Dual Random Spread Spectrum (DRSS)

- 8.3.7 Soft Start

- 8.3.8 Output Voltage Setpoint (FB)

- 8.3.9 Minimum Controllable On Time

- 8.3.10 Error Amplifier and PWM Comparator (FB, EXTCOMP)

- 8.3.11 Slope Compensation

- 8.3.12 Inductor Current Sense (ISNS+, VOUT)

- 8.3.13 Hiccup Mode Current Limiting

- 8.3.14 High-Side and Low-Side Gate Drivers (HO, LO)

- 8.3.15 Output Configurations (CNFG)

- 8.3.16 Single-Output Dual-Phase Operation

- 8.4 Device Functional Modes

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1

Design 1 – High Efficiency 2.1-MHz Synchronous

Buck Regulator

- 9.2.1.1 Design Requirements

- 9.2.1.2

Detailed Design Procedure

- 9.2.1.2.1 Custom Design with WEBENCH® Tools

- 9.2.1.2.2 Custom Design with Excel Quickstart Tool

- 9.2.1.2.3 Buck Inductor

- 9.2.1.2.4 Current-Sense Resistance

- 9.2.1.2.5 Output Capacitors

- 9.2.1.2.6 Input Capacitors

- 9.2.1.2.7 Frequency Set Resistor

- 9.2.1.2.8 Feedback Resistors

- 9.2.1.2.9 Compensation Components

- 9.2.1.3 Application Curves

- 9.2.2 Design 2 – High Efficiency 48-V to 12-V 400-kHz Synchronous Buck Regulator

- 9.2.3 Design 3 – High Efficiency 440-kHz Synchronous Buck Regulator

- 9.2.4 Design 4 – Dual-Phase 400-kHz 20-A Synchronous Buck Regulator

- 9.2.1

Design 1 – High Efficiency 2.1-MHz Synchronous

Buck Regulator

- 9.3 Power Supply Recommendations

- 9.4 Layout

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

3 概要

LM5148-Q1 は、大電流、単一出力アプリケーション用の 80V、超低静止電流 (IQ) の同期整流式降圧 DC/DC コントローラです。本コントローラはピーク電流モード制御アーキテクチャを採用しているため、ループ補償が簡単で、過渡応答が高速であり、負荷およびライン・レギュレーションが非常に優れています。LM5148-Q1 は、大電流アプリケーション向けに、高精度の電流共有が可能なデュアル同相モード (並列出力) に設定できます。最低 3.5V の入力電圧、必要に応じてほぼ 100% のデューティ・サイクルで動作できます。

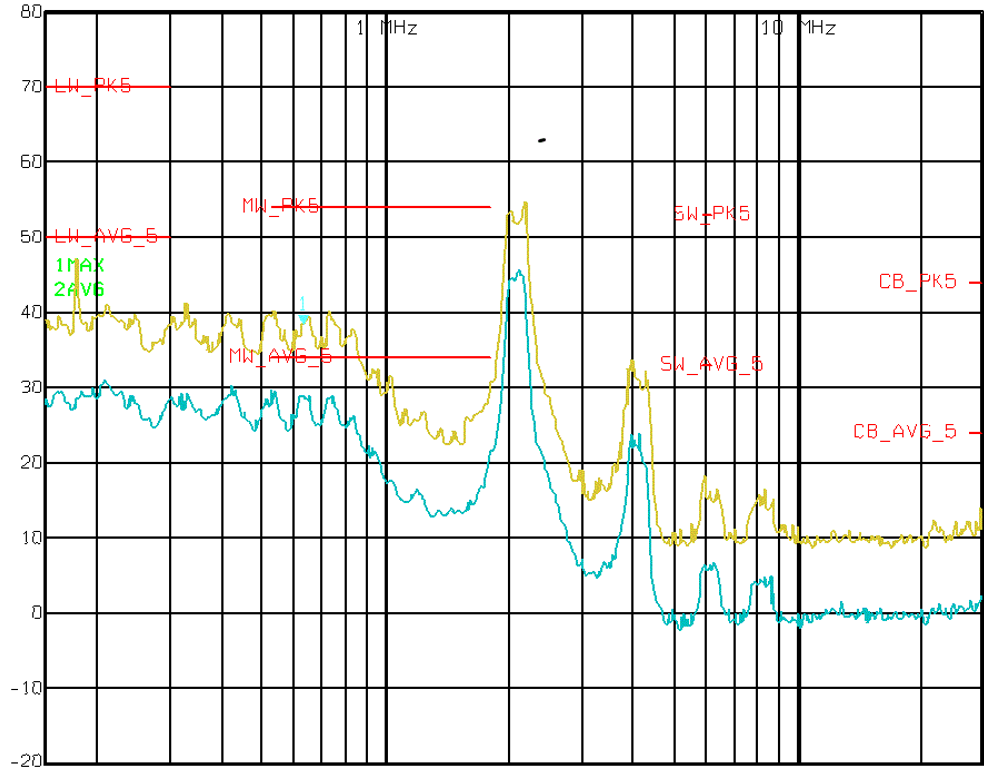

LM5148-Q1 にはデュアル・ランダム拡散スペクトラム (DRSS) と呼ばれる独自の EMI 削減機能を備えています。低周波数の三角波変調と高周波数のランダム変調を組み合わせると、低周波数帯域から高周波数帯域にわたり EMI 障害がそれぞれ緩和されます。このハイブリッド手法は、業界標準の EMC テストで規定されている複数分解能帯域幅 (RBW) 設定に適合します。

パッケージ情報

| 部品番号 | パッケージ (1) | 本体サイズ (公称) |

|---|---|---|

| LM5148-Q1 | RGY (VQFN、24) | 3.50mm × 5.50mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

代表的なアプリケーション回路図

代表的なアプリケーション回路図 CISPR 25 EMI 性能 (150kHz~30MHz)

CISPR 25 EMI 性能 (150kHz~30MHz)