JAJSE52B November 2017 – May 2021 LM73605-Q1 , LM73606-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Synchronous Step-Down Regulator

- 8.3.2 Auto Mode and FPWM Mode

- 8.3.3 Fixed-Frequency Peak Current-Mode Control

- 8.3.4 Adjustable Output Voltage

- 8.3.5 Enable and UVLO

- 8.3.6 Internal LDO, VCC_UVLO, and BIAS Input

- 8.3.7 Soft Start and Voltage Tracking

- 8.3.8 Adjustable Switching Frequency

- 8.3.9 Frequency Synchronization and Mode Setting

- 8.3.10 Internal Compensation and CFF

- 8.3.11 Bootstrap Capacitor and VBOOT-UVLO

- 8.3.12 Power-Good and Overvoltage Protection

- 8.3.13 Overcurrent and Short-Circuit Protection

- 8.3.14 Thermal Shutdown

- 8.4 Device Functional Modes

- 9 Layout

- 10Device and Documentation Support

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RNP|30

サーマルパッド・メカニカル・データ

- RNP|30

発注情報

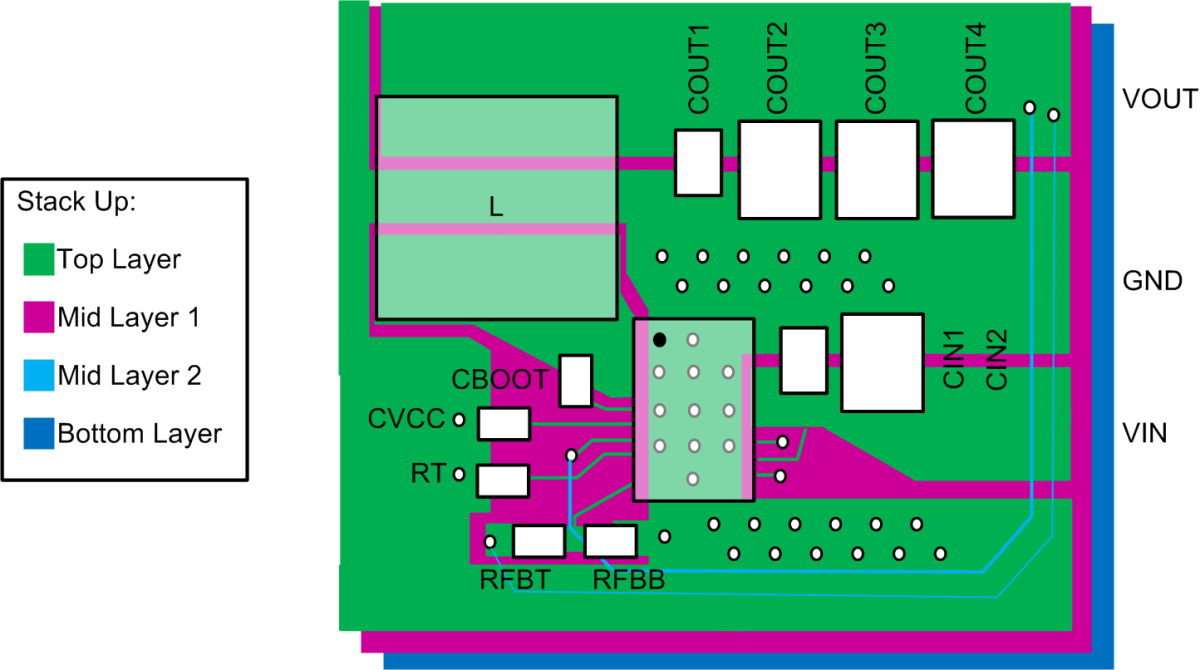

9.2 Layout Example

A layout example is shown in Figure 9-3. A four-layer board is used with 2-oz copper on the top and bottom layers and 1-oz copper on the inner two layers. Figure 9-3 shows the relative scale of the LM73605-Q1/6-Q1 with 0805 and 1210 input and output capacitors, 7-mm × 7-mm inductor and 0603 case size for all other passive components. The trace width of the signal connections are not to scale.

The components are placed on the top layer and the high current paths are routed on the top layer as well. The remaining space on the top layer can be filled with GND polygon. Thermal vias are used under the DAP and around the device. The GND copper was extended to the outside of the device, which serves as copper heat sink.

The mid-layer 1 is right underneath the top layer. It is a solid ground plane, which serves as noise shielding and heat dissipation path.

The VOUT sense trace is routed on the third layer, which is mid-layer 2. Ground plane provided noise shielding for the sense trace. The VOUT to BIAS connection is routed by a separate trace.

The bottom layer is also a solid ground copper in this example. Solid copper provides best heat sinking for the device. If components and traces need to be on the bottom layer, leave the area around thermal vias as solid as possible. Try not to cut heat dissipation path by a trace. The board can be used for various frequencies and output voltages, with component variation. For more details, see the LM73605/LM73606 EVM User's Guide.

Figure 9-3 LM73605-Q1/6-Q1 Layout Example

Figure 9-3 LM73605-Q1/6-Q1 Layout Example