SNOSDI3 March 2024 LMG3425R030

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 GaN FET Operation Definitions

- 7.3.2 Direct-Drive GaN Architecture

- 7.3.3 Drain-Source Voltage Capability

- 7.3.4 Internal Buck-Boost DC-DC Converter

- 7.3.5 VDD Bias Supply

- 7.3.6 Auxiliary LDO

- 7.3.7 Fault Protection

- 7.3.8 Drive-Strength Adjustment

- 7.3.9 Temperature-Sensing Output

- 7.3.10 Ideal-Diode Mode Operation

- 7.4 Start-Up Sequence

- 7.5 Device Functional Modes

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, and Orderable Information

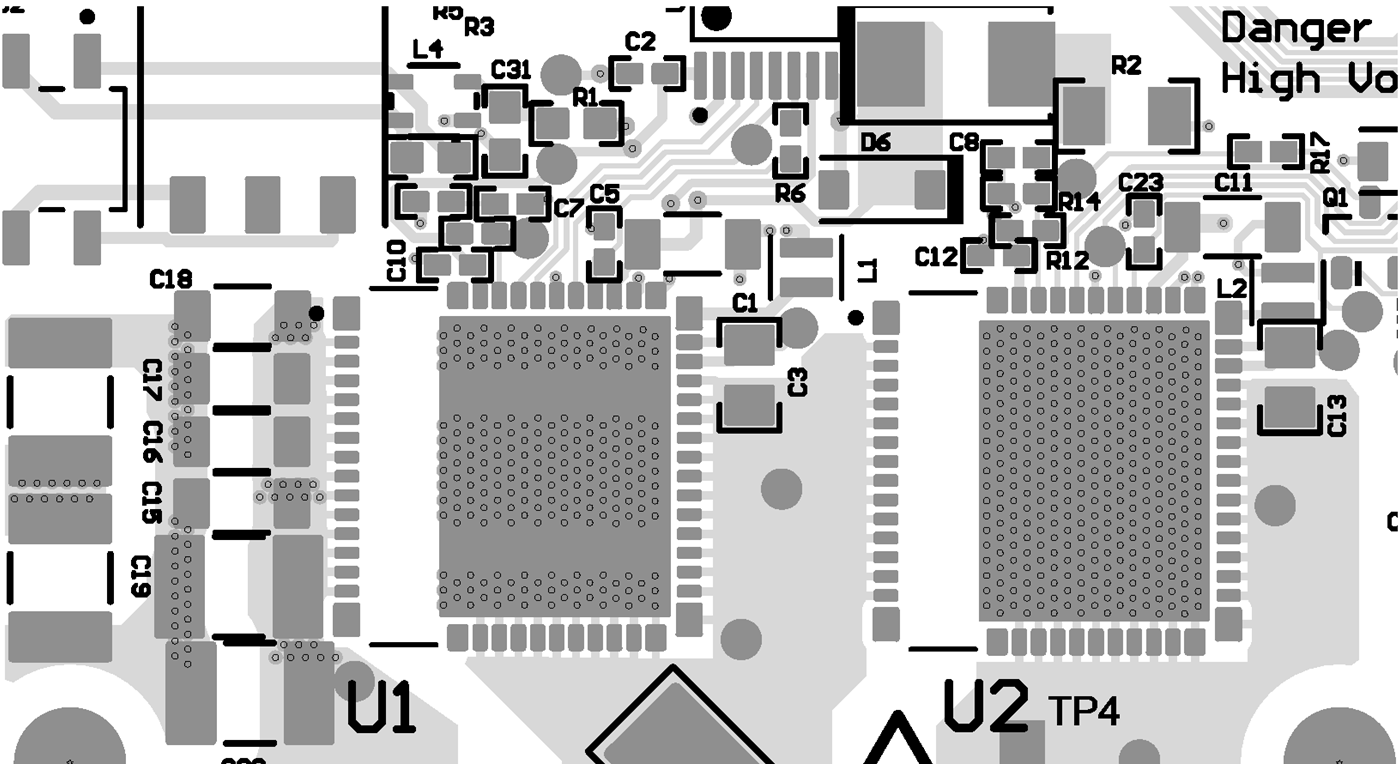

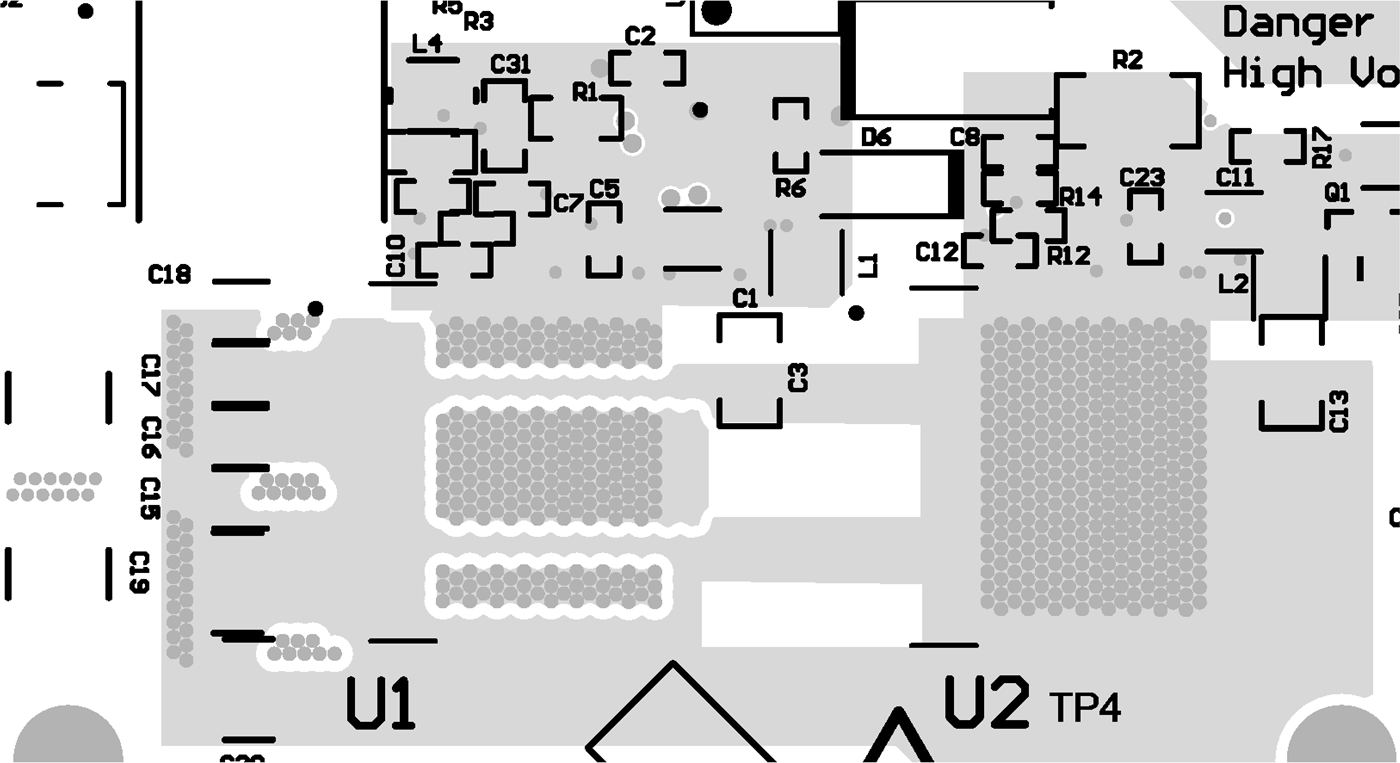

8.5.2 Layout Examples

Correct layout of the LMG3425R030 and its surrounding components is essential for correct operation. The layouts shown here reflect the GaN device schematic in Figure 8-1. These layouts are shown to produce good results and is intended as a guideline. However, it can be possible to obtain acceptable performance with alternate layout schemes. Additionally, please refer to the land pattern example in Mechanical, Packaging, and Orderable Information for the latest recommended PCB footprint of the device.

The the top-layer layout and mid-layer layout are shown. The layouts are zoomed in to the LMG3425R030 U1 and U2 component placements. The mid-layer layout includes the outlines of the top level components to assist the reader in lining up the top-layer and mid-layer layouts. Figure 8-10 Half-Bridge

Top-Layer Layout

Figure 8-10 Half-Bridge

Top-Layer Layout Figure 8-11 Half-Bridge

Mid-Layer Layout

Figure 8-11 Half-Bridge

Mid-Layer Layout